Есть несколько событий и тем, которыми я хотел бы поделиться с сообществом.

По-хорошему, под каждого можно написать отдельную статью, но общая нехватка времени вынуждает немного схитрить.

Наши темы сегодня:

- Выпуск MIPSfpga 2.0;

- процессор schoolMIPS и Летняя школа юных программистов в Новосибирске;

- школа-семинар по цифровому дизайну и компьютерной архитектуре в Томске;

- запуск ванильного ядра Linux на MIPSfpga-plus;

- поддержка АЦП Altera MAX10 в MIPSfpga-plus;

- Логотип MIPSfpga-plus.

Ваш выбор поможет мне сориентироваться и расставить приоритеты.

Добро пожаловать !

Выпуск MIPSfpga 2.0

Спустя 2 года после первого выпуска MIPSfpga компания Imagination Technologies выпустила вторую версию пакета: MIPSfpga 2.0 [ Л1 ].На что нужно обратить внимание:

- Как и прежде, MIPSfpga представлена не только как открытый исходный код ядра промышленного процессора под академической лицензией, но и как набор учебных материалов, включающий в себя также документацию и лабораторные работы.

И это здорово, ведь в комплекте идет недавно переведенная на русский язык книга «Цифровая схемотехника и компьютерная архитектура» (H&H).

Л2 ] получаем очень качественный и доступный набор теории и практики, изложенный на примере архитектуры MIPS;

- на недавнем симпозиуме в Торонто [ Л3 ] Сара Харрис (один из авторов H&H) представила коллективную статью [ Л14 ], где дано достаточно подробное описание MIPSfpga 2.0, а также анализ распространения образовательной инициативы Imagination Technologies по университетам.

И (вау!) там даже упоминается мое имя в связи с моей деятельностью в проекте MIPSfpga-plus. - если первый релиз был в основном ориентирован на то, как собрать систему на кристалле (SoC) на базе MIPSfpga, то второй релиз сместил акцент именно на работу самого процессора:

6 Расширьте систему, чтобы добавить счетчик 7 Расширьте систему, чтобы добавить зуммер.

8. Расширьте систему, добавив датчик SPI-Light. 9 Расширьте систему, добавив SPI-LCD. 10 Взаимодействие с периферийными устройствами с помощью прерываний 11. Создайте механизм DMA для передачи данных между периферийными устройствами.

12. Создайте механизм стандарта шифрования данных (DES).

13 Узнайте, как использовать счетчики производительности 14 Выполнение ADD и других арифметических инструкций 15 Выполнение AND и других логических инструкций 16 Выполнение LW и других связанных с ним инструкций 17 Выполнение BEQ и других связанных инструкций 18 Узнайте, как реализован блок рисков 19 Узнайте, как использовать интерфейс CorExtend 20 Знакомство с кэшами, доступными в MIPSfpga 21. Анализ D$ и внедрение новых конфигураций 22 Контроллер кэша: анализ попадания и промаха в кэше 23 Контроллер кэша: анализ политик управления D$ 24 Контроллер кэша: анализ хранилища и заполнение буферов 25. Реализация инструкции.

Блокнот оперативной памяти.

- Само ядро, по предварительной информации, особых изменений не претерпело, это все тот же MIPS microAptiv UP, на базе которого построен, например, микрочип PIC32MZ;

- Акцент на Xilinx при создании SoC в лабораторных работах также остался неизменным.

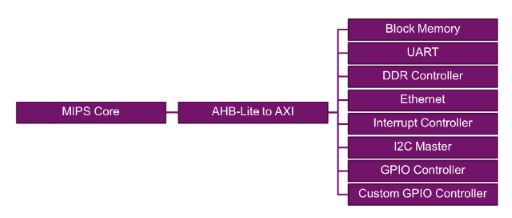

Таким образом, общая схема используемой в лабораторных работах SoC выглядит следующим образом, что несколько ограничивает запуск на платах на базе Altera:

Но здесь нам на помощь приходит MIPSfpga-plus — opensource-проект по построению SoC на базе MIPSfpga с платформонезависимой периферией[ Л4 ].

Для корректного взаимодействия с MIPSfpga 2.0, возможно, потребуется немного модифицировать его.

schoolMIPS и Летняя школа молодых программистов

Летняя школа молодых программистов открылась сегодня в Новосибирске.Л5 ].

Школьная программа разделена на мастер-классы [ Л6 ], один из которых посвящен обучению Verilog и архитектуре микросхем.

Воспитателем детей станет Юрий Панчул.

ЮрийПанчул , прилетевший из Штатов специально по этому делу.

Мастерская чип-архитекторов Мастер: Юрий Панчул Цифровое оборудование, от логических элементов до собственного процессора Хотите знать, как устроены чипы в современных устройствах — от телефонов до космических кораблей? Последние 25 лет это делается с использованием методологии синтеза логического кода на языках описания аппаратуры.

Именно эту технологию мы будем изучать в нашей мастерской и использовать для проектирования собственных устройств.

Мы начнем с трех ключевых строительных блоков цифровой электроники — логического элемента, тактового сигнала и D-триггера, памяти для одного бита информации.

Для наглядности будем осваивать их по старинке, соединяя микросхемы с низкой степенью интеграции проводами на макетной плате.

Затем повторим построенные схемы на языке описания аппаратуры SystemVerilog и смоделируем их с помощью программы-симулятора.

Но как мы можем превратить их в чипсы? Ведь заказывать коммерческий чип с завода — это очень дорого? К счастью, существуют «перестраиваемые» программируемые логические интегральные схемы (FPGA), платы, которые мы будем использовать на наших занятиях.

Помимо упражнений с арифметическими блоками и конечными автоматами, мы попробуем построить простой процессор, аналогичный по микроархитектуре процессору Mongoose-V внутри космического корабля New Horizons, который год назад пролетел мимо Плутона.

Заодно изучим немного программирование на языке ассемблера, понятие прерываний, сравним наш процессор с промышленными микроконтроллерами и встраиваемыми микропроцессорами, вплоть до микропроцессора EyeQ5 для беспилотного автомобиля, выпуск которого запланирован на 2020 год. Это круто, и я, честно говоря, немного завидую этим школьникам – в моем детстве такого не было.

Специально к этому событию мы написали небольшой процессор с архитектурой MIPS: schoolMIPS [ Л7 ], которую планируется использовать в образовательном процессе.

Он создан путем упрощения процессора Сары Харрис, описанного в H&H [ Л2 ].

Ключевая особенность:

- язык описания оборудования Verilog;

- подмножество архитектуры MIPS с памятью инструкций, с регистрами общего назначения, но без памяти данных;

- однотактная микроархитектура;

- минимальный набор инструкций, изначально достаточный для итеративного вычисления числа Фибоначчи и целого квадратного корня;

- микроархитектура и код максимально упрощены для целей обучения;

- Компиляция программы осуществляется с помощью инструментальной цепочки MIPS.

Помимо написания процессора, был осуществлен достаточно масштабный перевод различных учебных материалов на русский язык.

Я не буду касаться этой темы, потому что.

не участвовал, полагаю, что Юрий ЮрийПанчул Подробнее об этом напишем в будущем.

Школа-семинар по цифровому дизайну и компьютерной архитектуре в Томске

С 18 по 22 сентября в Томском государственном университете пройдет Школа-семинар «Цифровой дизайн и компьютерная архитектура в эпоху систем на кристалле (SoC) и интернет-технологий (IoT).Предварительная программа школы и список участников опубликованы на сайте [ Л8 ].

Там же выступит ваш покорный слуга: я планирую рассказать об AHB-Lite, подключении периферии к MIPSfpga, работе с SDRAM — это со сцены.

А неформально мы можем обсудить Linux, подключив отладчик и любой код, который я принес на MIPSfpga-plus. Приходить!

Запуск Linux на MIPSfpga-plus

Лаборатории MIPSfpga описывают запуск Linux на SoC, построенном с использованием периферийных модулей, специфичных для Xilinx. Вкупе с уже упомянутой выше проблемой доступа к платам это создавало некоторые трудности.Минимум, необходимый для запуска ОС Linux: MMU (доступен как часть MIPS fpga), достаточный объем памяти и UART. При этом большая часть работы по портированию системы уже выполнена компанией Imagination Technologies, соответствующий код включен в основную ветку ядра [ Л9 ].

Буквально неделю назад мне удалось запустить Linux на Terasic DE10-Lite и не скажу, что необходимый для этого патч оказался очень сложным.

Ключевая особенность:

- конфигурация системы: FPGA Altera MAX10, SDRAM 64MB, MIPSfpga-plus, UART16550;

- Ядро загружается в память с помощью EJTAG[ Л10 ];

- mmc/sdcard пока не поддерживаются, поэтому о загрузке с карты памяти говорить не приходится.

С другой стороны, в лабораторной работе MIPSfpga о загрузке с флешки речи не идет.

В ближайшее время я планирую подготовить небольшой HOWTO о том, как воспроизвести эти результаты.Linux version 4.12.2+ (stas@ubuntu) (gcc version 4.9.2 (Codescape GNU Tools 2016.05-03 for MIPS MTI Linux) ) #67 Wed Jul 19 00:07:19 MSK 2017 CPU0 revision is: 00019e60 (MIPS M14KEc) MIPS: machine is terasic,de10lite Determined physical RAM map: memory: 04000000 @ 00000000 (usable) Initrd not found or empty - disabling initrd Primary instruction cache 4kB, VIPT, 2-way, linesize 16 bytes. Primary data cache 4kB, 2-way, VIPT, no aliases, linesize 16 bytes Zone ranges: Normal [mem 0x0000000000000000-0x0000000003ffffff] Movable zone start for each node Early memory node ranges node 0: [mem 0x0000000000000000-0x0000000003ffffff] Initmem setup node 0 [mem 0x0000000000000000-0x0000000003ffffff] Built 1 zonelists in Zone order, mobility grouping on. Total pages: 16256 Kernel command line: console=ttyS0,115200 PID hash table entries: 256 (order: -2, 1024 bytes) Dentry cache hash table entries: 8192 (order: 3, 32768 bytes) Inode-cache hash table entries: 4096 (order: 2, 16384 bytes) Memory: 60512K/65536K available (1827K kernel code, 97K rwdata, 320K rodata, 948K init, 184K bss, 5024K reserved , 0K cma-reserved) NR_IRQS:8 clocksource: MIPS: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 38225208935 ns sched_clock: 32 bits at 50MHz, resolution 20ns, wraps every 42949672950ns Console: colour dummy device 80x25 Calibrating delay loop. 10.81 BogoMIPS (lpj=21632) pid_max: default: 32768 minimum: 301 Mount-cache hash table entries: 1024 (order: 0, 4096 bytes) Mountpoint-cache hash table entries: 1024 (order: 0, 4096 bytes) devtmpfs: initialized clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 7645041785100000 ns futex hash table entries: 256 (order: -1, 3072 bytes) clocksource: Switched to clocksource MIPS random: fast init done workingset: timestamp_bits=30 max_order=14 bucket_order=0 Serial: 8250/16550 driver, 4 ports, IRQ sharing disabled console [ttyS0] disabled b0400000.serial: ttyS0 at MMIO 0xb0401000 (irq = 0, base_baud = 3125000) is a 16550A console [ttyS0] enabled Freeing unused kernel memory: 948K This architecture does not have kernel memory protection. mount: mounting devpts on /dev/pts failed: No such device mount: mounting tmpfs on /dev/shm failed: Invalid argument mount: mounting tmpfs on /tmp failed: Invalid argument mount: mounting tmpfs on /run failed: Invalid argument Starting logging: OK Initializing random number generator. done. Starting network: ip: socket: Function not implemented ip: socket: Function not implemented FAIL Welcome to MIPSfpga mipsfpga login: root Jan 1 00:00:09 login[43]: root login on 'console' # uname -a Linux mipsfpga 4.12.2+ #67 Wed Jul 19 00:07:19 MSK 2017 mips GNU/Linux # free -m total used free shared buffers cached Mem: 60 3 56 0 0 2 -/+ buffers/cache: 0 59 Swap: 0 0 0

И наверное напишу большую статью после добавления в MIPSfpga-plus модуля для работы с mmc/sdcard, доделки загрузчика и отладки всего, что необходимо для автономного запуска.

Если кому-то нужно "прямо сейчас" - дайте знать.

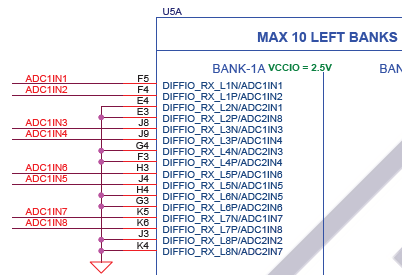

MIPSfpga-plus и АЦП Altera MAX10

В июне я завершил работу по интеграции АЦП, который есть на борту Altera MAX10, в MIPSfpga-plus. Соответствующий код добавлен в основную ветку проекта [ Л11 ], с документацией [ Л12 ] и пример [ Л13 ].Модуль, по сути, представляет собой преобразователь между шиной AHB-Lite и Avalon-ST, выполненный с учетом специфики конкретного АЦП.

По архитектуре он очень прост — я постарался сделать его программный интерфейс максимально похожим на АЦП микроконтроллера Atmel ATmega88. Были, конечно, и некоторые подводные камни, так как на ПЛИС, используемой в Terasic DE10-Lite, доступны 2 канала АЦП (с независимыми наборами входов на каждом); при подключении этих входов второй канал оказался полностью заземлен, т.е.

параллельная работа каналов на DE10-Lite невозможна:

Хочется верить, что в академических проектах MIPSfpga-plus будет использоваться чуть чаще там, где раньше ради встроенного АЦП приходилось брать микроконтроллер или конфигурацию MAX10+NIOS-II.

Опять же, нужна ли отдельная статья, где подробно рассматривается работа с АЦП? Или для того, чтобы разобраться, вам достаточно уже приведенных мною ссылок на исходный код модуля, пример и документацию?

Логотип MIPSfpga-plus

Считаете ли вы, что проект MIPSfpga-plus достаточно зрел, чтобы иметь собственный узнаваемый логотип? Потратив на это, наверное, десятки часов, мне уже хочется, чтобы это ассоциировалось с какой-то позитивной картинкой.На ум почему-то приходит только «Большое Ухо» из одноименного мультфильма (см.

КДПВ), возможно, из-за его конфедеративного характера, который хорошо ассоциируется с изначальной просветительской направленностью проекта.

И в принципе мне очень нравится этот персонаж.

Что вы думаете об этой теме? Может быть, вы предложите какой-то альтернативный вариант, а может, среди читателей найдется художник, который сможет изобразить «персонажа мультфильма, отдалённо напоминающего Большое Ухо, но не до степени растерянности»?

Благодарности

Автор выражает благодарность команде переводчиков учебника «Цифровое схемотехнико и компьютерная архитектура» Дэвида Харриса и Сары Харрис [ Л2 ], Технологии воображения [ Л1 ] за академическую лицензию на современное процессорное ядро и учебные материалы, а также лично Юрию Панчулу ЮрийПанчул за его работу по продвижению MIPSfpga. Особая благодарность Александру Романову (НИУ ВШ?, МИЭМ) [ Л15 ] за практичный и основательный подход к микроархитектуре schoolMIPS, а также всем участникам рассылки Young Russian Chip Architects, принявшим участие в обсуждении.

Ссылки

[Л1] — Пресс-релиз о выходе MIPSfpga 2.0 ; [Л2] — Цифровая схемотехника и компьютерная архитектура ; [Л3] — Семинар по образованию в области компьютерной архитектуры (Торонто) ; [Л4] — Проект MIPSfpga-plus на github ; [Л5] — Летняя школа для программистов (Новосибирск) ; [Л6] — Летняя школа программистов (Новосибирск).Программа обучения

; [Л7] — Проект schoolMIPS на GitHub ; [Л8] — Школа-семинар по цифровому дизайну и компьютерной архитектуре (Томск) ; [Л9] — Поддержка MIPSfpga в ядре Linux ; [Л10] — MIPSfpga и внутрисхемная отладка ; [Л11] — MIPSfpga-плюс.Модуль поддержки АЦП Altera MAX10

; [Л12] — MIPSfpga-плюс.Модуль поддержки АЦП Altera MAX10. Документация

; [Л13] — MIPSfpga-плюс.Модуль поддержки АЦП Altera MAX10. Пример

; [Л14] — Практический опыт на основе MIPSfpga ; [Л15] — Профиль Александра Романова на сайте ВС? .В опросе могут участвовать только зарегистрированные пользователи.

Войти , Пожалуйста.

О чем написать в следующий раз 30% перевод статьи Практический опыт на базе MIPSfpga 6 25% подробная статья об интеграции MIPSfpga и АЦП Altera MAX10 5 30% статья о запуске Linux на MIPSfpga в его нынешнем виде 6 15% не надо Не отвлекайтесь на написание, сделайте это лучше, загрузив Linux с mmc/sdcard 3 Проголосовали 20 пользователей.

6 пользователей воздержались.

Теги: #FPGA #verilog #mips #mips #mipsfpga #mipsfpga #MIPS microAptiv UP #C++ #Системное программирование #soc #Системный анализ и проектирование #Системное программирование #FPGA #Программирование микроконтроллеров

-

Нечего Надеть? Компьютерное Зрение В Помощь

19 Oct, 24 -

История Винила В Автомобилях

19 Oct, 24 -

Чистый Доход $210 000 На Человека

19 Oct, 24 -

Дискуссии По Геймдизайну Vr-Игр

19 Oct, 24 -

Новый Гугл Хром

19 Oct, 24 -

Ваша Собственная Домашняя Атс

19 Oct, 24 -

Установка Ubuntu На Eee Pc

19 Oct, 24 -

Кому Может Понадобиться К-Мелеон?

19 Oct, 24