Мы продолжаем двигаться к созданию реальных устройств на базе ПЛИС комплекса Redd. Для другого проекта All-Hardware мне нужен простой логический анализатор, поэтому мы будем двигаться в этом направлении.

Если повезет, мы доберемся до анализатора USB-шины (но это еще в далеком будущем).

Сердце любого анализатора — это оперативная память и блок, который сначала закачивает в нее данные, а затем удаляет их.

Сегодня мы как раз его спроектируем.

Для этого освоим блок DMA. Вообще DMA — моя любимая тема.

Я даже сделал большой статья о DMA в некоторых ARM-контроллерах .

Из той статьи понятно, что DMA забирает такты из шины.

В текущей статье мы рассмотрим, как обстоят дела в случае с процессорной системой на базе FPGA.

Предыдущие статьи серии

- Разработка простейшей «прошивки» для ПЛИС, установленной в Redd, и отладка на примере теста памяти.

- Разработка простейшей «прошивки» для ПЛИС, установленной в Redd. Часть 2. Программный код.

- Разработка собственного ядра для интеграции в процессорную систему на базе FPGA.

- Разработка программ для центрального процессора Redd на примере доступа FPGA.

- Первые эксперименты по использованию потокового протокола на примере связи ЦП и процессора в ПЛИС комплекса Redd.

- Весёлый Квартусель, или как процессор дошёл до такой жизни.

- Методы оптимизации кода для Redd. Часть 1. Влияние на кэш.

- Методы оптимизации кода для Redd. Часть 2: некэшируемая память и параллелизм шин.

- Обширная оптимизация кода: замена тактового генератора для улучшения производительности системы.

- Доступ к сложным шинам Redd, реализованным на контроллерах FTDI

- Работа с нестандартными шинами комплекса Редд

- Практика работы с нестандартными шинами комплекса Редд.

- Проброс USB-портов из Windows 10 для удаленной работы

- Использование процессорной системы Nios II без процессорного ядра Nios II

Создание оборудования

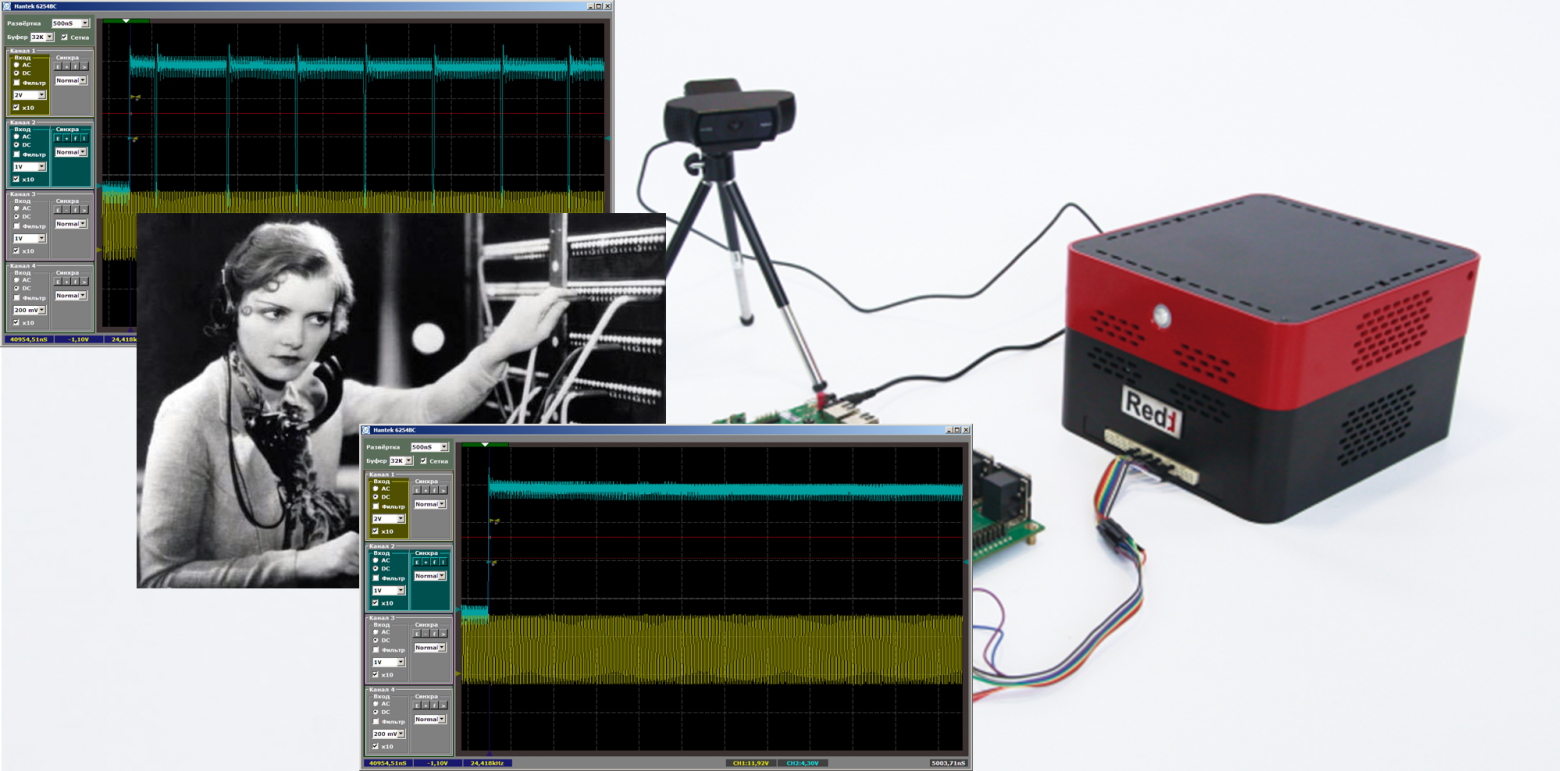

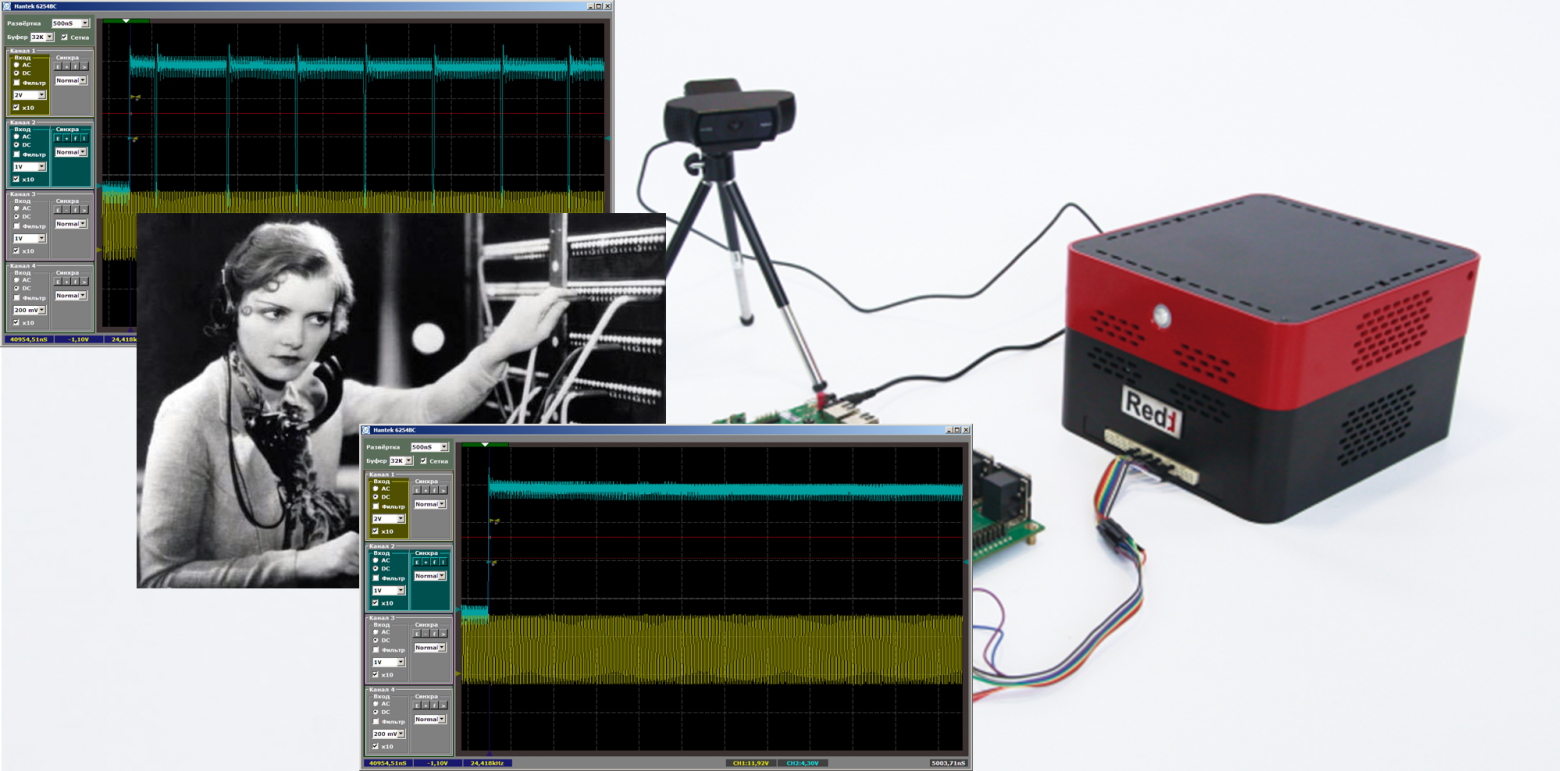

Начинаем создавать аппаратуру.Чтобы понять, насколько блок DMA спорен по тактовым частотам, нам потребуется провести точные измерения при высокой нагрузке на шину Avalon-MM (Avalon Memory-Mapped).

Мы готовы выяснил что мост Altera JTAG-to-Avalon-MM не может создать высокую нагрузку на шину.

Поэтому сегодня нам придется добавить в систему процессорное ядро, чтобы оно обращалось к шине на высокой скорости.

Как это делается описано здесь .

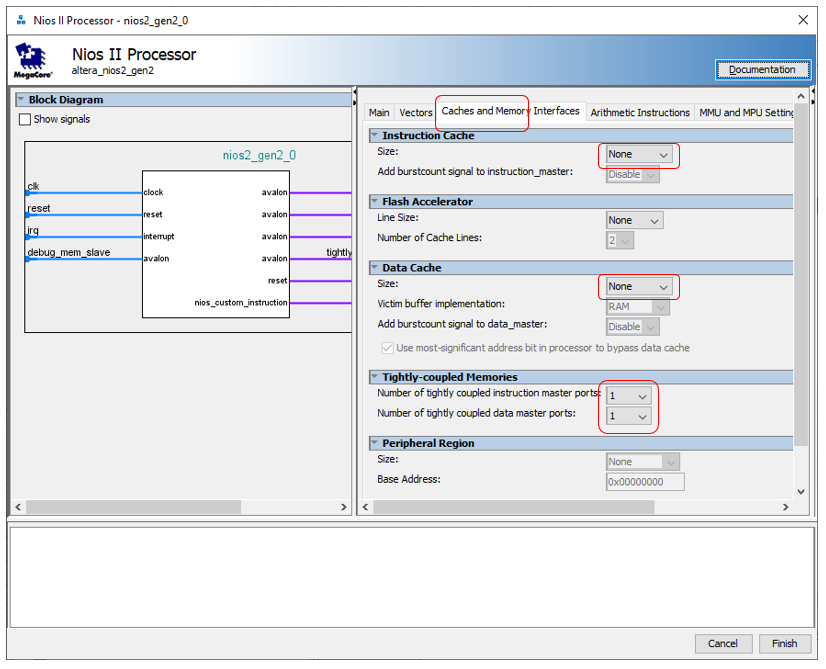

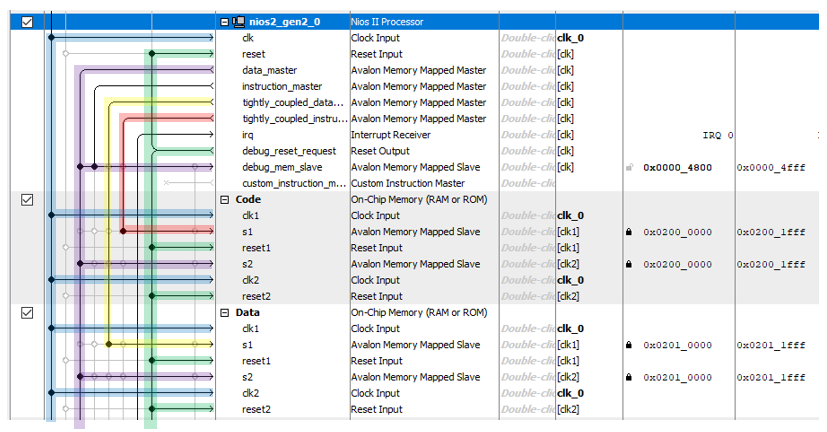

Ради оптимальности отключим оба кэша ядра процессора, но создадим по одной сильносвязанной шине, как мы это сделали здесь .

Добавим по 8 килобайт памяти программ и памяти данных.

Помним, что память должна быть двухпортовой и иметь адрес в специальном диапазоне (чтобы не прыгала - заблокируем, причины всего этого мы обсуждали здесь ).

Мы уже тысячу раз создавали проект, поэтому в самом процессе создания нет ничего особенно интересного (во всяком случае, все этапы создания описаны здесь ).

База готова.

Теперь нам нужен источник данных, который мы поместим в память.

Идеальная вещь — это постоянно тикающий таймер.

Если в течение какого-то такта блок DMA не смог обработать данные, то мы это сразу увидим по отсутствующему значению.

Ну то есть если в памяти есть значения 1234 и 1236, то на такте при выходе таймера 1235 блок DMA не передавал данные.

Создать файл Таймер_ST.sv с помощью этого простого счетчика:

Теги: #Программирование микроконтроллеров #Компьютерное оборудование #Системное программирование #FPGA #pls #FPGA #pls #DMA #Redd #Авалон-ММ.module Timer_ST ( input clk, input reset,

Avalon-ST #закачивает потоковые данные в память

-

Анализ Acer Aspire-As5738Pg-6306

19 Oct, 24 -

10 Главных Проблем На Пути Внедрения Devops

19 Oct, 24 -

Habreffect.ru: Прощание С Пользователями

19 Oct, 24 -

Не Только Интернет. Стартапы В Эпоху Перемен

19 Oct, 24 -

Windows Vista Будет Жить До 31 Мая

19 Oct, 24