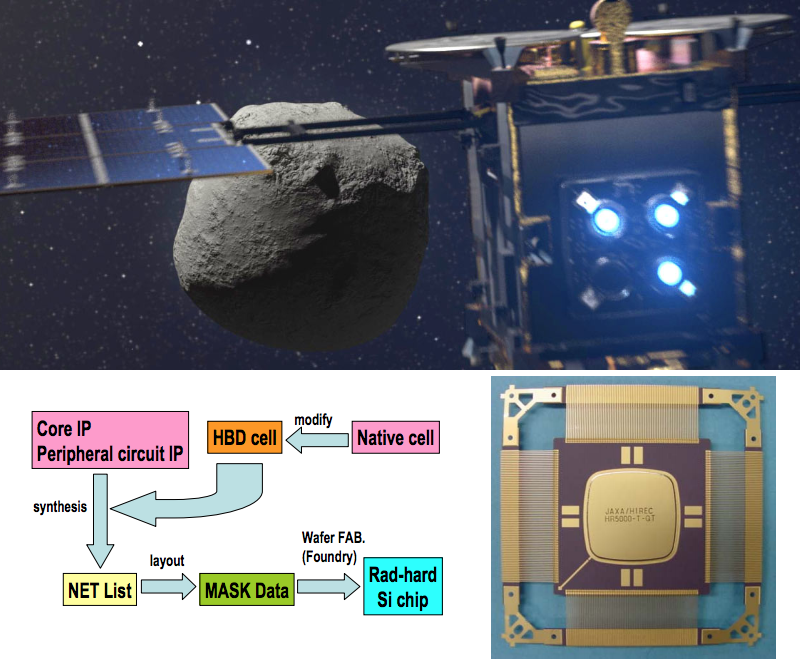

В другой день Японская автоматическая станция Хаябуса-2 сбросила бомбу на астероид Рюгу .

Управление космическим кораблем осуществляется радиационно-стойкой микросхемой HR5000 (JAXA2010/101) с 64-битным процессорным ядром MIPS 5Kf. Бортовой компьютер работает под управлением операционной системы реального времени uITRON, одной из семейства RTOS стандарта TRON, появившейся в Японии еще в 1980-х годах.

и заслуживает отдельного поста .

В этой заметке я кратко опишу, что входит в состав SoC HR5000 и его процессорного ядра, покажу фотографии двух ключевых разработчиков линеек MIPS 4K и 5K, а также расскажу, как можно дома поиграться на FPGA. плата с «потомком младшего брата» этого компьютера — 32-битное ядро MIPS microAptiv UP, которое было закодировано на языке описания оборудования Verilog и базировалось на MIPS 4KEc.

Японское аэрокосмическое агентство JAXA лицензировало процессорное ядро MIPS 5Kf у американской компании MIPS Technologies. Это произошло еще в 2000-х годах.

Группа, разработавшая это ядро, существует в различных конфигурациях уже 40 лет:

- MIPS был первым проектом в Стэнфорде в 1978–1984 годах, которым руководил Джон Хеннесси.

Благодаря успеху этого проекта Хеннесси стал автором самого известного учебника по компьютерной архитектуре и в какой-то момент президентом Стэнфорда.

- Затем, в 1984 году, MIPS стала коммерческой компанией — MIPS Computer Systems. В том же году ARM также была коммерциализирована.

В 1991 году MIPS выпустила первый в мире 64-битный микропроцессор MIPS R4000.

- После этого MIPS был поглощен компанией Silicon Graphics и в 1990-х годах использовался на графических станциях, где в Голливуде (Парк Юрского периода) снимались первые фильмы с реалистичной графикой.

- В 2000-х годах группа выделилась в MIPS Technologies и, в частности, разработала процессор для JAXA. Штаб-квартира MIPS располагалась в Калифорнии, часть разработчиков MIPS 5Kf сидел в европейском офисе MIPS в Копенгагене.

- В 2012 году MIPS Technologies была куплена британской компанией Imagination Technologies, прославившейся как разработчик графических процессоров в первых Apple iPhone.

- В 2017 году Apple отказалась от Imagination и после некоторых потрясений технология и часть группы MIPS интегрировались в компанию Wave Computing — стартап, занимающийся разработкой чипа для ускорения нейронных сетей.

- Чип Wave Computing представляет собой комбинацию кластера 64-битных процессоров MIPS I6500, матричного умножителя на основе систолического массива а-ля Google TPU и процессора потока данных на основе устройства Coarse-Grained Reconfigurable Architecture (CGRA).

Классические процессоры в кластере I6500 нагружают данными матричный умножитель и процессор потока данных, матричный умножитель обеспечивает плотность вычислений, а процессор потока данных задачи находится посередине между классическими процессорами и матричным умножителем - он более гибок, чем множитель и более производительный, чем классический процессор.

Ларри начал свою карьеру в Digital Equipment Corporation (DEC) в качестве разработчика процессоров для MicroVAX. Затем Ларри работал в небольшой компании Cyrix, которая в конце 1980-х бросила вызов Intel и создала сопроцессор FPU, совместимый с Intel 80387 и работавший на 50% быстрее.

Затем Ларри разработал чипы MIPS в Silicon Graphics. Когда MIPS Technologies отделилась от Silicon Graphics, Ларри и Райан Кинтер запустили первый независимый продукт MIPS, MIPS 4K, который стал основой линейки, доминировавшей в домашней электронике в 2000-х годах (DVD-плееры, фотоаппараты, цифровые телевизоры).

Затем MIPS 5K полетел в космос — его использовало японское космическое агентство JAXA. Затем Ларри в качестве вице-президента по разработке аппаратного обеспечения возглавил разработку следующих направлений и сейчас работает над новыми архитектурами ускорителей Wave:

Теперь вернемся к процессору в Хаябусе-2 (в Хаябусе-1 он другой).

Здесь Техническое описание процессорного ядра MIPS64 5Kf И Страница данных встроенной системы HR5000 .

Отметим несколько интересных моментов.

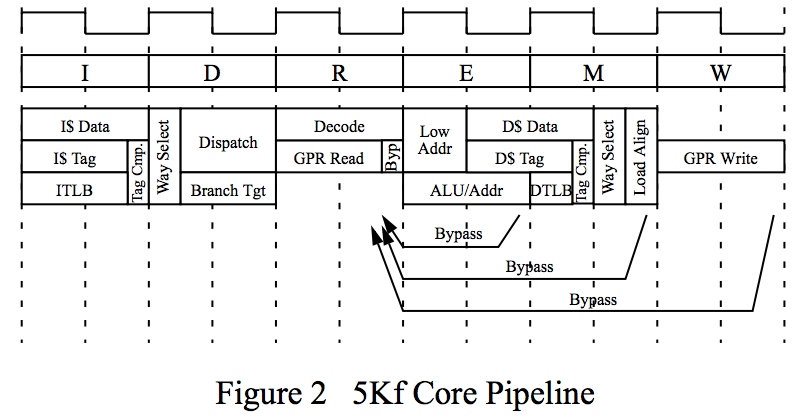

Прежде всего, MIPS 5Kf — это конвейерный процессор.

Если вы незнакомы с тем, как это работает, то самый простой способ познакомиться — изучить седьмую главу книги Дэвида М.

Харриса и Сары Л.

Харрис «Цифровое схемотехника и архитектура компьютеров», последней версии русской книги.

перевод которого можно скачать Здесь или Здесь ).

Однако конвейер MIPS 5Kf отличается от классического конвейера MIPS от Harris & Harris. Те из вас, кто читал X&X, могут посмотреть на различия и догадаться, почему:

Конечно, MIPS 5Kf имеет не пять ступеней конвейера, а шесть, с дополнительной ступенью Dispatch. Этот этап необходим для того, чтобы сделать MIPS 5Kf ограниченным суперскаляром.

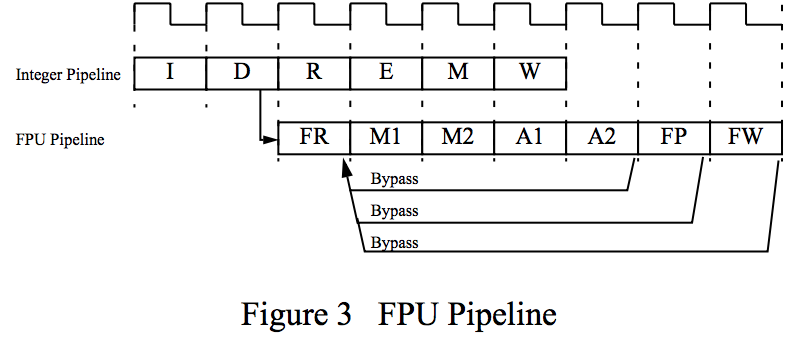

Он не только может выполнять операции одну за другой в конвейере, но также может выполнять операцию с плавающей запятой одновременно с целочисленной операцией или с операцией памяти (загрузка или сохранение).

На этапе диспетчеризации работает сопроцессор с плавающей запятой, который имеет собственный семиэтапный конвейер:

А вот справа на фото Даррен Джонс, разработчик FPU в MIPS 5Kf. «f» в «5Kf» означает именно то, что он имеет плавающую точку:

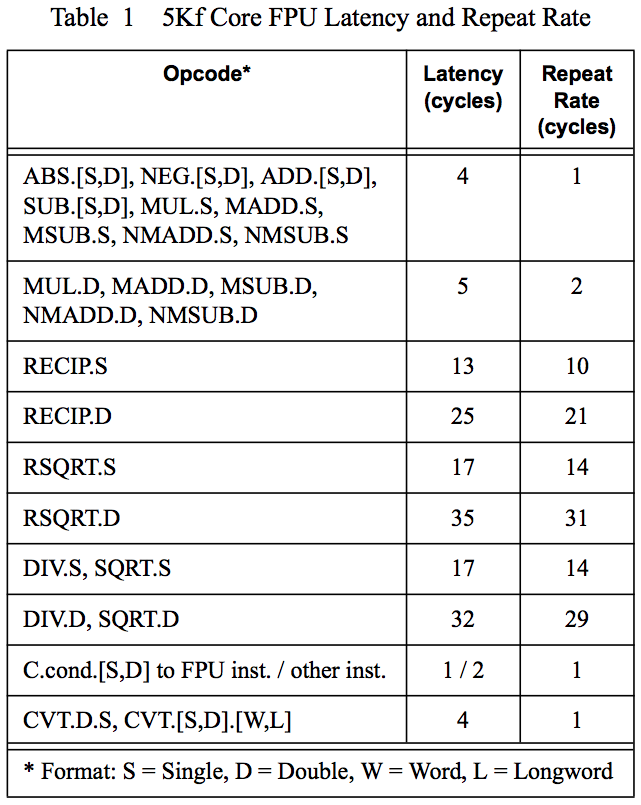

Вот в этой таблице можно увидеть, сколько тактов требуют различные операции в FPU и как часто (частота повторения) их можно запускать в конвейер.

Например, для умножения одинарной точности требуется четыре цикла, но вы можете помещать в конвейер новое умножение в каждом цикле.

Таким образом, FPU может одновременно обрабатывать четыре умножения одинарной точности на каждом этапе обработки.

Но умножение двойной точности требует пяти циклов и может выполняться только с паузой на каждый цикл.

Сложная операция извлечения квадратного корня двойной точности требует целых 32 тактов, а новое извлечение квадратного корня можно начать только после 29 тактов.

Вот как оптимизируется расчет координат корабля и формулы его движения в космическом пространстве:

Hayabusa-2 использует конфигурацию MIPS 5Kf с отдельными кэшами инструкций и данных размером 32 КБ.

В то же время из Краткое описание HR5000 неясно, использует ли он четырехканальный кэш емкостью 8 килобайт или двухканальный кэш объемом 16 килобайт. Вы можете прочитать, как эти кеши работают как в X&X, так и в моя старая презентация про тайники , а также в полезной книге См.

MIPS Run Linux, 2-е издание, автор Доминик Свитман:

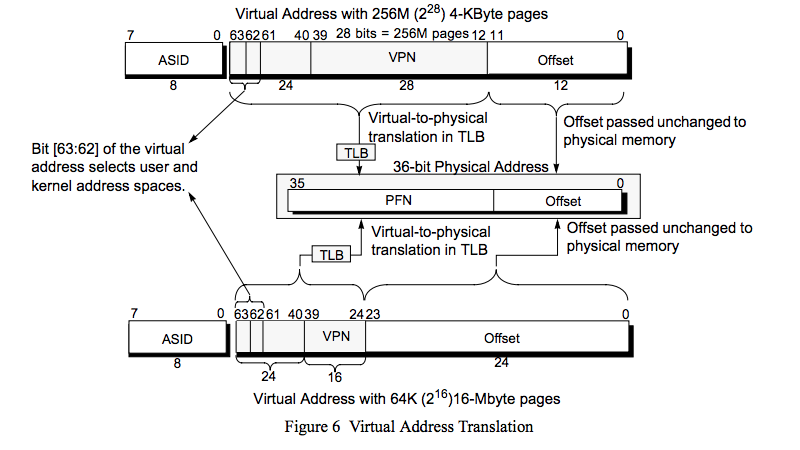

Hayabusa-2 также имеет блок управления памятью (MMU) с резервным буфером трансляции (TLB).

TLB — универсальное средство быстрого преобразования адресов из виртуальных в физические.

TLB позволяет:

- Скройте память операционной системы от непривилегированного кода.

- Защищайте пользовательские программы друг от друга.

- Обеспечить программе доступ к объему виртуальной памяти, превышающему объем физической оперативной памяти.

- Адресуйте больше физической памяти, чем доступны виртуальные адреса.

- Разместите программу в любой части физической памяти.

- Позволяет нескольким областям памяти отображаться как последовательный фрагмент.

- Позволяет загружать фрагменты программы с внешнего устройства по мере необходимости.

- TLB также связывает с адресом различные атрибуты: чтение, запись и выполнение запрещены, а также атрибуты кэширования и согласованности.

- Атрибут кэшируемости необходим, чтобы показать процессору, где находится адресное пространство для следующего уровня кэша, а где — для регистров ввода-вывода, которые не могут быть кэшированы.

- Атрибуты когерентности нужны для совместной работы нескольких ядер процессора, каждое из которых имеет свой кеш первого уровня, а вместе они используют общий кеш второго уровня.

- Атрибут кэшируемости необходим, чтобы показать процессору, где находится адресное пространство для следующего уровня кэша, а где — для регистров ввода-вывода, которые не могут быть кэшированы.

- TLB может хранить индикатор того, что страница по данному адресу была записана.

Это помогает при подкачке, загрузке и выгрузке страниц памяти в системах с меньшим количеством физической памяти, чем необходимо приложению, для адресации всех частей своего кода и данных с помощью виртуальных адресов.

Возможно, для каких-то алгоритмов 64-битная арифметика и 64-битный обмен кешем (или 64-битный обмен некэшируемой памятью) что-то улучшают и это оказывается полезно в космосе.

Но я точно не знаю, может надо спросить Зеленикот И амартология которые знают о космосе больше, чем я.

Вы можете прочитать о TLB в X&X и См.

MIPS Run, но есть одна оговорка: обе книги описывают, как выглядит TLB с точки зрения программиста.

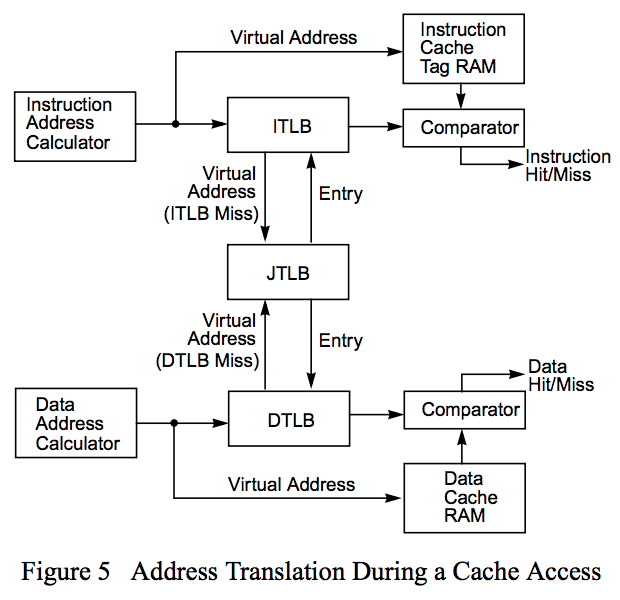

Но с точки зрения аппаратного инженера проектировщики процессоров обманывают программиста, показывая ему TLB как одну таблицу ассоциативного перевода, несмотря на то, что внутри TLB Хаябуса-2 на самом деле три таблицы: микро-TLB инструкций, микро-TLB -TLB данных и общий (Joint TLB).

Сначала устройство управления памятью смотрит в ITLB и DTLB и только если не находит, берет из JTLB. Это стоит процессору дополнительных 2 тактов.

Также см моя старая презентация про TLB :

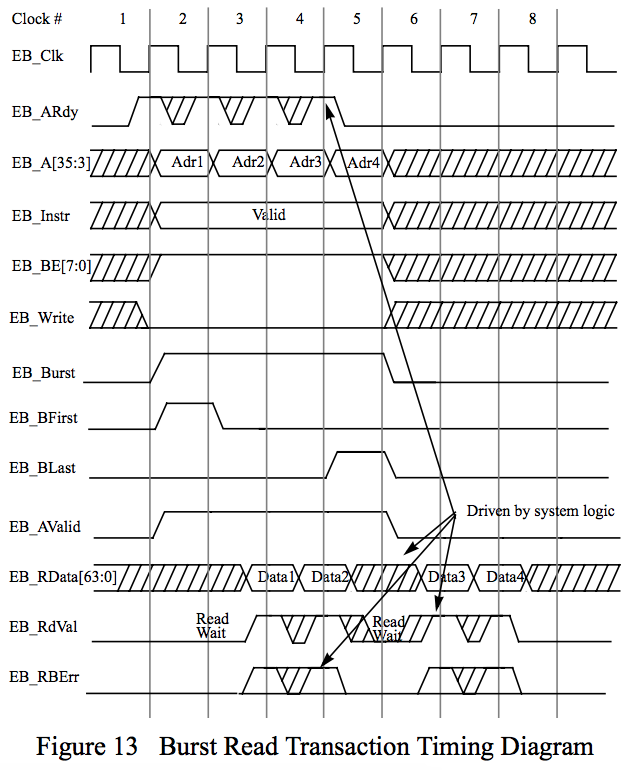

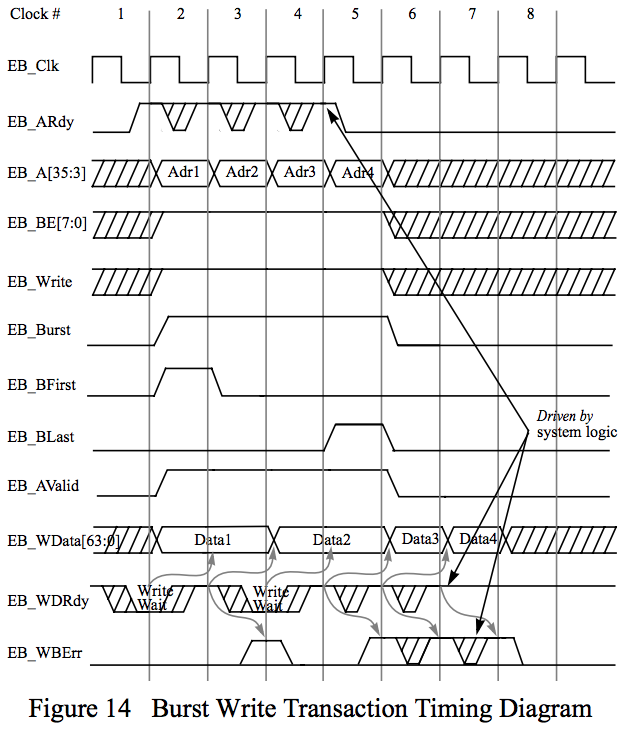

Интерфейс между кэшами L1 и контроллером памяти MIPS 5Kf Hayabusa-2 называется EB (произносится как E-Bee).

Это сокращение от «Внешняя шина».

Он похож на AHB и AXI и позволяет пакетировать, испускать из кеша или загружать в кеш всю строку из памяти, используя передачи в последовательных циклах.

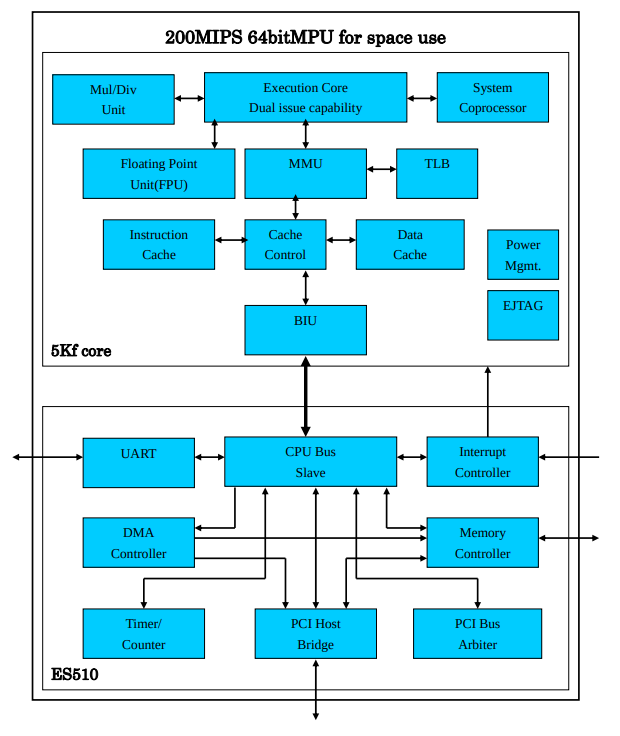

За пределами ядра процессора HR5000 имеет контроллер прерываний, модуль UART, контроллер прямого доступа к памяти, таймеры и контроллер PCI:

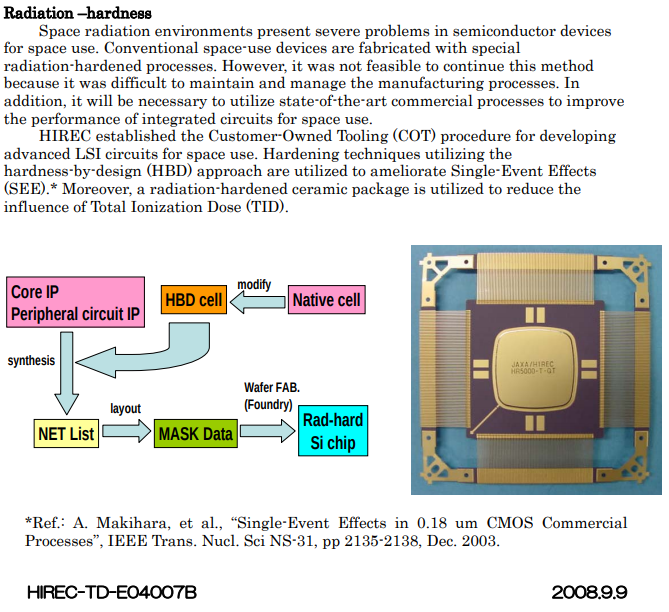

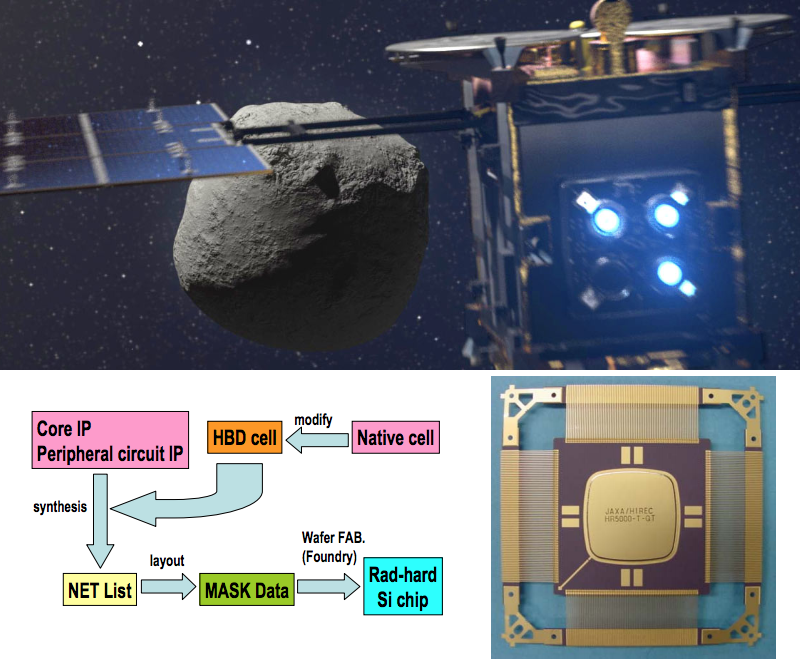

Для работы в космосе чип должен быть защищен от радиации.

Я не специалист по радиационной защите, для этого есть амартология , но я знаю, что такую защиту можно сделать и на уровне физической технологии производства, и на уровне различных ECC-проверок, и даже на архитектурном уровне, с триплетом и т.д. Создатели системы-на-кристалле HR5000 решил использовать обычный маршрут RTL2GDSII, распространённый в коммерческих приложениях, синтезируя граф логических элементов из кода на языке описания аппаратуры Verilog. Однако, получив такой граф (нетлист), они модифицируют его с помощью специальной библиотеки примитивов Hardness-by-Design (HBD) (я этим никогда не пользовался, поэтому любые пояснения в комментариях приветствуются):

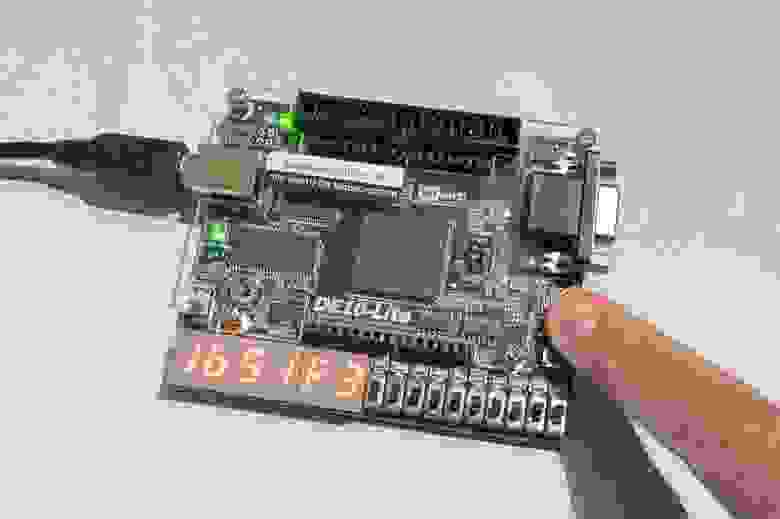

Поскольку MIPS 5Kf написан на Verilog, его можно превратить не только в список соединений и не только в маску для изготовления чипов на фабрике, но и в конфигурацию FPGA. К сожалению, исходники MIPS 5Kf в открытом доступе отсутствуют, но в открытом доступе находятся исходники потомка его «младшего брата», 32-битного процессора MIPS 4K. Этот «потомок» называется MIPS microAptiv UP, а его базовая конфигурация включена в пакет MIPSfpga. Код MIPS 4K/4KEc/microAptiv UP/M5150 (это все прогрессивные версии линейки) также в свое время был написан Ларри, Райаном и Дарреном.

Вы можете поиграться с конвейером, кэшами, управлением памятью и прерываниями ядра MIPS microAptiv UP, запустить его на симуляторе или плате FPGA/FPGA. Для этого достаточно скачать пакет Пакет для начала работы с MIPS Open™ FPGA , вместе с Лаборатории MIPS Open™ FPGA , и (это важно!) дополнить его MIPSfpga+ .

Последний имеет лабораторные работы по конвейеру, устройству управления кэшем и памятью .

Вы можете синтезировать и запустить процессор MIPS microAptiv UP на недорогой плате за 85 долларов (академическая цена 55 долларов):

Для работы с пакетом MIPSfpga/MIPSfpga+ необходимо знание языка описания аппаратуры Verilog, принципов проектирования на уровне передачи регистров и умение писать ассемблер MIPS.

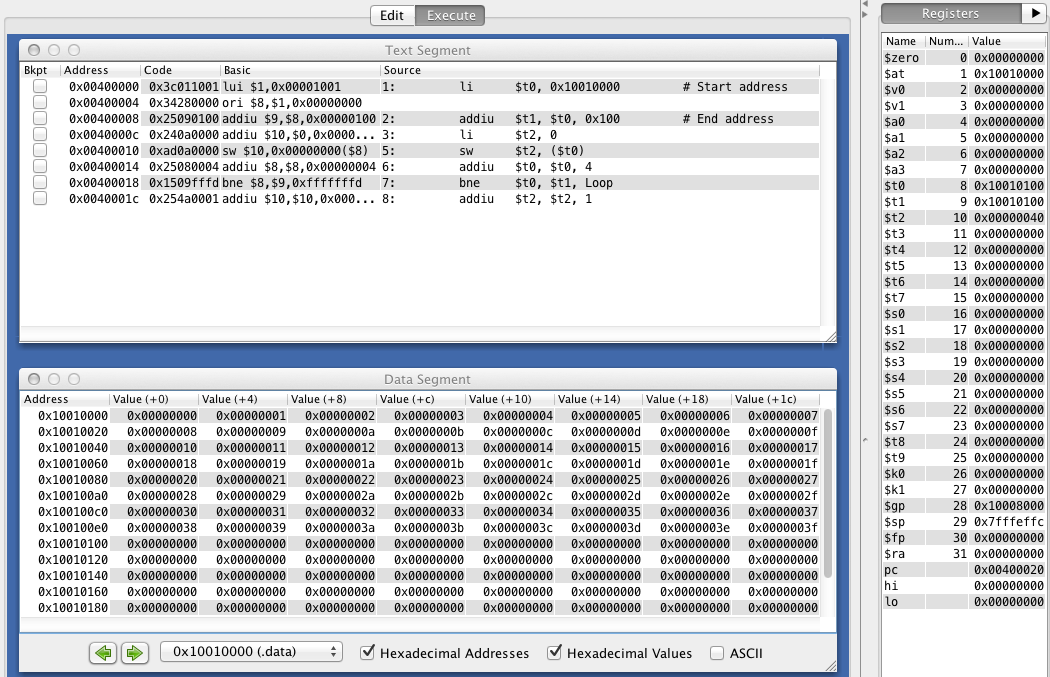

Ассемблер MIPS проще всего изучить.

Для этого вы можете скачать симулятор MARS (MIPS Assembler и Runtime Simulator) .

Вы можете научиться им пользоваться за 5 минут; на самом деле там три кнопки — собрать, запустить, запустить шаг за шагом:

Затем вы можете провести день, практикуясь в написании языка ассемблера по книгам.

MIPS Run Linux. .

Если вы совершенно ничего не знаете о разработке цифровых схем вообще и в языке описания аппаратуры в частности, можете начать с онлайн-курса Роснана для школьников, в трех частях: «От транзистора к микросхеме» , «Логическая сторона цифровой схемотехники» , «Физическая сторона цифровой схемотехники» ).

Потом можно изучить Verilog с помощью X&X и понять, что есть процессор на базе упрощенного процессора школаMIPS .

Если вам интересна эта тема и вы хотите принять участие в работе над МИПС Открытый (в рамках которого было открыто ядро MIPS microAptiv UP), пишите в комментариях.

Роснановцы также проводят семинар для школьников по цифровому дизайну 17-19 апреля , где мы также поговорим об этом космическом процессоре.

Хаябуса-2 не зря бомбил Рюгу — это еще и возможность для российских школьников и студентов узнать, что у него внутри.

В опросе могут участвовать только зарегистрированные пользователи.

Войти , Пожалуйста.

Стоит ли открывать исходники процессорного ядра MIPS 5Kf, которое находится внутри Hayabusa-2? 66,67% Да 76 33,33% Нет, инопланетяне взломают его через EJTAG и отправят вирусы на Землю 38 Проголосовали 114 пользователей.

28 пользователей воздержались.

Теги: #Космонавтика #Программирование микроконтроллеров #космос #астероид #Процессоры #открытый исходный код #FPGA #mips #mips #mipsfpga #mipsfpga #mips open #Hayabusa-2 #hayabusa-2

-

Календари И Измерение Времени

19 Oct, 24 -

Xcom: Enemy Unknown Портируется На Linux

19 Oct, 24 -

Nagios: Уведомление По Sms

19 Oct, 24 -

Фракталы В Иррациональных Числах

19 Oct, 24 -

Fl Studio - Путь Джедая (Часть 1).

19 Oct, 24