При проектировании различных цифровых устройств, в частности контроллеров, необходимо организовать задержку подачи одного и того же сигнала на разные выводы ПЛИС или на другие элементы внутри ПЛИС.

Сначала рассмотрим аналогичную ситуацию с дискретной логикой.

Обычно, если у разработчика есть микросхема с шестью вентилями НЕ (например, 155ЛН1), он использует последовательное соединение двух элементов в качестве элемента задержки (10.20 наносекунд).

Иногда он вставляет между ними RC-цепочку, с помощью которой можно сделать время задержки от 10 до 150 нс.

В микросхеме FPGA задержка НЕ МОЖЕТ быть организована таким образом.

Все дело в особенностях синтеза конструкции.

Программа синтеза воспринимает двойной минус как лишнее звено (как ошибку) и устраняет его.

На RC-цепях также невозможно организовать задержку, поскольку ПЛИС плохо переносит емкостные нагрузки.

Поэтому для организации задержки я рекомендую следующий способ.

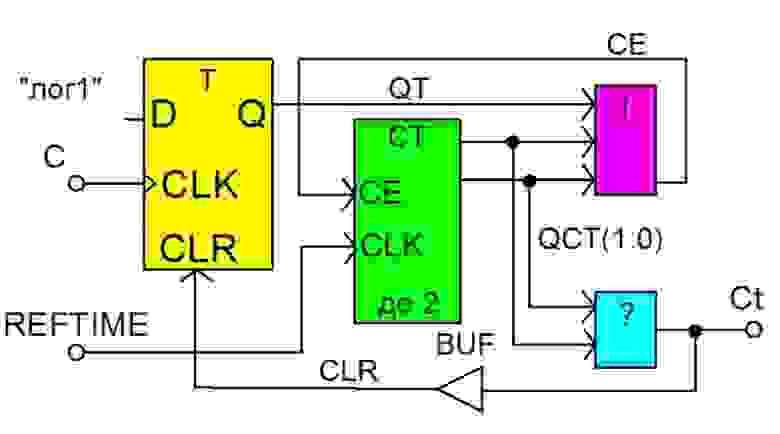

Схематично это выглядит так:

Сигнал Ct — это тот же сигнал C, только с задержкой 100 нс.

Сигнал опорного времени представляет собой импульсный сигнал определенной частоты, который нам необходимо использовать в элементе задержки.

Период этого сигнала представляет собой минимально возможное время, на которое мы можем задержать сигнал Ct относительно C. В нашем случае период опорного временного сигнала составляет 50 нс (частота 20 МГц).

Теперь представляю вашему вниманию «железную» конструкцию элемента задержки:

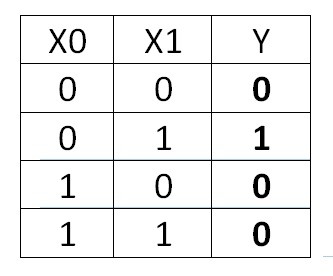

В этой структуре есть только один непонятный синий элемент «Э».

На самом деле это всего лишь продукт комбинаторной логики.

Я не буду расшифровывать структуру этого элемента; Приведу лишь таблицу истинности:

Элемент ЭT представляет собой обычный D-триггер с синхронизацией по фронту сигнала C. Элемент ТТ представляет собой счетчик импульсов опорной частоты (времени) REFTIME. В дополнение к тактовому входу CLK он имеет вход разрешения CE. Чтобы сгенерировать время задержки 100 нс, счетчик должен закончить счет до двух (50 x 2 = 100).

Этот параметр впоследствии необходимо указать в коде VHDL счетчика.

?Элемент розового цвета – 3-ИЛИ.

Буфер BUF необходим для отделения выходного сигнала Ct от внутреннего сигнала CLR. Опытному разработчику нет необходимости объяснять, как работает эта схема, но поскольку эту статью читают и начинающие разработчики, я приведу краткое описание того, как работает схема.

Внешний сигнал REFTIME частотой 20 МГц подается на счетчик ТТ непрерывно.

Вход «D» Т-триггера постоянно привязан к логической единице.

При подаче фронта сигнала С на вход CLK триггера первый из них появляется на входе элемента 3-ИЛИ.

Этот элемент сразу позволяет счетчику считать.

Как только счетчик досчитал до 2х, D-триггер тут же сбрасывается в состояние логического нуля и вместе со следующим импульсом REFTIME на его выходах появляются логические нули.

При этом аккаунт блокируется.

Особенность этой схемы в том, что сигнал С не только задерживается на 100 нс, но и сокращается его длительность до 50 нс (т.е.

до периода опорного сигнала).

В большинстве случаев эта особенность не является критичной и ее можно просто игнорировать.

Но эту особенность можно также использовать целенаправленно для формирования длительности импульса.

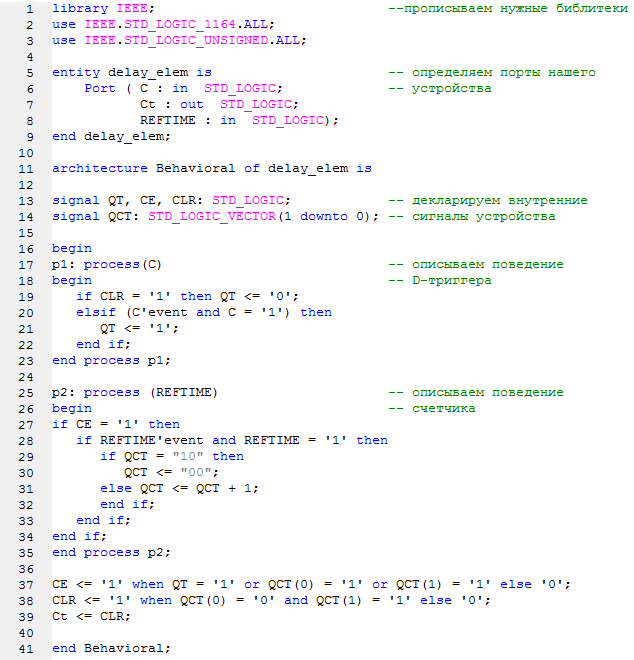

Представляю вашему вниманию текст VHDL программы элемента задержки:

Процесс, обозначенный p1, описывает поведение D-триггера, а процесс, обозначенный p2, описывает поведение счетчика.

Теги: #vhdl #vhdl #vhdl #vhdl #delay #pls #pls #pls #signal #программирование микроконтроллера

-

Похоже На Скриншоты Windows 7

19 Oct, 24 -

Как Вызвать Интерес У Технарей?

19 Oct, 24 -

Больные Вопросы О Хостинге

19 Oct, 24