На выставке Hot Chips прошлое В августе этого года ведущий инженер Cisco Джейми Маркевич рассказал об особенностях сетевого процессора 400 Гбит/с, который в настоящее время поставляется клиентам.

/Фликр/ Тимоти Лоуренс / СС

Чип изготовлен по 22-нанометровому техпроцессу и имеет 672 ядра, каждое из которых обрабатывает до четырех потоков.

Сетевой процессор (NPU) содержит 9,2 миллиарда транзисторов и 353 МБ SRAM. SRAM действует как кэш L0, в котором хранятся инструкции и данные для каждого потока.

Также имеется кэш L1 для кластера из 16 ядер.

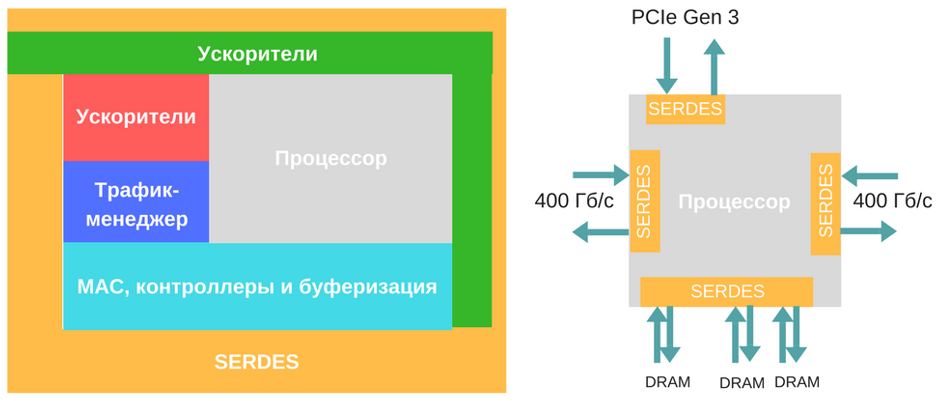

NPU имеет 42 кластера ядер, которые подключены к кэшу инструкций L2 через кэш инструкций L2. Он также объединяет в единую «сеть» кэши разных уровней, хранилища пакетов данных, ускорители, встроенную и динамическую память.

Эта сеть работает на частоте 1 ГГц и имеет пропускную способность более 9 Тбит/с.

Блок-схема чипа

Cisco не рассказала о наборе команд, который используется в NPU. Однако эксперты сделали предположение , что это кастомный комплект, созданный специально для работы с сетью, а не ARM, MIPS, Power или X86.

Потоки ядра NPU обеспечивают обработку пакета данных на протяжении всей его «жизни» на кристалле.

Это исключает время простоя или «перетасовку» пакетов между ядрами.

Таким образом, одновременно можно обрабатывать 2688 пакетов.

Пакеты хранятся вне чипа в DRAM, но обрабатываются в реальном времени в SRAM. Более того, ускорители могут получить доступ к копии DRAM независимо от того, какие ядра работают с оригиналом SRAM. Поскольку разные пакеты требуют разных спецификаций, все ядра различаются по производительности, чтобы обеспечить максимальную эффективность.

При этом Cisco NPU поддерживает привычные методы программирования — C или ассемблер.

Сетевой процессор обрабатывает пакеты со скоростью 800 Гбит/с или 400 Гбит/с в полнодуплексном режиме.

В свою очередь, пропускная способность интерфейса SERDES составляет 6,5 Тбит/с.

Большая часть соединений используется для подключения DRAM и TCAM — последний хранит списки доступа (ACL).

Он также используется для буферизации пакетов, поэтому иногда его недостаточно — тогда часть данных сохраняется в DRAM. Большая часть логики NPU работает на частоте 760 МГц или 1 ГГц.

MAC-интерфейсы поддерживают работу портов на скоростях от 10 до 100 Гбит/с.

Сетевой процессор оснащен встроенным диспетчером трафика, который одновременно обрабатывает 256 тысяч запросов и способен обрабатывать нагрузку в полтриллиона объектов.

Ускорители берут на себя обработку префиксов IPv4 и IPv6, сжатие и хеширование диапазонов IP, доставку пакетов и сбор статистики.

Внешняя DRAM имеет 28 линий SERDES, работающих со скоростью 12,5 ГБ/с.

SERDES использует собственный последовательный протокол для доступа к памяти — он способен осуществлять до миллиарда произвольных обращений в секунду и поддерживает скорость передачи данных до 300 Гбит/с.

Логика подключается к DRAM через параллельный интерфейс ввода-вывода — максимальная скорость составляет 1250 МБ/с.

Интересно, что только процессор выполнен по 22-нанометровому техпроцессу.

DRAM производится по 30-нм техпроцессу, а SERDES и BIST — по 28-нм техпроцессу.

«Мы определили, какие операции обычно выполняются на устройствах такого типа, и оптимизировали чип для обработки случайных операций на высокой скорости.Демонстрация «внутренностей» сетевого процессора — явление не уникальное, но редкое.Его можно использовать как буфер, в котором количество операций чтения будет равно количеству операций записи, а также для поиска данных в базах данных, когда количество обновлений не столь велико», — рассказал Джейми Маркевич, главный инженер Cisco.

Производители обычно не раскрывают такую информацию, хотя случаются исключения.

В январе Barefoot Networks сказал об особенностях чипа Tofino, Innovium в марте - о Тералинксе и Mellanox Technologies в июле – о Спектр-2 .

О конференции Hot Chips

Горячие чипсы — симпозиум на тему высокопроизводительных процессоров.Впервые оно состоялось еще в 1989 году.

В этом году, помимо Cisco, в мероприятии приняли участие многие крупные производители.

В частности, Microsoft представлен свои разработки в области дополненной реальности и сказал о процессоре для Xbox One X Scorpio. Выступление китайской компании Baidu было преданный дополненная реальность и представитель Google сказал об оптимизации оборудования для нейронных сетей.

P.S. О чем еще мы пишем в нашем блоге:

- Защита персональных данных: европейский подход

- Виртуализация приложений: как правильно настроить виртуальные машины

- Особенности двухфакторной аутентификации: работает ли она в облаке IaaS

-

Ошибки Создания Интернет-Магазина

19 Oct, 24 -

Личный Кабинет От Мегафаил

19 Oct, 24 -

Запущен Поисковик Для Веб-Мастеров Codavr.ru

19 Oct, 24