Однажды мне попался заказ на оцифровку сигнала.

Частота дискретизации сигнала составляла 50 кГц.

Эту задачу я быстро выполнил, воспользовавшись мануалом из Интернета.

Однако заказчик не смог выжать из этой скорости то, что хотел, и решил разместить заказ на частоту 50 МГц.

В связи с тем, что частота изменения сигнала от 0 до 5В составляла не более 10 МГц, я решил, что насчет скин-эффекта заморачиваться не стоит и взялся за заказ.

Эти скорости были для меня новыми, и я потратил две недели на изучение материала.

Мое любимое правило – не решать проблему только из того, что лежит под ногами – мне очень помогло.

В связи с тем, что большая часть моей работы была связана с использованием stm32F1XX, я начал изучать возможность работы именно с этим производителем.

Первое, что я проигнорировал, это stm32f4XX. Дело в том, что даже при одновременной согласованной работе трёх быстродействующих АЦП частота дискретизации составит не более 7,2 МГц.

Для начала я выбрал АЦП: AD6645. Эта серия может работать с частотой дискретизации до 120 МГц.

Я выбрал на 80 МГц: AD6645-80. Сейчас есть две нерешенные проблемы: — что смотреть; - как принять сигнал.

Вариант 1. ПЛИС.

Плюсы: - работает быстро; - гибко меняется.

Минусы: — дорого, мне нужно было 500 долларов за штуку; — большие габариты, от 200 ножек и ширина от 30 мм по дигану; — незнакомая мне среда и принципы работы.

Ввиду того, что устройство небольшое, окончательное решение было принято именно из-за габаритов.

Вариант 2. Генератор TTL/HCMOS + FIFO/ Плюсы: — можно использовать любой финальный приёмник, даже 8-битный процессор; - в целом дешевле, чем FPGA. Минусы: - больше деталей и, следовательно, больше соединений высокочастотных цифровых сигналов.

Взвесив все за и против, я начал искать детали.

Многие сразу спросят, зачем поиск.

Да потому что на таких частотах много чего работает, либо очень дорого, либо срок поставки 3-5 месяцев, либо партия 100 штук (цена за штуку начинается от 50$).

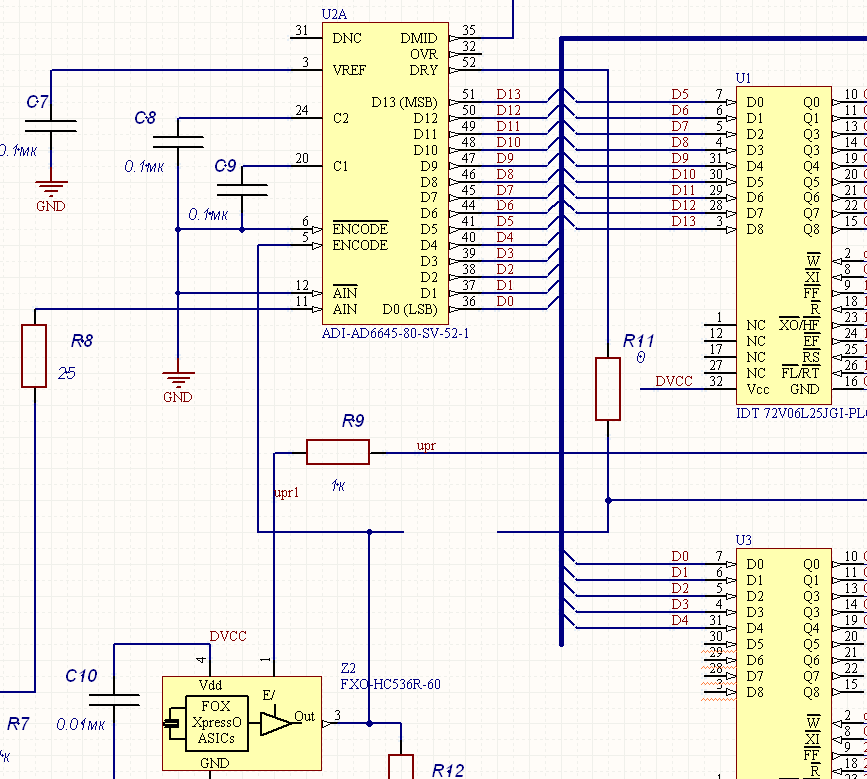

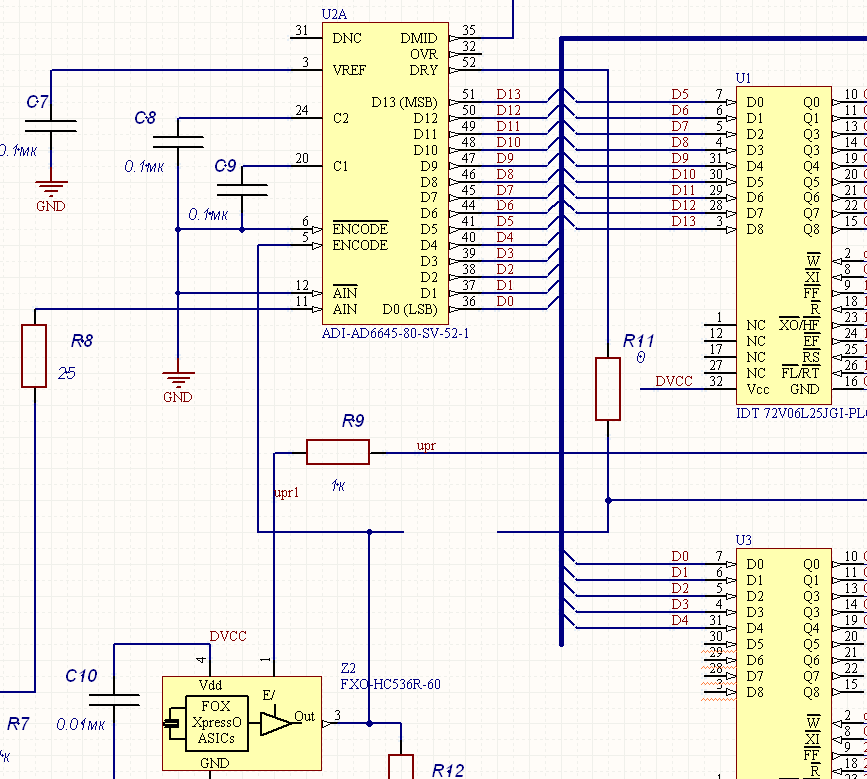

Общий: — АЦП AD6645; — ИДТ72В06; – F X O – H C 5 3 6 R; - STM32F103RET8. Принцип работы: 1. Процессор включает генератор FXO–HC536R на 1 мс.

2. Генератор тактирует АЦП AD6645. По нарастающему фронту сигнала генератора АЦП начинает оцифровку.

3. По окончании работы АЦП устанавливает ногу DRY на низкий уровень.

4. Нога –W FIFO соединена с ветвью DRY АЦП.

При появлении нижнего фронта АЦП на ножке DRY FIFO записывает данные во внутреннюю память.

5. Далее процессор берет данные из FIFO. Схема подключения представлена на рисунке.

Спасибо за внимание.

Теги: #ADC STM32 FIFO IDT72 #Программирование микроконтроллеров

-

Вариационное Исчисление

19 Oct, 24 -

Молодая Женщина

19 Oct, 24