Многие начинающие разработчики не до конца понимают значение таких параметров триггера, как Настройка и Время удержания.

О метастабильности и природе этих двух параметров написано довольно много ( https://habrahabr.ru/post/254869/ ), поэтому давайте сосредоточимся на том, как бороться с нарушениями установки и удержания в процессе проектирования схемы.

Сначала давайте определим настройку и удержание:

- Время настройки — минимальное время от момента завершения переходных процессов на входе данных до момента поступления тактового фронта на тактовый вход триггера.

- Время удержания — минимальное время от момента поступления тактового фронта на тактовый вход до начала новых переходных процессов на входе триггерных данных.

Подробнее о построении графиков и внутренней «кухне» статического тайминг-анализа вы можете прочитать в первой заметке.

https://habrahabr.ru/post/273849/ .

Теперь поговорим о том, как проверяются нарушения Setup и Hold. В синхронных схемах все переходные процессы начинаются на тактовом входе (вернее, на выходе внешнего генератора или ФАПЧ, но статический анализ не смотрит за пределы микросхемы, поэтому речь идет только о тактовом входе микросхемы).

Итак, переходный процесс (тактовый, тактовый импульс) распространяется по схемам к тактовым входам триггеров, распадаясь на множество переходных процессов, которые проходят через триггеры на их выходы, поступают в логику и заканчиваются на информационных входах приемника.

триггеры.

Главное условие работы синхронных схем: все переходные процессы должны заканчиваться за один такт. Или, точнее, не за один такт, а к моменту поступления следующего тактового импульса, который на самом деле для каждого триггера разный, поскольку схема тактирования в реальной микросхеме построена по принципу дерева.

О дереве.

Очевидно, что схема тактирования имеет настолько большое количество нагрузок, что ни один логический элемент не имеет достаточной мощности, чтобы прокачать их все.

Поэтому тактовую схему оформляют в виде дерева, вершина которого — тактовый вход микросхемы, ветви — буферы усиления или инверторы, а листья — тактовые входы триггеров.

Дерево не идеальное (часто оно так делается специально), поэтому всегда происходит неодновременное поступление часов на различные триггеры.

Из-за этого получается, что на некоторых участках схемы переходные процессы должны закончиться раньше, а на других участках позже - просто чтобы успеть время Tsetup до прихода тактового импульса.

Давайте посмотрим на следующую картинку (картинка и формулы заимствованы из англоязычной статьи http://www.edn.com/design/systems-design/4392195/Equations-and-Impacts-of-Setup-and-Hold-Time )

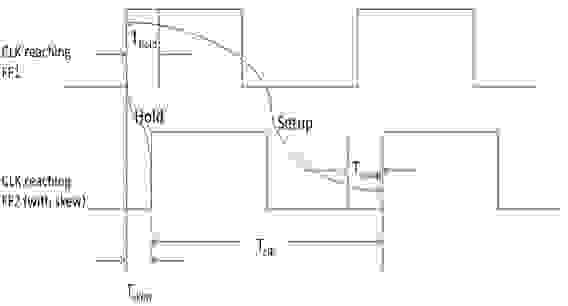

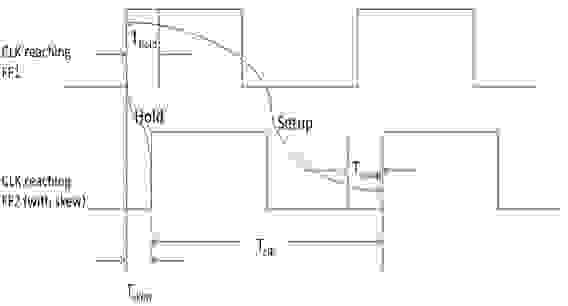

На картинке показаны формы прихода тактового импульса на триггеры FF1 и FF2, между которыми находится некая комбинационная схема, задерживающая сигнал.

Другими словами, FF1 — это триггерный источник сигнала, FF2 — приёмник, а сигнал через логику, в зависимости от некоторых входных условий, может доходить либо очень быстро, либо очень медленно.

Давайте посмотрим на обозначения: Tskew — перекос дерева часов, из-за которого такт на FF2 приходит позже, чем на FF1 на значение Tskew. Tc2q — это задержка сигнала внутри триггера между входом тактового сигнала и выходом данных.

Напомню, что в синхронных схемах источником всех переходных процессов является тактовый импульс, поэтому путь сигнала идет через тактовый вход к информационному выходу триггера, а затем через логику.

Tcomb — задержка сигнала в логике, Tclk — период тактового импульса, а Tsetup — характеристика запуска, определение которой (Setup) было дано выше.

Смотрим на картинку и видим, что максимальное время завершения переходных процессов на входе данных триггера должно удовлетворять следующему неравенству (1): Tc2q + Max(Tcomb) + Tsetup ≤ Tclk + Tskew (1)

Здесь Max(Tcomb) — максимально возможное значение Tcomb. Из формулы следует, что с нарушением неравенства можно бороться двумя способами: сдвинуть вправо момент поступления тактового импульса на FF2, изменив Tskew, или уменьшить задержку в логике Max(Tcomb).

Теперь попробуем разобраться с нарушениями Hold. Если нарушение Set, вообще говоря, относится к следующему такту, поскольку оно сравнивается с моментом прихода очередного тактового импульса, то нарушение Hold должно проверяться уже в текущем такте.

Как может произойти нарушение Hold? Судя по картинке, если сигнал с выхода FF1 пройдет через логику настолько быстро, что успевает испортить данные на входе FF2, мы получим нарушение в текущем такте.

Из чего следует, что сигнал с выхода FF1 не может поступить быстрее, чем за время Thold, скорректированное на Tskew. Получаем неравенство (2) Tc2q + Min(Tcomb) ≥ Thold + Tskew (2)

Здесь Min (Tcomb) — минимально возможное значение Tcomb. Из этой формулы также следует, что с нарушением можно бороться, перемещая Tskew или увеличивая задержки в логике Min(Tcomb).

Далее поговорим о том, как CAD борется с нарушениями.

Его основной задачей является повышение производительности проектируемой схемы.

Допустим, нам нужно добиться расчетной частоты 1 ГГц, несмотря на то, что в паре мест конструкции присутствует логическая задержка 1,2 нс.

САПР может попытаться сжать эту логику до 1 нс или исказить дерево тактовых импульсов таким образом, чтобы Tskew триггера-приемника был равен 200 пс.

Нечто подобное показано на картинке выше.

Поскольку логику обычно невозможно сжать, первое, что делает САПР, — это перестраивает дерево часов, тем самым устраняя нарушения Tsetup. Следует отметить, что по мере увеличения Tskew увеличивается и риск нарушения Hold. Как только желаемая частота будет достигнута, пришло время исправить удержание.

На этот раз CAD не трогает дерево часов, а использует второй прием — увеличение Min(Tcomb), т.е.

минимальных задержек в логике там, где есть нарушения Hold. Задержки можно увеличить очень просто, вставив элементы буфера.

Хотя дополнительные буферы, конечно, увеличивают потребление схемы.

Интересно, что увеличению задержек в схеме из-за нагрева, снижения электропитания, накопления дозы радиации или старения можно противодействовать снижением рабочей частоты микросхемы.

Ведь, как видно из формулы (1), при увеличении задержек Tclk необходимо уменьшить.

Но если задержки в схеме уменьшатся, за счет чрезмерного охлаждения или повышения напряжения питания, то нарушения Hold в микросхеме ничем исправить невозможно – микросхема просто перестанет работать, как следует из формулы (2).

Как же тогда микросхемы рассчитаны на низкие и даже сверхнизкие температуры? Чаще всего такие схемы устроены обычным образом, но заложен огромный резерв Холда.

Чем больше запас, тем больше микросхема может охлаждаться ниже расчетных температур, но насколько сильно покажет только эксперимент. Вероятность нарушений снижается и за счет отказа от перекошенного дерева часов в пользу наиболее ровного (чаще всего используется так называемое H-дерево) с сопутствующим снижением производительности.

И самый надежный способ — спроектировать асинхронные (SI, DI) схемы, полностью устойчивые к параметрическим отказам.

Ну и в заключение, причем здесь FPGA? Во-первых, на хабе нет раздела про ASIC. Во-вторых, хорошая FPGA рано или поздно перерастет в ASIC-проект. Ну и в-третьих, хотя возможности манипулирования Clock Skew в FPGA нивелированы, они все же существуют. Надеюсь, кому-то статья окажется полезной.

Теги: #sta #статический временной анализ #настройка #Hold #FPGA

-

Беккер, Гэри

19 Oct, 24 -

2-Я Встреча В Москве. Фотоотчет

19 Oct, 24 -

Gprs – Теория И Практика Применения

19 Oct, 24 -

Игры С Мозгом - А Точнее Шми

19 Oct, 24 -

Как Капчи Рассказали Об Уязвимости Яндекса

19 Oct, 24 -

Ключевые Тенденции Мошенничества В 2021 Году

19 Oct, 24