Всем привет! Меня зовут Максим, я работаю инженером в компании.

Компания делает серверы и другое оборудование на архитектуре POWER (какое именно и почему - другие расскажут позже), а пока хочу показать разрез серверной платы - это моя зона ответственности.

.

В общем, здесь будет что-то вроде рабочего журнала — мы вместе с коллегами будем публиковать истории о зарождении жизни в железах.

Сначала о сервере, а потом об остальном.

Как лучше всего установить здесь преобразователи напряжения?

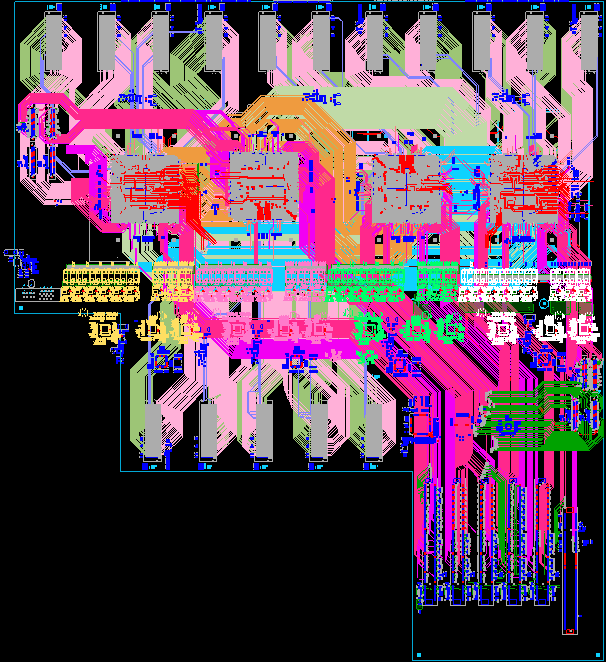

Скриншот выше — не результат галлюцинаций художника, творящего в стиле ПОП-АРТ, а материнская плата, на которой необходимо разместить четыре группы преобразователей напряжения — по одному на каждый процессор (на скриншоте желтые, розовые, ярко-зеленые и белые).

).

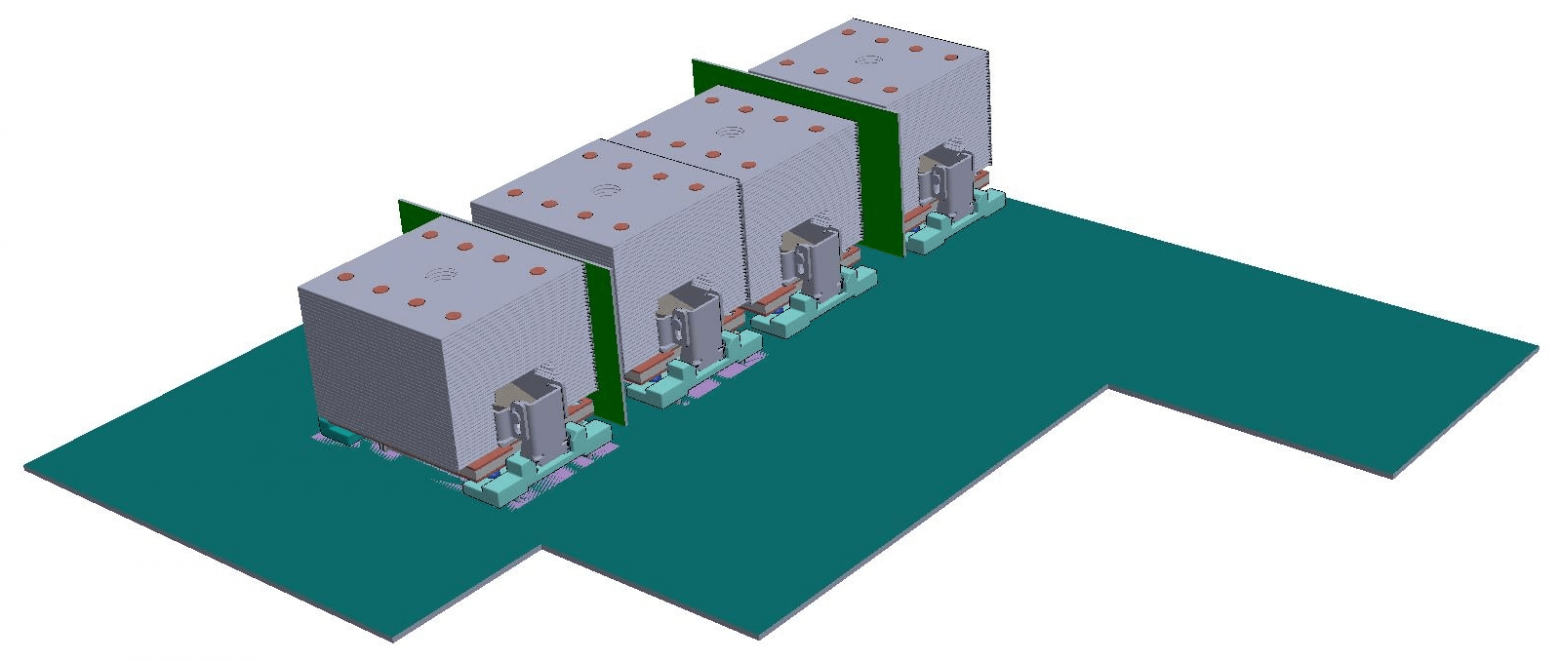

Сначала их хотели поставить на внешние платы, как на рисунке ниже:

Первоначальная идея размещения преобразователя

По первоначальному плану каждая плата должна была нести VRM для двух процессоров и связанных с ними модулей памяти.

Но изучив его, мы решили отказаться от этого варианта — дико большой ток требует большого разъема CardEdge, что существенно усложнит маршрутизацию межпроцессорных шин.

Теперь пытаемся установить VRM на материнскую плату.

Это тоже усложняет трассировку - теперь уже высокоскоростных шин, ведь придется менять расположение дорожек, чтобы обойти переходные отверстия, необходимые для подачи напряжения на процессоры от преобразователей.

А дырочек нужно много! Процессоры и модули памяти требуют большого тока, и плотность этого тока, проходящего через переходные отверстия, должна быть минимизирована.

Если вы сэкономите на количестве переходных отверстий, это приведет к их перегреву (из-за высокой плотности тока) и, в конечном итоге, к деградации, пока они полностью не сгорят.

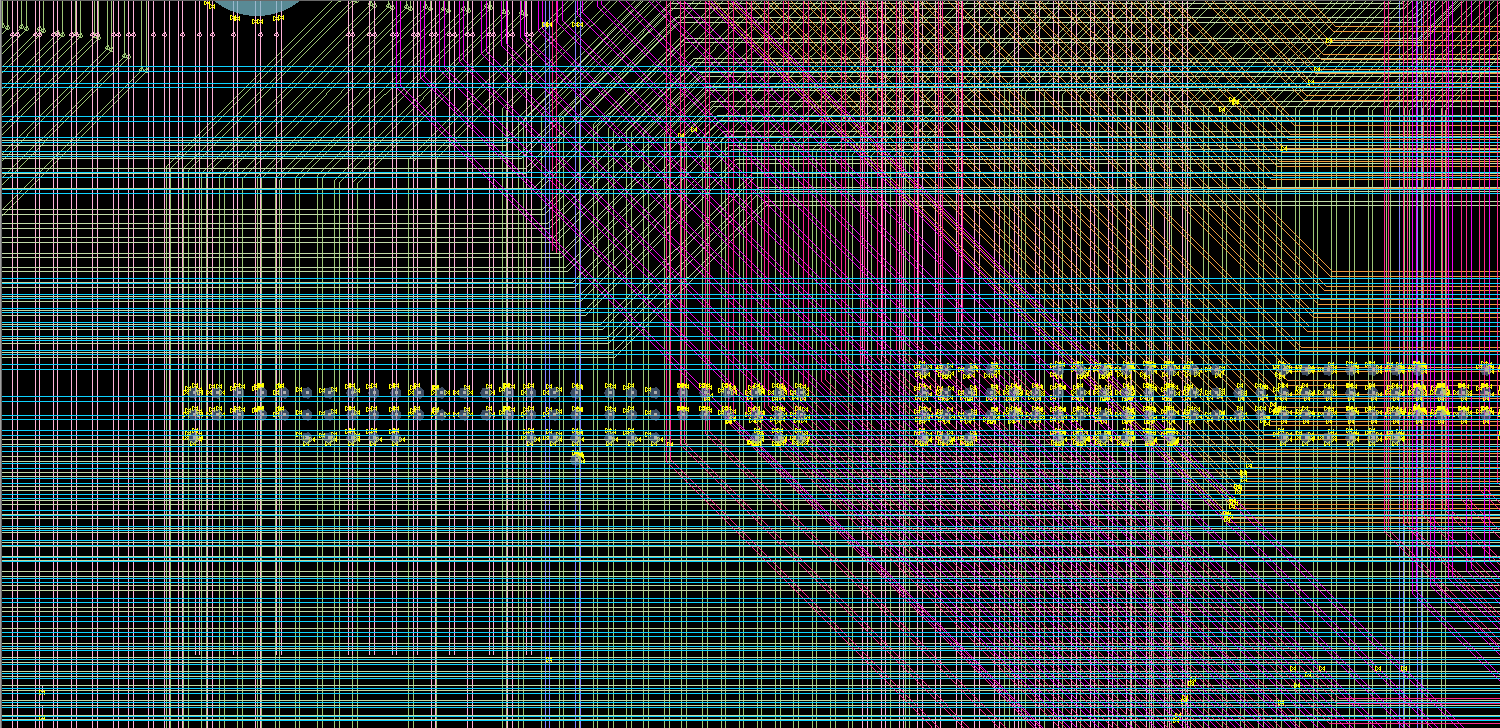

Почти скриншот из ТРОН 2.0, хочется плакать кровавыми слезами.

Желтым цветом выделены отверстия — по сути, это подсветка ошибок из-за пересечения с ними дорожек различных шин.

Все эти пути нужно отвести в сторону.

Вообще сложность проекта в рамках моих задач заключается в том, что мне приходится разводить на плате, помимо сильноточных шин питания (до 250 А!), множество высокоскоростных шин — PCIe Gen3 (8 Гбит/с), DMI (9,6 Гбит/с, Differential Memory Interface, шина для подключения буферных микросхем памяти Centaur), межпроцессорные шины A-bus (6,4 Гбит/с, SMP link).

Несколько слов об A-Bus и Кентаврах A-Bus — одна из двух шин межпроцессорной связи для POWER8. Что касается «Кентавров», то IBM при выпуске POWER8 решила вынести буфер памяти в отдельный чип.

Там же реализован кэш L4, отвечает за всю логику и т.д., спроектированную в т.ч.

для безболезненного перехода с DDR3 на DDR4. Если вам интересно, можете написать о них отдельно.

Компонентов тоже немало — 4 процессора, 16 слотов для райзеров памяти DDR4, всего 14 слотов для PCIe (из них 8 — НаноПитч , а 6 — обычные разъемы для карт расширения), и установка очень плотная.

Первый экран дает достаточное представление о масштабе беды — это упрощенное изображение с изрядным количеством скрытых от отображения компонентов, чтобы не перегружать и без того плотную картину.

Область между двумя процессорами.

Между ними можно было проложить пути очень плотно.

Много высокоскоростных интерфейсов — много ограничений.

Необходимо строго соблюдать требования к трассировке – максимальная длина, статические и динамические фазы в дифференциальных парах; расстояние между дифференциальными парами; максимальная дисперсия длины в группе, характеристическое сопротивление и т. д. Это, в свою очередь, накладывает ограничения на маршруты шин вдоль платы, выбор материала печатной платы (материал с низкими потерями), количество слоев и т. д. Теперь у нас есть стек из 28 слоев — из них 4 слоя отведены под силовые шины, для увеличения площади силовых полигонов — это позволяет минимизировать IR drop (падение напряжения на проводнике).

Мы хотим не превышать это количество слоев, и я думаю, нам следует это сделать.

Почему ИК-падение вредно? Явление падения ИК-излучения, помимо реальных проблем с провалами напряжения компонентов, также тесно связано с рассеянием тепла.

Чем больше падение напряжения на резистивной линии, тем больше энергии уходит на нагрев и перегрев.

В целом мы стремимся уменьшить этот эффект за счет геометрии.

Это не плохо статья насчет ИК падения и анализа явления в зависимости от формы проводника - ясно видно, что на широких участках питания эффект снижается.

В общем, это рабочие дни.

Привыкаешь рассматривать такие схемы пристальным взглядом — и тогда замечаешь, что они даже по-своему художественны, словно смесь линий и цветовых пятен различных форм и оттенков.

А трассировка такого масштаба – это само по себе искусство.

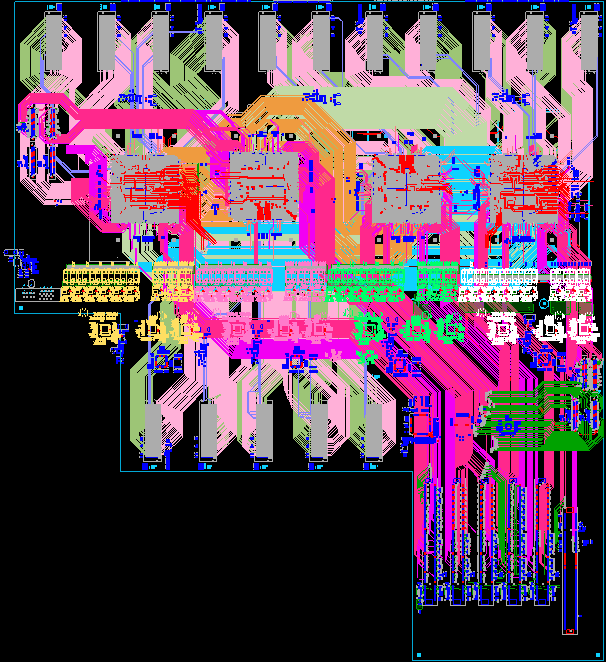

Наконец, я хочу показать еще один экран, скрывающий всю историю:

Это не приход Ктулху из морских глубин.

Из-за расположения разъемов памяти один процессор пришлось повернуть на 180 градусов.

Почему разъемы памяти нельзя было расположить по-другому? Это уже история следующей серии и я не буду в ней героем.

Теги: #серверы #проектирование #платы #трассировка #FPGA #программирование микроконтроллеров

-

Лаосский Язык

19 Oct, 24 -

Гершко, Аврам

19 Oct, 24 -

Геймификация Ит-Обучения

19 Oct, 24 -

Как Вести Себя С Трудными Людьми

19 Oct, 24 -

Домашняя Гэс

19 Oct, 24