Что-то я не могу кратко выразить свою мысль.

Осенью прошлого года у меня возникло желание рассказать подробнее об освоенной мной архитектуре PSoC, в результате чего появилась серия статей о ней.

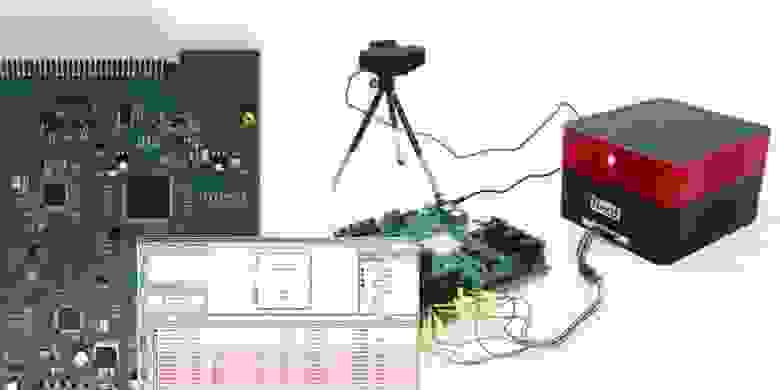

Сейчас участвую в подготовке оборудования для нашего комплекса удаленной отладки Redd, о котором шла речь Здесь , а накопленный опыт хочу выплеснуть в текстовом виде.

Пока не уверен, но мне кажется, что опять будет не одна статья, а серия.

Во-первых, таким образом я буду документировать разработанные приемы разработки, которые могут быть кому-то полезны как при работе с комплексом, так и вообще, а во-вторых, концепция еще новая, не до конца устоявшаяся.

Возможно, в процессе обсуждения статей появятся какие-то комментарии, из которых можно будет что-то почерпнуть, чтобы расширить (или даже изменить) ее.

Итак, давайте начнем.

Длинное введение

Я не очень люблю теоретизировать, предпочитаю сразу изложить какие-то практические вещи.Но в начале первой статьи без длинного вступления никуда.

В ней я обосноваю текущий подход к развитию.

И все будет крутиться вокруг одного: человеко-час — очень дорогой ресурс.

И дело не только во времени, отведенном на проект. Он физически дорогой.

Если оно потрачено на разработку конечного продукта, ну что поделаешь, без него не обойтись.

А вот когда он тратится на вспомогательную работу, это, на мой взгляд, плохо.

Помню, я поспорил с одним разработчиком, который сказал, что, делая прототипы самостоятельно, он сэкономит деньги своей компании.

Я аргументировал это тем, что изготовление займет около 3 дней.

Это 24 человеко-часа.

Берем его зарплату за эти часы, добавляем социальный налог, который «платит работодатель», а также аренду офиса за эти часы.

И мы с удивлением видим, что, заказывая платы на стороне, вы можете снизить затраты.

Но это только я, я преувеличиваю.

В общем, если можно избежать затрат на рабочую силу, их следует избегать.

В чем заключается разработка «прошивки» для комплекса Redd? Это вспомогательная работа.

Основной проект будет жить долго и счастливо, его нужно делать максимально качественно, с отличной оптимизацией и т. д. А вот тратить время и силы на вспомогательные вещи, которые уйдут в архив после завершения разработки, расточительно.

Именно с учетом этого принципа было разработано оборудование Redd. Все функции по возможности реализованы стандартно.

Шины SPI, I2C и UART реализованы на стандартных чипах FTDI и программируются через стандартные драйверы, без каких-либо наворотов.

Управление реле реализовано в формате виртуального COM-порта.

Его можно улучшить, но, по крайней мере, сделано все, чтобы такого желания не возникло.

В целом всё стандартно, по возможности реализовано стандартно.

От проекта к проекту разработчикам просто приходится быстро писать стандартный код ПК для доступа к этим шинам.

Технология разработки на C++ должна быть очевидна тем, кто разрабатывает программы для микроконтроллеров (о некоторых технических подробностях мы поговорим в другой статье).

Но ПЛИС стоит особняком в комплексе.

Он добавлен в систему в случаях, когда необходимо реализовать какие-либо нестандартные протоколы с высокими требованиями к производительности.

Если таковые требуются, то придется делать для них «прошивку».

Именно о программировании FPGA хотелось бы поговорить конкретно, имея в виду ту же цель — сократить время разработки вспомогательных вещей.

Чтобы не запутать читателя, сформулирую мысль в рамке:

Нет необходимости разрабатывать FPGA в каждом проекте.Если для работы с целевым устройством достаточно контроллеров шины, подключенных непосредственно к центральному процессору, стоит их использовать.

В комплекс добавлена ПЛИС для реализации нестандартных протоколов.

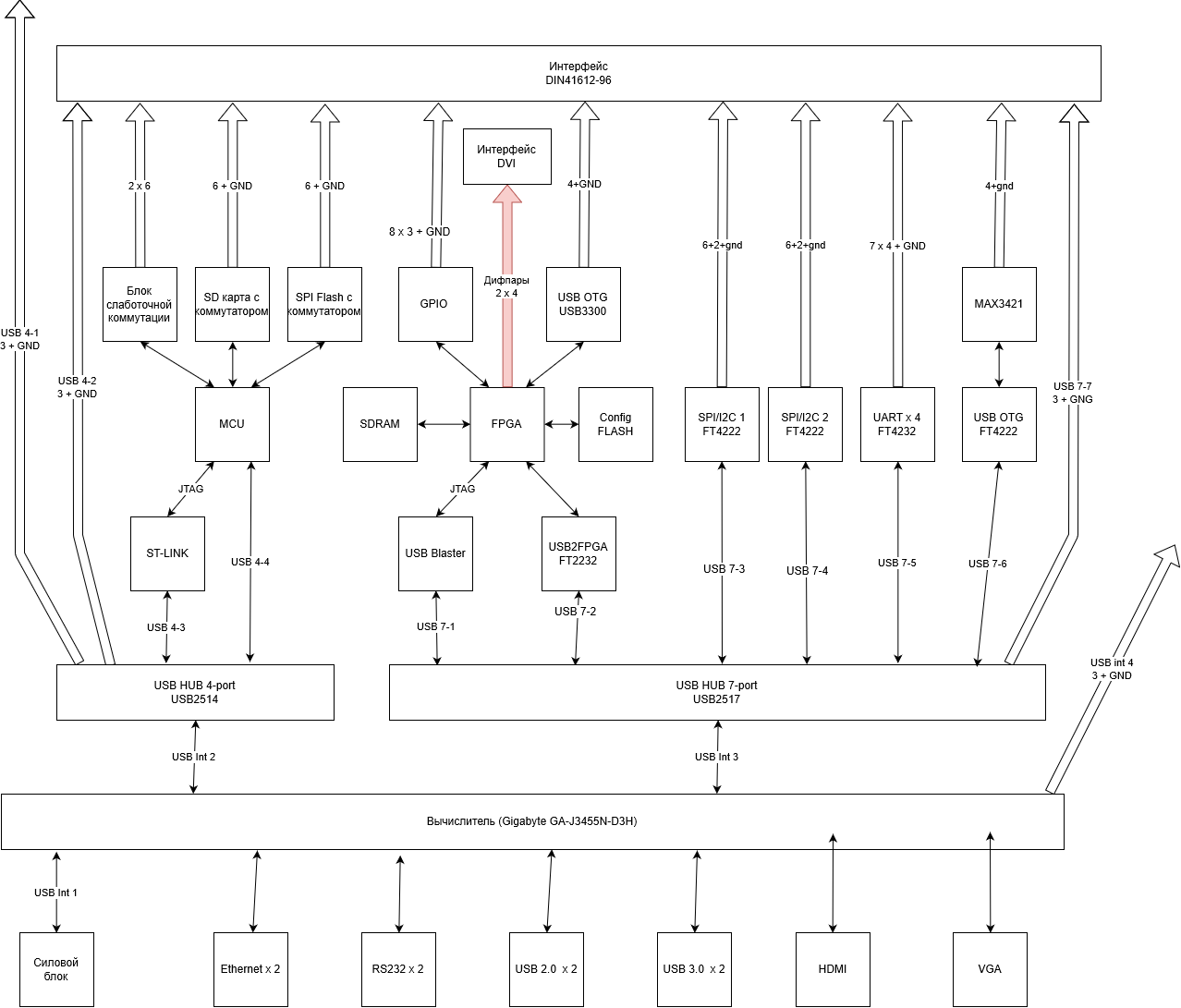

Структурная схема комплекса

Давайте посмотрим на структурную схему комплекса.

Внизу схемы есть «калькулятор».

Фактически это стандартный ПК с ОС Linux. Разработчики могут писать обычные программы на C, C++, Python и т. д., которые будут выполняться компьютером.

В правой верхней части расположены стандартные порты для штатных шин.

Слева — переключатель штатных устройств (SPI Flash, SD-карта и несколько слаботочных твердотельных реле, способных, например, имитировать нажатие кнопок).

А в центре находится именно та часть, работу с которой мы планируем рассмотреть в этой серии статей.

Ее сердцем является ПЛИС класса FPGA, от которой к выходу выходят прямые линии (могут использоваться как дифференциальные пары или обычные небуферизованные линии), линии GPIO с заданным логическим уровнем, а также шина USB 2.0, реализованная через ULPI-чип.

разъем.

Продолжение вступления о подходе к программированию ПЛИС.

При разработке высокопроизводительной логики управления для FPGA Его Величество конечный автомат обычно играет первую скрипку.

Именно на автоматах можно реализовать быстродействующую, но сложную логику.

Но с другой стороны, автомат разрабатывается медленнее, чем программа для процессора, и его модификация — это другой процесс.

Существуют системы, упрощающие разработку и обслуживание машин.

Один из них даже разработала наша компания, но все равно процесс проектирования любой сложной логики не быстрый.

Когда разрабатываемая система является конечным продуктом, имеет смысл подготовить, спроектировать хорошую управляющую машину и потратить время на ее реализацию.

Но как уже отмечалось, разработка для Редда — это вспомогательная работа.

Он призван облегчить процесс, а не усложнить его.

Поэтому было решено, что основной разработкой будут не автоматы, а процессорные системы.

Но с другой стороны, при разработке «железа» был отвергнут самый модный сегодня вариант — ПЛИС с ARM-ядром.

Во-первых, из соображений цены.

Плата разработки на базе SoC Cyclone V стоит умеренно дорого, но, как ни странно, отдельная ПЛИС стоит гораздо дороже.

Скорее всего, цена на макетные платы занижена, чтобы заманить разработчиков использовать данные ПЛИС, и платы продаются поштучно.

Для серии придется брать отдельные микросхемы.

Но кроме этого есть еще и «во-вторых».

Во-вторых, когда я проводил эксперименты с SoC Cyclone V, выяснилось, что эта процессорная система не так уж и производительна, когда речь идет об одиночных обращениях к портам.

Пакетные - да, там работа идет быстро.

А в случае одиночных вызовов при тактовой частоте ядра процессора 925 МГц можно получить обращения к портам на частоте одного мегагерца.

Предлагаю всем вызывать стандартную функцию размещения данных в FIFO блока UART, проверяющую заполненность очереди, но вызывать ее тогда, когда очередь заведомо пуста, то есть ничего не мешает операциям.

Моя производительность колебалась от миллиона до пятисот тысяч вызовов в секунду (конечно, работа с памятью была на нормальной скорости, все кэши были настроены, даже та версия функции, которая не проверяла FIFO на переполненность, работала быстрее, просто так обсуждаемая функция содержит много смешанной записи и чтения из портов).

Это ФИФО! На самом деле FIFO был придуман для того, чтобы закидывать туда данные и забывать их! Быстро уходи! И не с производительностью, менее одной мегаоперации в секунду при тактовой частоте процессора 925 МГц.

Во всем виновата задержка.

Между ядром процессора и аппаратным обеспечением имеется три или более мостов.

Причем скорость доступа к портам зависит от контекста (несколько записей подряд пройдут быстро, но первое чтение остановит процесс до полной выгрузки кэшированных данных; слишком много записей подряд тоже будет тормозить, так как буферы записи будут исчерпаны).

Наконец, проверка накопленных в отладочном буфере трассировок показала, что архитектура Кора А один и тот же участок может выполняться за разное количество тактов из-за сложной системы кэширования.

В общей сложности, учитывая все эти факторы (цена, просадки производительности при работе с оборудованием, нестабильность скорости доступа к оборудованию, общая зависимость от контекста), было принято решение не устанавливать такую микросхему в комплекс.

?Эксперименты с Cypress PSoC показали, что ядро есть Кортекс М дает более предсказуемые и повторяемые результаты, но логическая емкость и максимальная рабочая частота этих контроллеров не соответствовали спецификациям, поэтому от них тоже отказались.

Было решено установить недорогую универсальную FPGA Cyclone IV и рекомендовать использование синтезируемого процессорного ядра NIOS II. Ну, а при необходимости вести разработку любыми другими методами (автоматами, жесткой логикой и т.п.

).

Отдельно упомяну (и даже выделю этот абзац), что основной процессор комплекса — х86 (х64).Именно он является центральным процессором системы.

Именно на нем реализована основная логика комплекса.

Процессорная система, о которой пойдет речь ниже, просто предназначена для обеспечения логики работы оборудования, «вшитого» в ПЛИС.

Причем такое оборудование реализуется только в том случае, если у разработчиков недостаточно стандартных модулей, подключаемых непосредственно к центральному процессору.

Процесс разработки и отладки прошивки

Если комплекс Redd работает под ОС Linux, это не означает, что разработка должна вестись именно в этой ОС.Redd — удаленный исполнитель, и разработку следует вести на собственной ВМ, вне зависимости от того, какая ОС на ней работает. Проще тем, у кого Linux, но тем, кто привык к Windows (когда-то мне очень не нравилась WIN 3.1, но на работе меня заставили, и где-то во времена WIN95 OSR2 я к ней привык, а сейчас бороться с этим бесполезно, легче принять) , в нем можно продолжать развиваться.

Поскольку дружбы с Linux у меня не сложилось, я не буду давать пошаговую инструкцию по настройке среды под него, а ограничусь общими словами.

Тем, кто работает с этой ОС, этого будет достаточно, а остальным.

Поверьте, проще обратиться к сисадминам.

В итоге я сделал именно это.

Но тем не менее.

Вам следует загрузить и установить Quartus Prime Programmer and Tools той же версии, что и ваша среда разработки.

Если версии не совпадают, могут быть сюрпризы.

Я провел весь вечер, пытаясь осознать этот факт. Поэтому просто скачайте инструмент той же версии, что и среда разработки.

После установки войдите в каталог, в который была установлена программа, подкаталог bin. В общем, самым важным файлом должен быть jtagconfig. Если запустить без аргументов (от меня, кстати, настойчиво требовали ввести .

/jtagconfig и только так), то отобразится список имеющихся в системе программистов и подключенных к ним ПЛИС.

Там должен быть USB Blaster. И первая проблема, которую подкидывает система - не хватает прав доступа для работы с USB. Как решить ее, не прибегая к sudo, описано здесь: radiotech.kz/threads/nastrojka-altera-usb-blaster-v-ubuntu-16-04.1244 Но здесь отображается список устройств.

Теперь вам следует написать:

после чего запустится сервер, доступный по сети из любого места../jtagconfig --enableremote <password>

Все бы ничего, но системный фаервол не позволит никому увидеть этот сервер.

А проверка в гугле показала, что каждый тип линукса (а их много) открывает порты в фаерволе по-своему, и нужно наколдовать столько заклинаний, что я предпочел обратиться к админам.

Также стоит учесть, что если jtagd не был прописан в автозапуске, то при открытии удаленного доступа вам будет сообщено, что невозможно установить пароль.

Чтобы этого не произошло, jtagd нужно запускать не с помощью самого jtagconfig, а до него.

В общем, шаманизм на шаманизме.

Позвольте мне просто констатировать эти моменты:

- Входящий порт 1309 должен быть открыт в системе.

Не до конца понимаю какой протокол, для надежности можно открыть и tcp и udp;

- при запуске jtagconfig без аргументов должны отображаться USB Blaster и подключенная к нему ПЛИС, а не сообщение об ошибке;

- Прежде чем открыть удаленную работу, jtagd должен быть запущен с достаточными правами.

Если jtagd уже был запущен с недостаточными правами, его процесс необходимо завершить перед новым запуском, иначе новый запуск не состоится;

- фактический удаленный доступ открывается строкой

jtagconfig --enableremote <password>

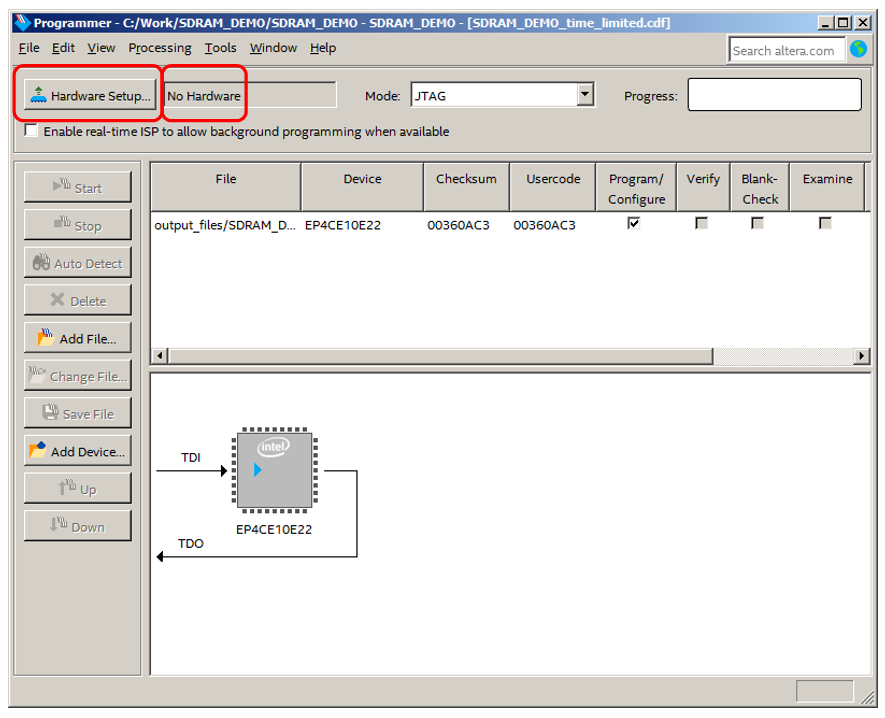

Поэтому я описал пакетный вариант. Когда все эти тезисы выполнены (а за меня их сделали сисадмины), запускаем программатор на своей машине и видим сообщение об отсутствии оборудования.

Нажмите «Настройка оборудования»:

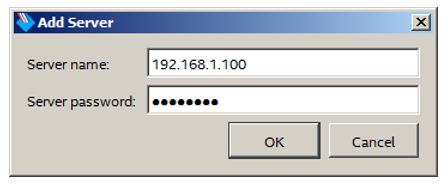

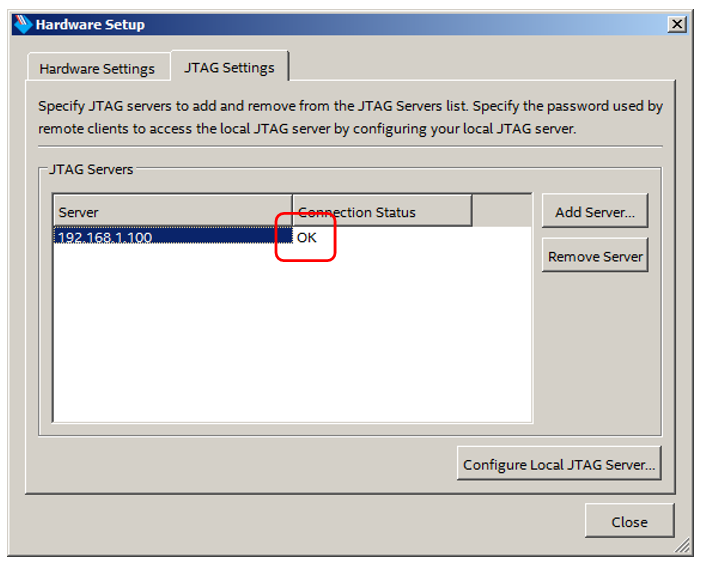

Перейдите на вкладку «Настройки JTAG» и нажмите «Добавить сервер»:

Введите сетевой адрес Redd (у меня 192.168.1.100) и пароль:

Убеждаемся, что соединение прошло успешно.

Три майских праздника я потратил на то, чтобы добиться этого, а потом все решили админы.

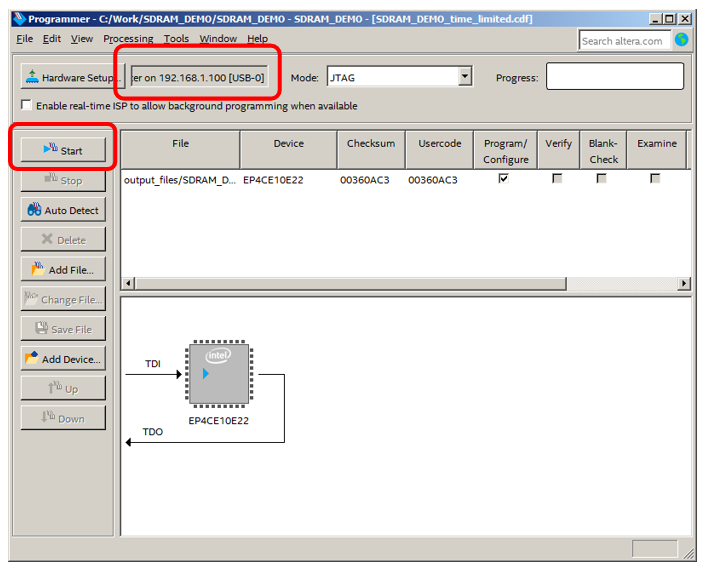

Перейдите на вкладку «Настройки оборудования», откройте раскрывающийся список и выберите там удаленный программатор:

Вот и все, теперь вы можете его использовать.

Кнопка «Пуск» разблокирована.

Первая "прошивка"

Хорошо.Чтобы статья имела реальную практическую ценность, давайте рассмотрим простейшую «прошивку», сделанную описанными выше способами.

Самое простое, что мне собственно пришлось реализовать для комплекса, — это тестирование чипа SDRAM. Давайте потренируемся на этом примере.

Есть ряд любительских ядер для поддержки SDRAM, но все они включены как-то хитро.

А учет всех хитростей трудоемкий.

Мы постараемся использовать готовые решения, которые можно будет вставить в вычислительную систему NIOS II, поэтому воспользуемся стандартным ядром контроллера SDRAM. Само ядро описано в документе Руководство пользователя встроенной периферии IP , и довольно много места в описании отведено сдвигу тактовых импульсов для SDRAM относительно тактовых импульсов ядра.

Приведены сложные теоретические расчеты и формулы, но конкретной информации, что делать, нет. Что делать, можно узнать из документа Использование SDRAM на плате Altera DE0 с Verilog Designs .

По мере продвижения анализа я буду применять знания из этого документа.

Разрабатывать буду в бесплатной версии Quartus Prime 17.0. Я на этом акцентирую внимание, так как при сборке мне сообщают, что в дальнейшем ядро Контроллер SDRAM будет исключен из бесплатной версии.

Если такое уже произошло в вашей среде разработки, никто не мешает вам скачать бесплатную 17-ю версию и установить ее на виртуальную машину.

Основную работу проводите там, где вы привыкли, а прошивка для Redd с SDRAM есть в версии 17. Ну это если использовать бесплатные варианты.

Никто еще не грозился выкинуть это из платных.

Но я отвлекся.

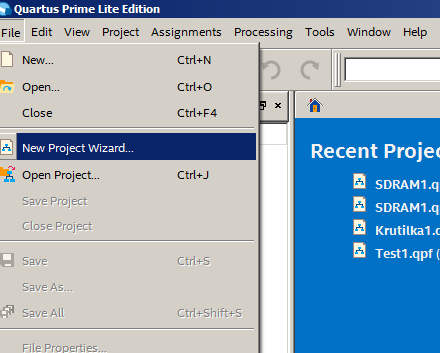

Создадим новый проект:

Назовем его SDRAM_DEMO. Название стоит запомнить: я собираюсь вести сверхбыструю разработку, поэтому на верхнем уровне должна быть сама процессорная система, без всяких Verilog-слоев.

А чтобы это произошло, имя процессорной системы должно будет совпадать с названием проекта.

Итак, давайте запомним это.

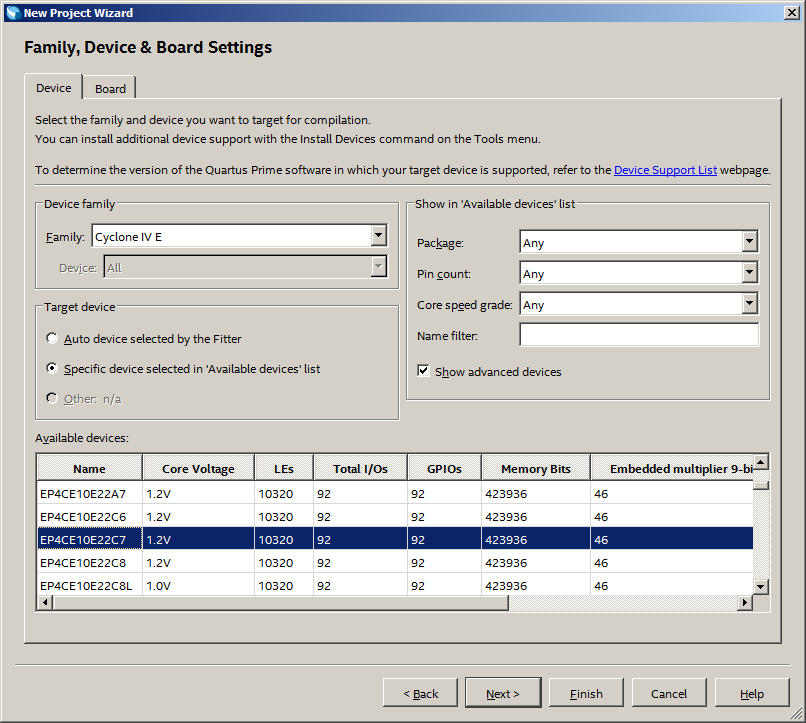

Согласившись в несколько шагов со значениями по умолчанию, доходим до выбора кристалла.

Выбираем EP4CE10E22C7, используемый в комплексе.

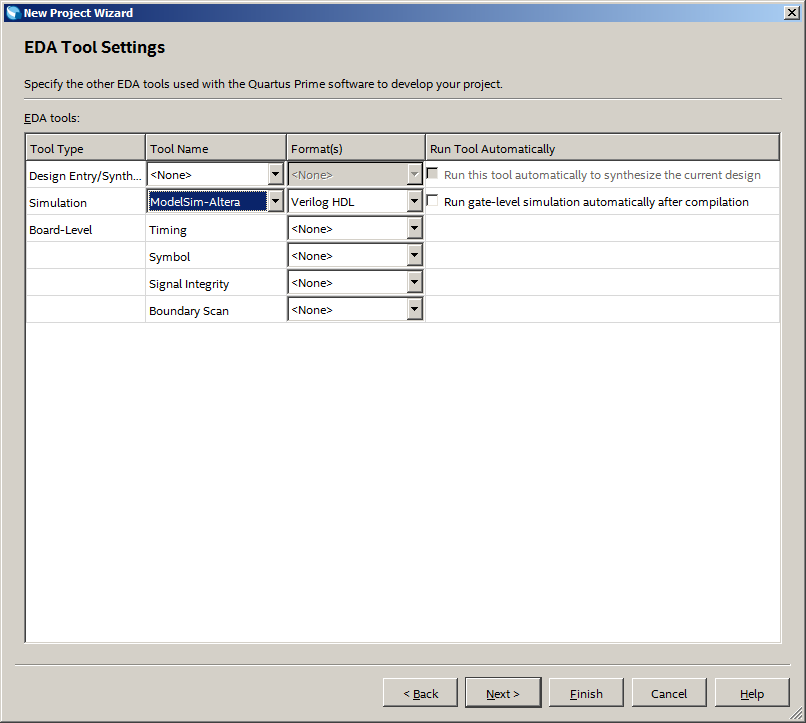

Следующим шагом по привычке выбираю моделирование в ModelSim-Altera. Мы не будем сегодня ничего моделировать, но что-нибудь может пригодиться.

Лучше выработать такую привычку и следовать ей:

Проект создан.

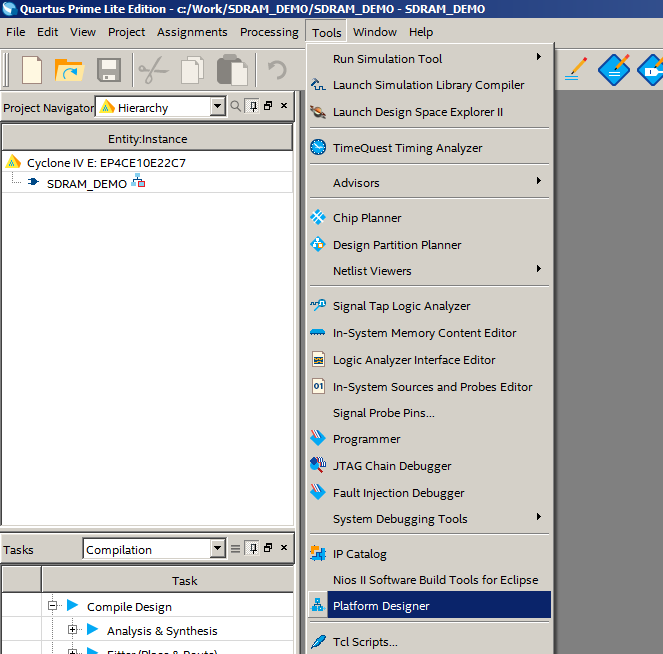

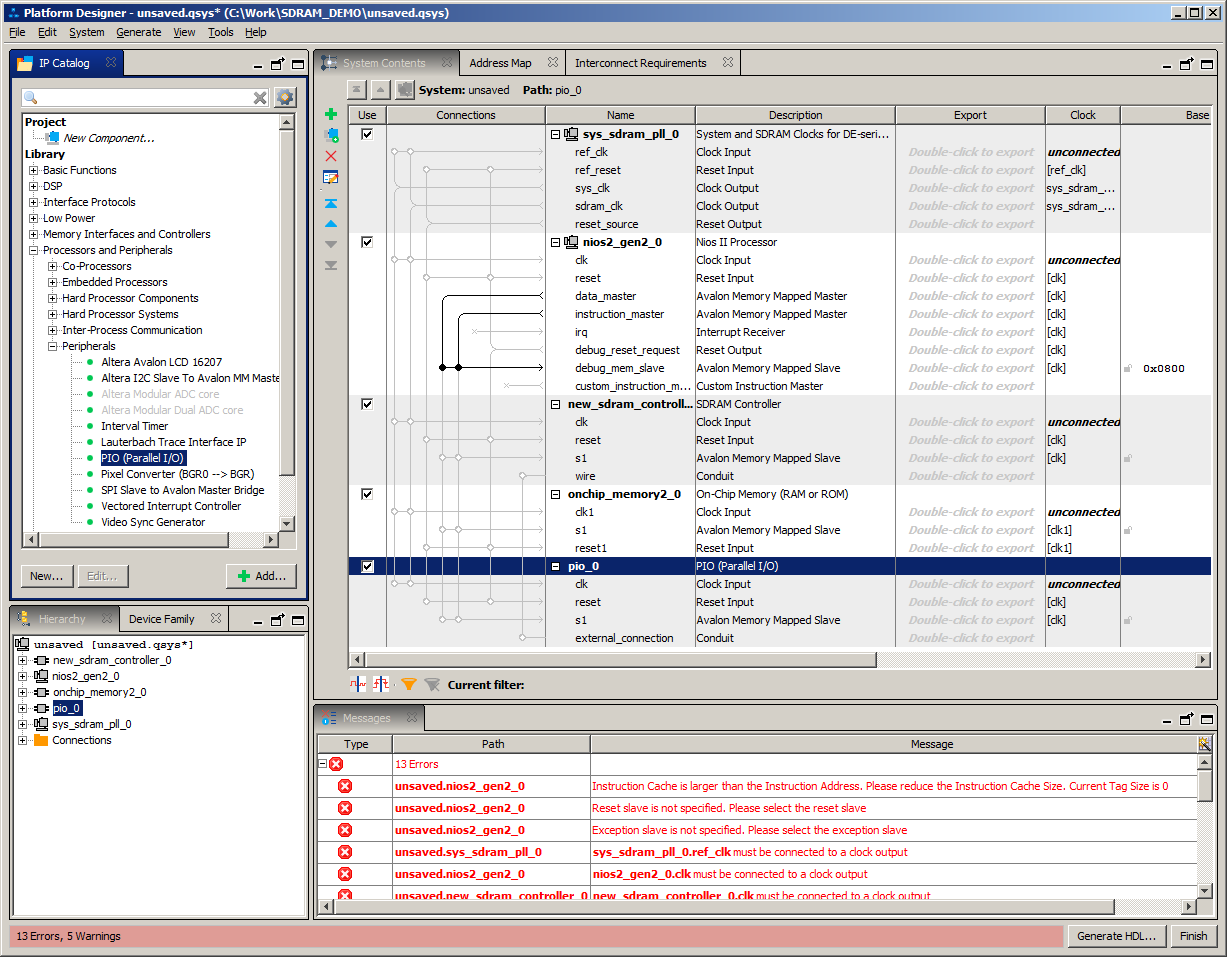

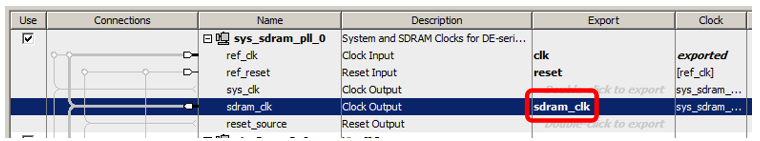

Сразу переходим к созданию процессорной системы (Инструменты-> Конструктор платформ):

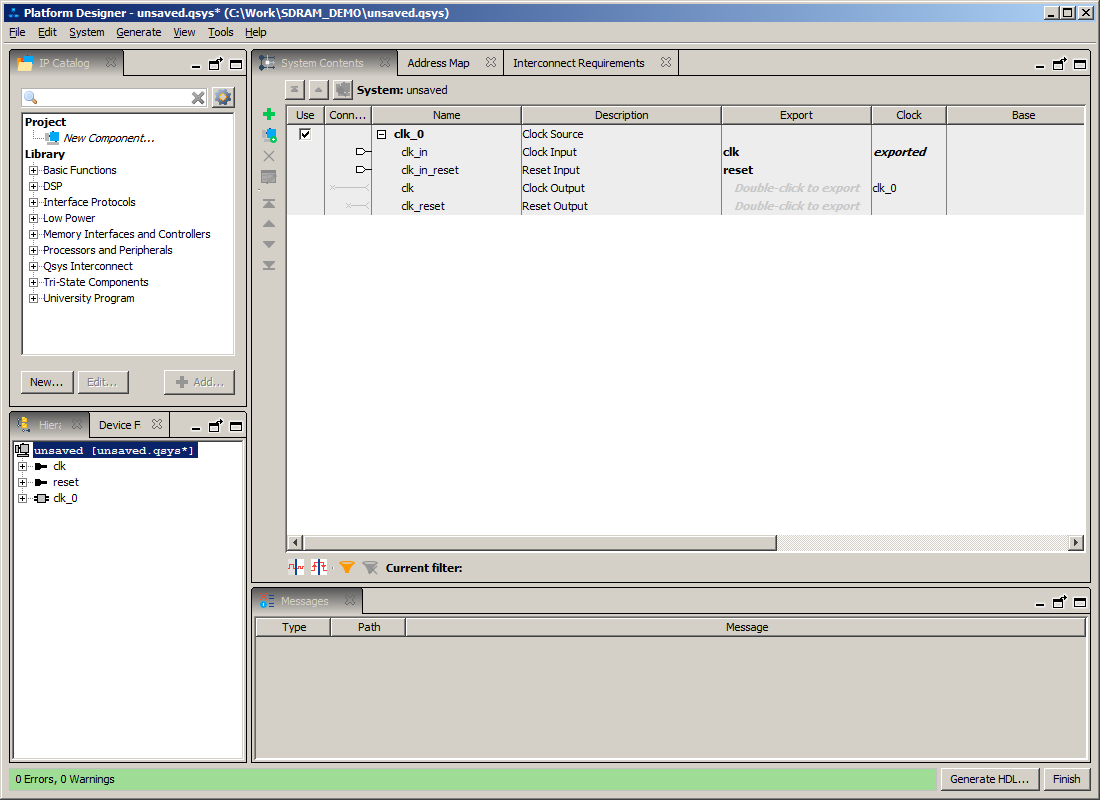

Мы создали систему, содержащую модуль часов и сброса:

Но как я уже упоминал, ядро SDRAM требует особой тактовой частоты.

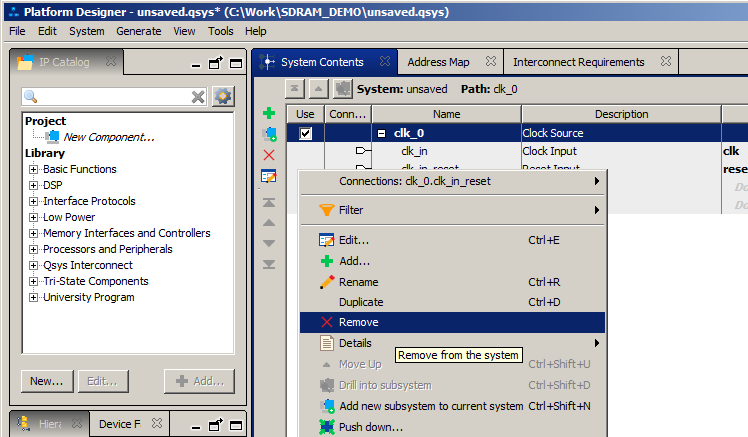

Поэтому безжалостно выкидываем стандартный модуль

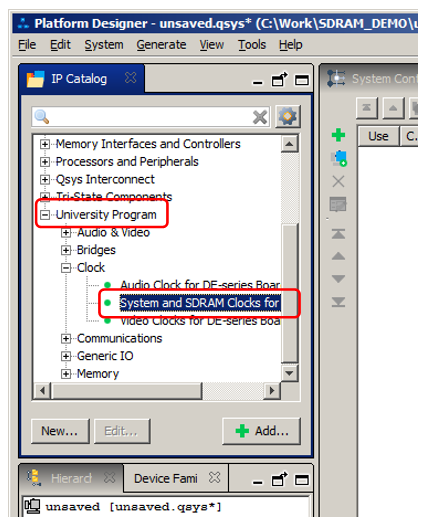

А вместо него добавляем блок Университетская программа-> Система и SDRAM Clock для плат серии DE:

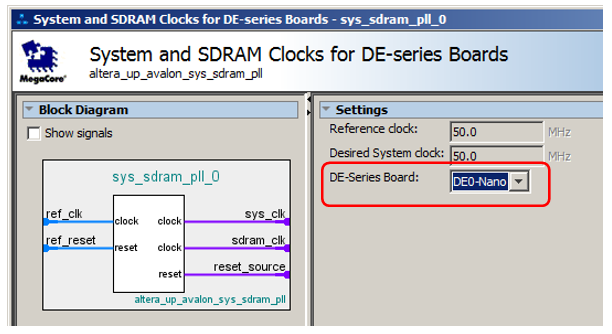

В свойствах выбираем DE0-Nano, так как вдохновение для схемы подключения SDRAM было почерпнуто именно из этой макетной платы:

Начинаем наполнять нашу процессорную систему.

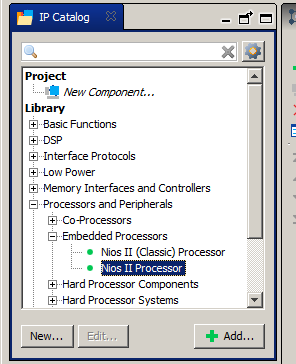

Конечно, первое, что вам следует сделать, это добавить само ядро процессора.

Пусть это будет «Процессор и периферия-> Встроенные процессоры-> Процессор NIOS II».

Мы пока не заполняем для него никаких свойств.

Мы просто нажимаем «Готово», хотя получаем ряд сообщений об ошибках.

В настоящее время не существует оборудования, которое позволит устранить эти ошибки.

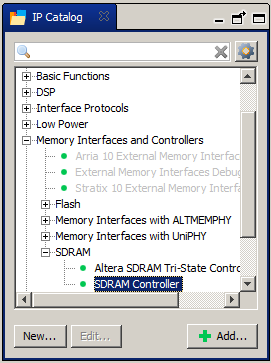

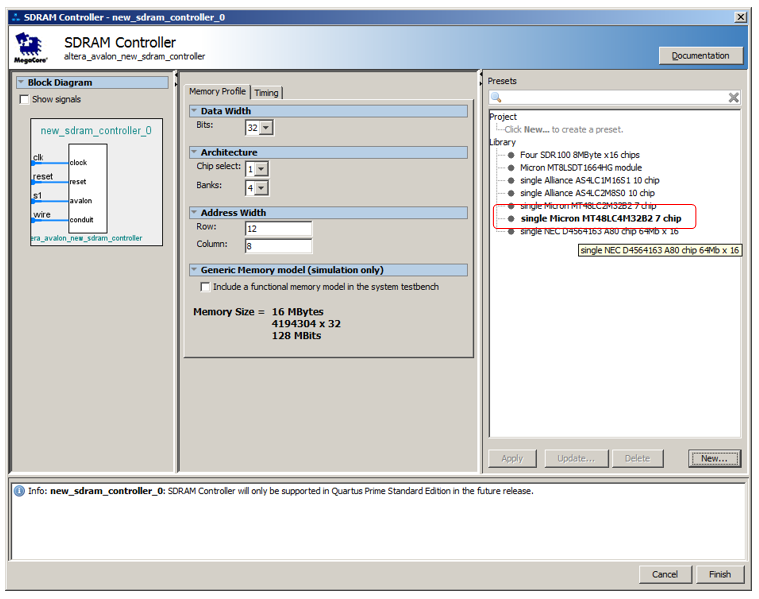

Теперь добавляем саму SDRAM. Интерфейсы и контроллеры памяти-> SDRAM-> Контроллер SDRAM.

Здесь нам придется немного остановиться во время заполнения свойств.

Выберите из списка ближайшую микросхему аналогичной организации и нажмите «Применить».

Его свойства попадают в поля «Профиль памяти»:

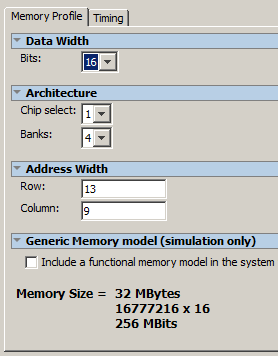

Теперь изменяем ширину шины данных на 16, количество адресных строк на 13, а количество столбцов на 9.

Временные пока не редактировал, возможно в будущем эта рекомендация будет изменена.

Процессорная система подразумевает программу.

Программа должна где-то храниться.

Мы будем тестировать чип SDRAM. На данный момент мы не можем ей доверять.

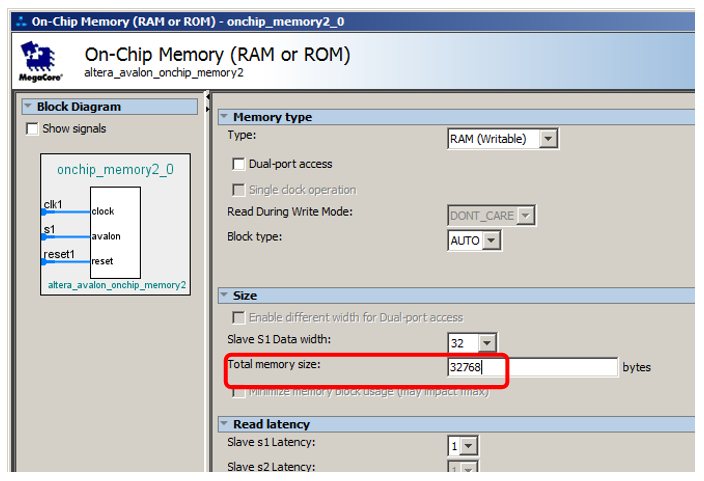

Поэтому для хранения программы добавим память на базе блочной оперативной памяти ПЛИС.

Основные функции-> Встроенная память-> Встроенная память (ОЗУ или ПЗУ):

Объем.

Ну, скажем, 32 килобайта.

Эту память надо откуда-то загрузить.

Чтобы это произошло, установите флажок «Включить файл инициализации не по умолчанию» и введите какое-нибудь значимое имя файла.

Допустим, прошивка.

hex:

Статья и так сложная, поэтому не будем ее перегружать.

Мы просто отобразим физический результат теста в виде строк PASS/FAIL (и увидим логический результат с помощью моей любимой JTAG-отладки).

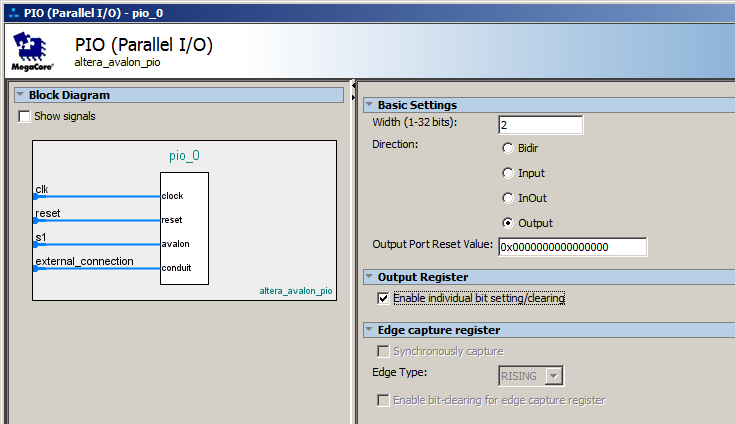

Для этого добавьте порт GPIO. Процессоры и периферийные устройства-> Периферийные устройства-> PIO (параллельный ввод-вывод):

В свойствах выставляем 2 бита, еще люблю поставить галочку для индивидуального управления битами.

Это тоже просто привычка.

В итоге у нас получилась вот такая система с кучей ошибок:

Начинаем их устранять.

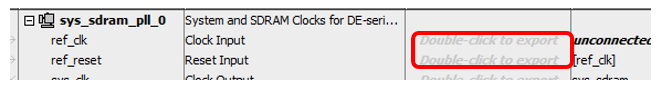

Для начала давайте разделим тактирование и сброс.

Входы блока тактирования и сброса необходимо выкинуть наружу.

Для этого есть поля с надписью «Двойной щелчок для экспорта»:

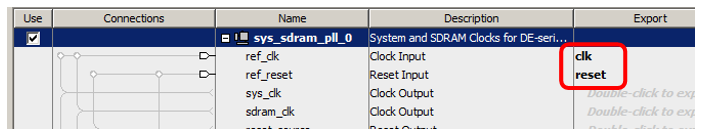

Щелкаем, но даем более-менее короткие имена.

Еще нужно выкинуть вывод тактовой частоты SDRAM:

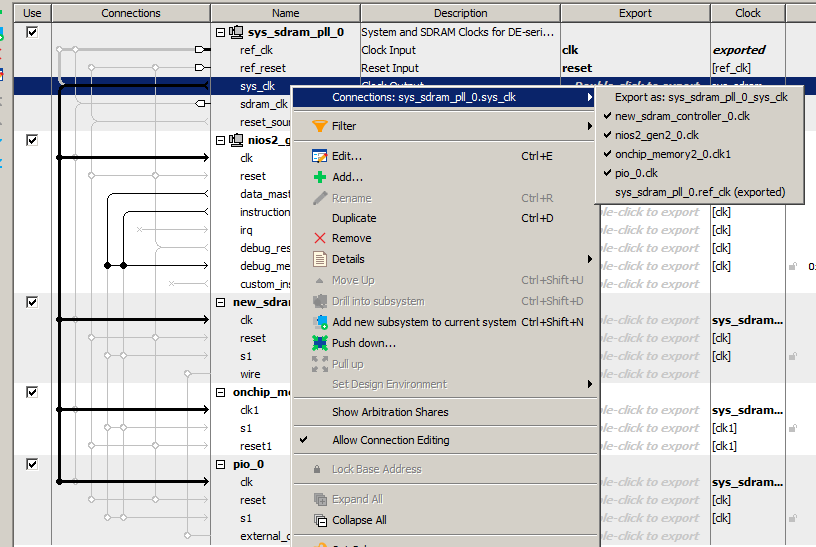

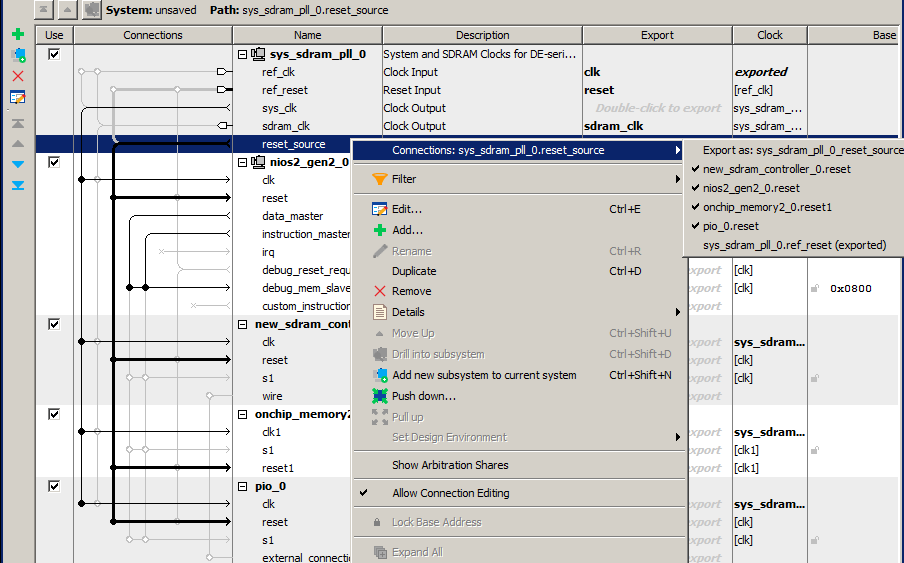

Теперь sys_clk направляется на все тактовые входы, а reset_source направляется на все линии сброса.

Вы можете аккуратно попадать мышкой по точкам, соединяющим соответствующие линии, а можете нацелиться на соответствующий выход, нажать правую кнопку мыши, а затем в выпадающем меню перейти в подменю Соединения и выбрать там соединения.

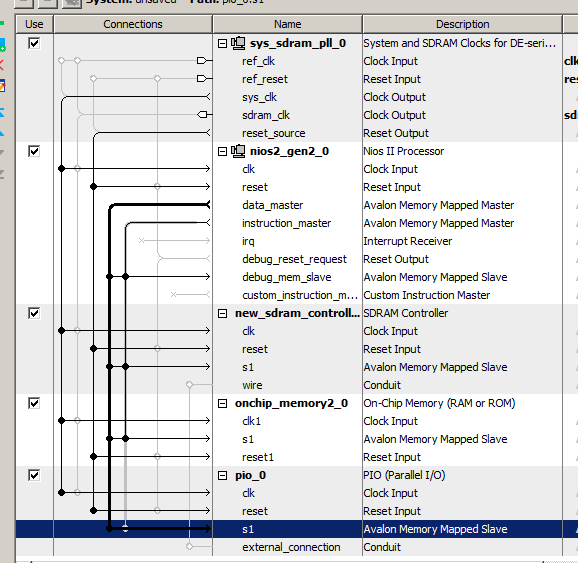

Далее связываем шины вместе.

Data Master подключаем ко всем шинам всех устройств, а Instruction Master практически ко всем из них.

Его не нужно подключать к шине PIO_0. Инструкции оттуда читаться точно не будут.

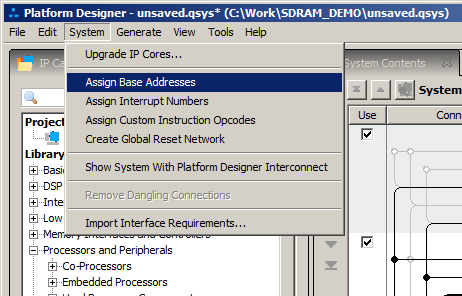

Теперь вы можете разрешать конфликты адресов.

Для этого выберите пункт меню Система-> Назначить базовые адреса:

И когда у нас есть адреса, мы можем назначить векторы.

Для этого зайдите в свойства ядра процессора (наведите на него курсор, нажмите правую кнопку Мыши и выберите пункт меню «Правка») и настройте там векторы для Onchip Memory. Просто выбираем в выпадающих списках этот тип памяти, цифры вставятся сами.

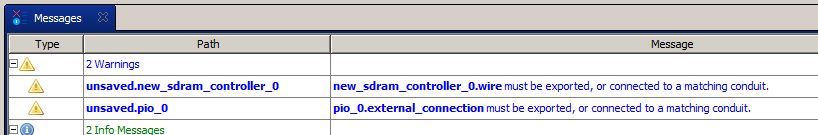

Ошибок не осталось.

Но осталось два предупреждения.

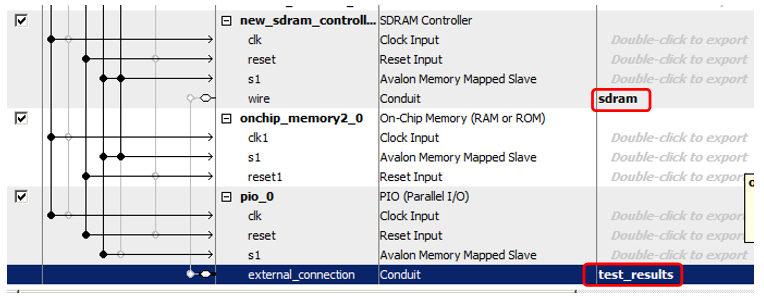

Я забыл экспортировать строки SDRAM и PIO.

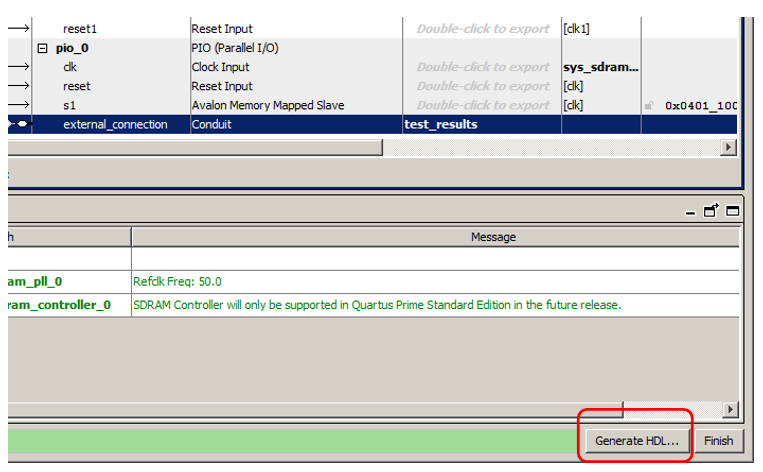

Как мы уже делали для блока сброса и тактирования, кликаем два раза по нужным ножкам и даем им максимально короткие (но понятные) имена:

Всё, больше никаких ошибок и предупреждений.

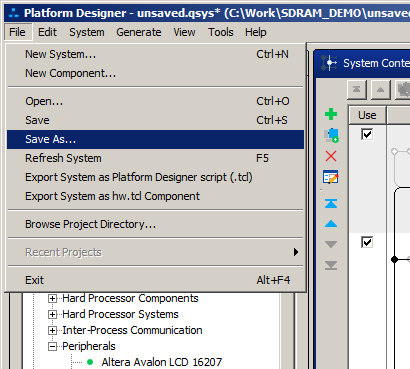

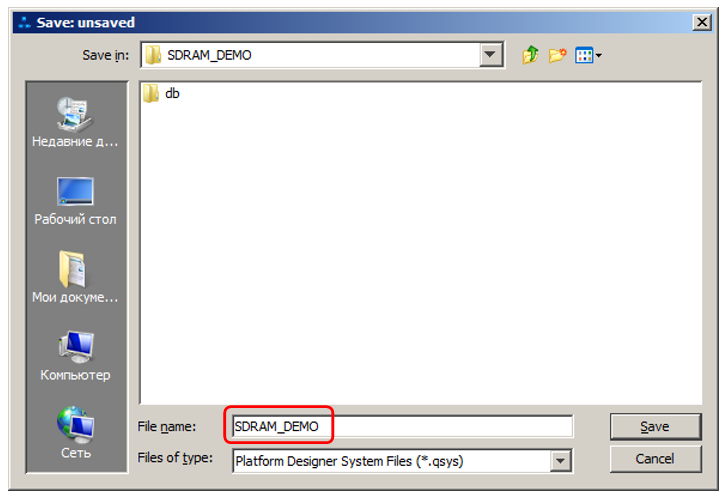

Сохраняем систему.

При этом имя должно совпадать с названием проекта, чтобы процессорная система стала элементом верхнего уровня в проекте.

Вы забыли, как оно называлось?

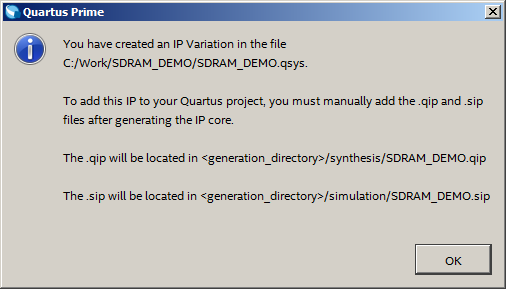

Что ж, нажимаем самую главную кнопку — генерировать HDL.

Всё, процессорная часть создана.

Нажмите «Готово».

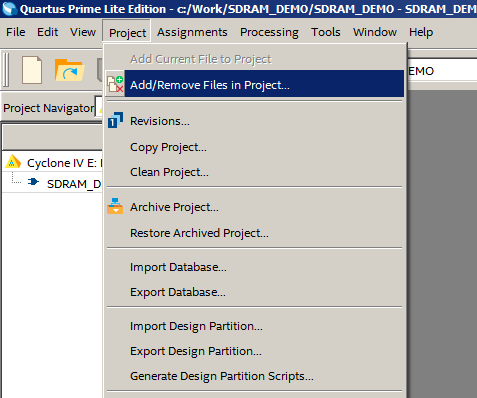

Напоминаем, что было бы неплохо добавить в проект вот эту процессорную систему:

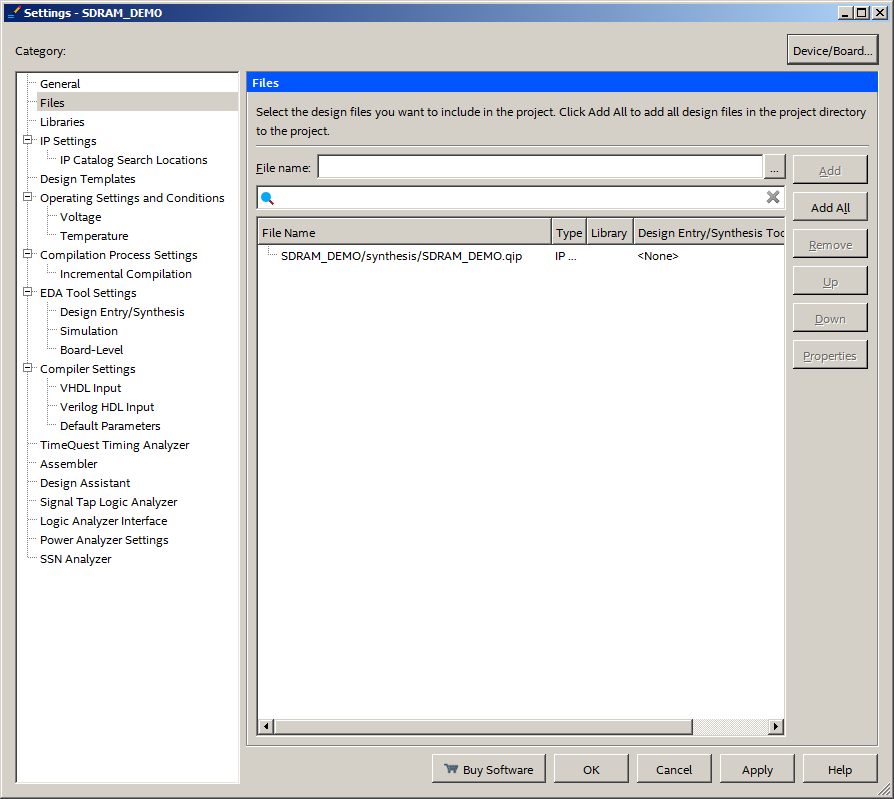

Добавлять:

И там с помощью кнопки Добавить добиваемся следующего изображения:

SIP-файл еще не создан.

Да и нам это в рамках данной статьи не нужно.

Уфф.

Первый шаг сделан.

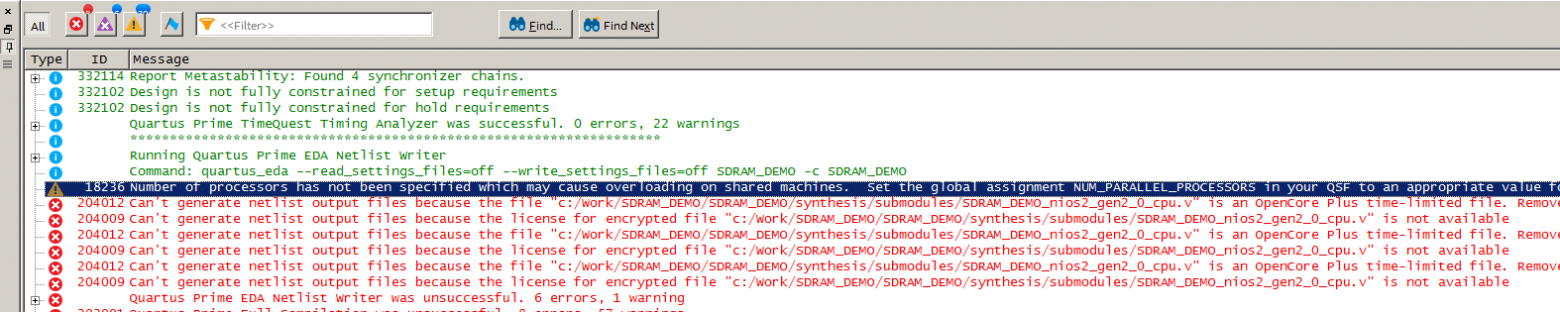

Выполняем черновую сборку проекта, чтобы система смогла разобраться в иерархии проекта и используемых ножках.

Ошибки компиляции не страшны.

Просто в бесплатной версии среды созданы ядра, которые работают только при подключенном JTAG-адаптере.

Но в комплексе Редд он всегда подключен, так как разведен на общей плате, то есть нам нечего бояться.

Поэтому мы игнорируем эти ошибки.

Теперь вернемся к описанию ядра SDRAM. Там написано, что линия CKE не используется и всегда подключена к блоку.

На самом деле в рамках комплекса ноги ПЛИС — это не просто дорогой, а ценный ресурс.

И было бы глупо отделять ножку, которая всегда есть в блоке (а на плате DE0-NANO она еще и не разведена).

Если бы был слой Verilog, там могла бы разорваться соответствующая цепочка, но я экономлю время (нервный смех, глядя на объем получившегося документа, но без сохранения он был бы еще больше).

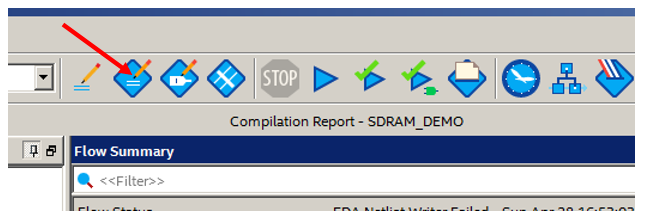

Поэтому слоя нет. Что я должен делать? Перейдем в Редактор заданий.

Именно в нем, поскольку Pin Planner, судя по описаниям, не имеет такого функционала.

Очередей там пока нет. Отлично.

Давайте создадим новый

Выберите этот значок:

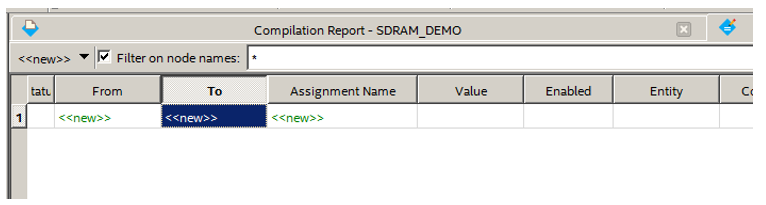

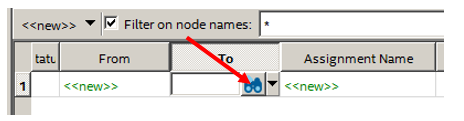

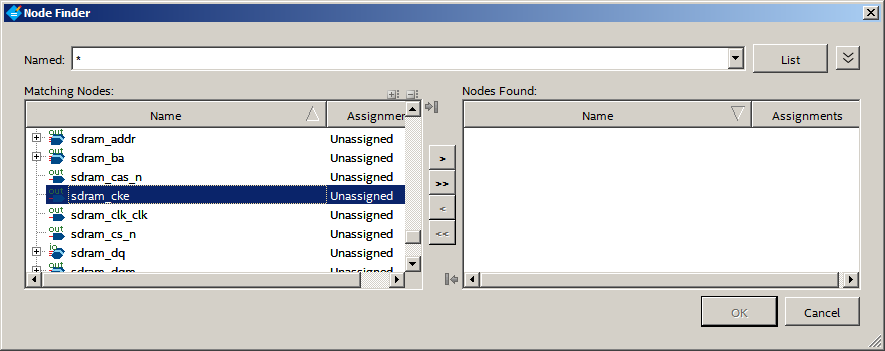

В поисковой системе нажмите List и в результатах поиска найдите наш CKE:

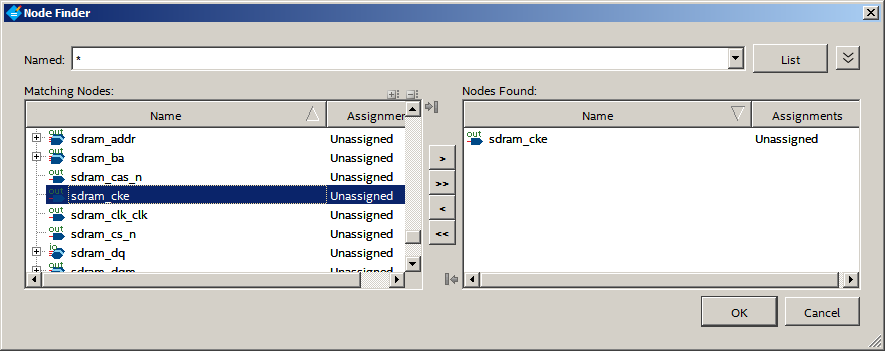

Добавьте его в правый столбец и нажмите «ОК».

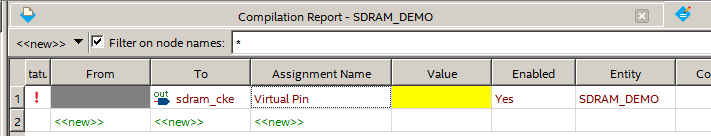

Получаем следующий список:

В желтом поле нажмите на раскрывающийся список и найдите Virtual Pin. Давайте выбирать.

Желтизна перешла в другую ячейку:

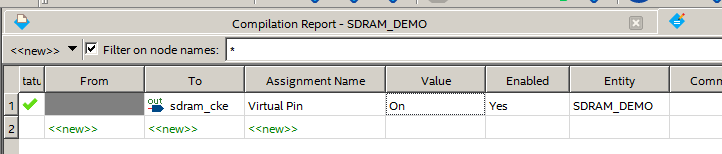

Там выбираем Вкл.

:

Всё, желтизны больше нет. И наша цепочка теперь помечена как виртуальная, а значит, ей не требуется физическая нога.

Поэтому мы не можем назначить его на физический выход ПЛИС.

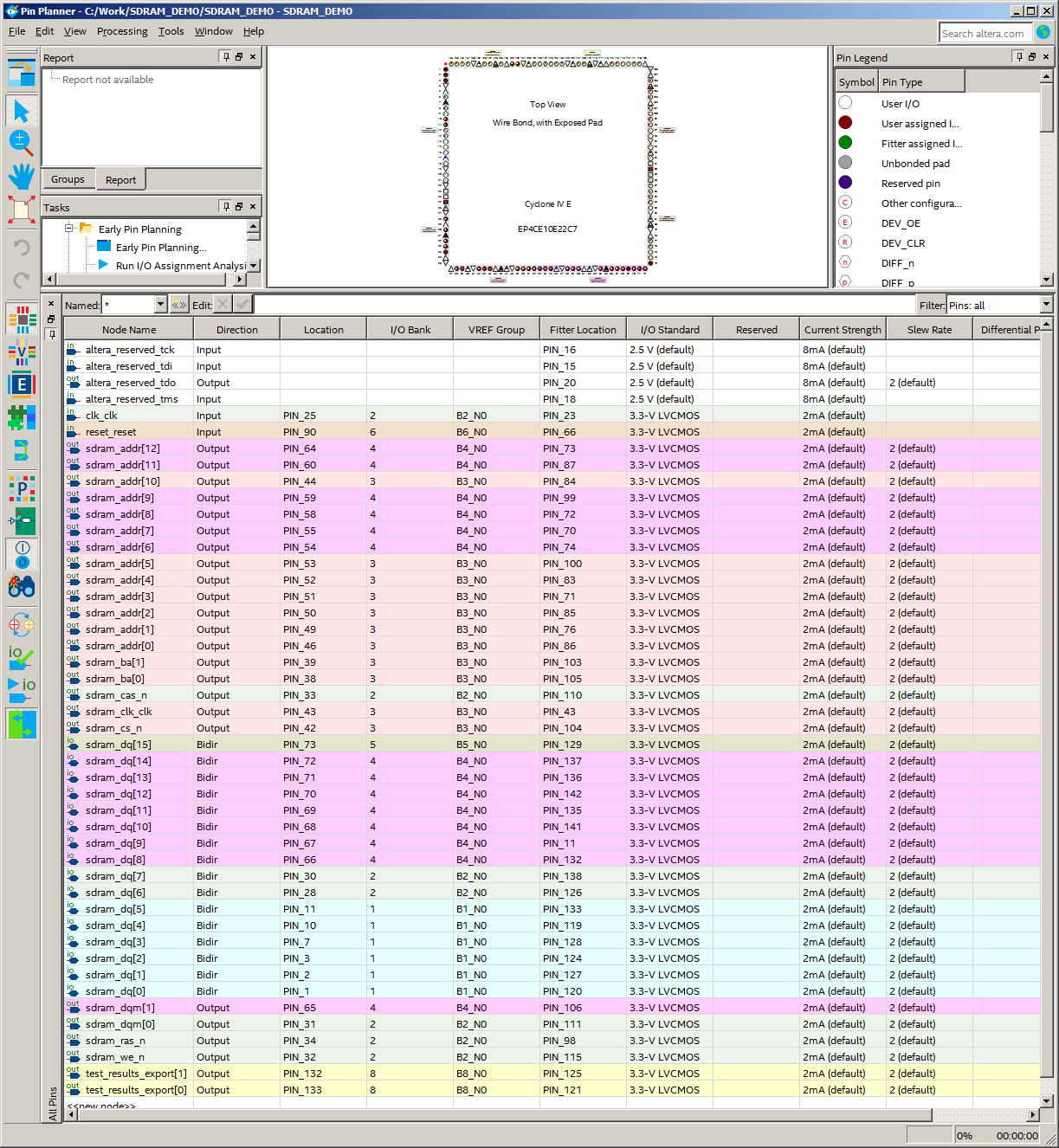

Закройте Редактор назначений и откройте Планировщик контактов.

Назначить ножки можно сверившись с чертежом, а можно взять список из *.

qsf-файла, входящего в проект, который я приложу к статье.

Все, закройте Pin Planner и выполните чистую компиляцию проекта.

Аппаратная часть готова, переходим к разработке программного обеспечения получившейся процессорной системы.

Но статья оказалась настолько огромной, что мы это сделаем.

в следующий раз .

Теги: #Программирование микроконтроллеров #Компьютерное оборудование #Системное программирование #FPGA #FPGA #FPGA #FPGA

-

Новый Мускус

19 Oct, 24 -

Muscleadonis Добавляет Живое Видео

19 Oct, 24