В предыдущей публикации я представил метод синтеза асинхронных схем с использованием минимальной элементной базы.

Этот метод не требует расчета логических функций, а представляет собой коррекцию исходного поведения путем добавления дополнительных сигналов.

Я покажу вам, как это работает, на примере элемента C.

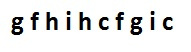

Первоначальное поведение выглядит следующим образом:

Сигналы a, b являются входными, c — выходными.

Признаки событий не указываются, так как для синтеза это ненужная информация и для оптимизации их лучше размещать в конце.

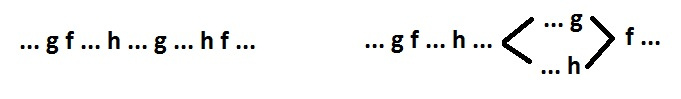

Цель синтеза — добавить дополнительные сигналы так, чтобы каждый невходной сигнал f можно было уместить в следующие шаблоны:

В общем, таких шаблонов есть еще несколько, но в данном случае достаточно только этих.

Давайте посмотрим на начальное поведение и выявим любые проблемы.

Во-первых, есть две синхронизации параллельных ветвей.

Во-вторых, наличие входных сигналов.

В исходном поведении нет двух последовательных входных переключателей, поэтому входные сигналы не являются проблемой.

Но на этапе декомпозиции все же могут возникнуть проблемы, связанные с входными сигналами.

В результате нам необходимо обеспечить две синхронизации.

Один сигнал может обеспечить только одну синхронизацию (сигнал f во втором шаблоне).

Сигнал c не может использоваться для синхронизации; он не вписывается в шаблон.

Это означает, что для синхронизации требуется как минимум 2 дополнительных сигнала.

И в этом случае достаточно двух сигналов:

Сигналы f, g укладываются в шаблон, т.е.

уже имеют двухвходовую реализацию.

Мы объявляем их псевдовходами.

Сигналы a, b теперь вызывают только псевдовходные события.

Поэтому их можно исключить из дальнейшего рассмотрения.

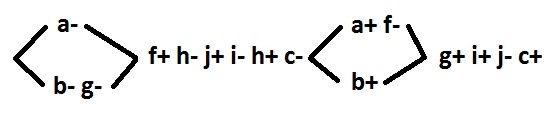

В результате мы получаем поведение:

Сигналы f, g являются псевдовходными.

Нарушений КСК нет. Поэтому, казалось бы, мы можем начать разложение.

Но, поскольку сигнал с требует представления в виде триггера (для декомпозиции), и при этом сигнал с является причиной только псевдовходных событий, переключение двойного сигнала пришлось бы ставить параллельно с последующей синхронизацией.

И это слишком сложное решение.

В этом случае проще включить сигнал c в шаблон, добавив 1 или 2 дополнительных сигнала.

Такое дополнение, если не вставлять подряд два переключателя одного и того же сигнала, не влечет за собой нарушений CSC и не мешает разложению как старых, так и новых сигналов.

В нашем случае нам придется сложить 2 сигнала h и i, причем единственным возможным способом:

Сигналы f, g являются псевдовходными.

Теперь мы можем перейти к разложению.

Только сигнал i требует представления в качестве триггера, поэтому давайте добавим двойной сигнал j:

В результате все сигналы c, h, i, j укладываются в шаблон, и нет необходимости проводить фактическую декомпозицию.

Теперь восстановим сигналы a и b, ранее исключенные из рассмотрения.

Таким образом, мы получаем скорректированное начальное поведение, при котором все невходные сигналы укладываются в шаблон.

Остается только расположить знаки так, чтобы минимизировать количество дополнительных инверторов.

Теперь введем инверторы k и n для устранения несоответствий, возникших на входах элементов g и i.

В результате коррекция не исказила исходное поведение.

Логические функции выглядят следующим образом:

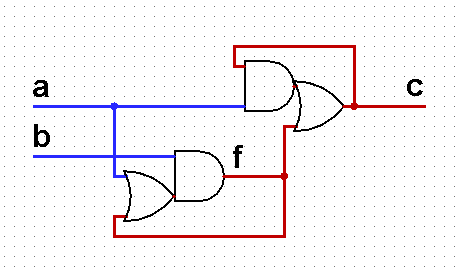

Схема С-элемента:

Для сравнения интересная реализация на трехвходовых элементах.

Поведение выглядит следующим образом.

Логические функции:

И сама схема.

Теги: #асинхронные схемы #самосинхронные схемы #FPGA

-

Сериализация Ссылки В Unity

19 Oct, 24 -

Канал Aurora Открыт В Firefox 5 Alpha 2

19 Oct, 24 -

Как Узнать Посещаемость 3,8 Млн Сайтов

19 Oct, 24