Наконец выпущен в России туториал по SystemVerilog уровень выше, чем для новичков .

В учебнике описаны технологии и приемы, которые просят на собеседованиях в NVidia, Intel, AMD, Apple и других компаниях, занимающихся электроникой: использование параллельных утверждений и функционального покрытия, которое сейчас требуется не только от инженеров по верификации, но и от разработчиков чипов; алгоритм работы симулятора с дельта-циклами; вменяемое объяснение статического временного анализа; схемы связи аппаратных блоков через аппаратные очереди; реализация этих коммуникаций с использованием конечных автоматов с путями данных и т. д. В главе о последнем у российского читателя может вызвать недоумение упоминание о «политкорректной системе».

Что бы это значило? Это, наверное, намек Инцидент, произошедший в округе Лос-Анджелес в 2003 году.

Власти Лос-Анджелеса попросили производителей, поставщиков и подрядчиков прекратить использовать термины «главный/подчиненный» применительно к компьютерному оборудованию, поскольку эти термины напомнили одному служащему округа о рабовладельческом прошлом.

В настоящее время авторы технической литературы избегают терминов «ведущий/подчиненный».

В современной Америке работают и афроамериканские инженеры (например, София Мвокани из Камеруна - на фото слева), а использование старых терминов выглядит архаично, как, например, в украинской технической литературе выглядели бы термины «пан/слуга».

вместо принятого «ведение/ведение» (русское «вождь/раб»).

Тема борьбы афроамериканцев за гражданские права появляется в российском электронном образовании не впервые.

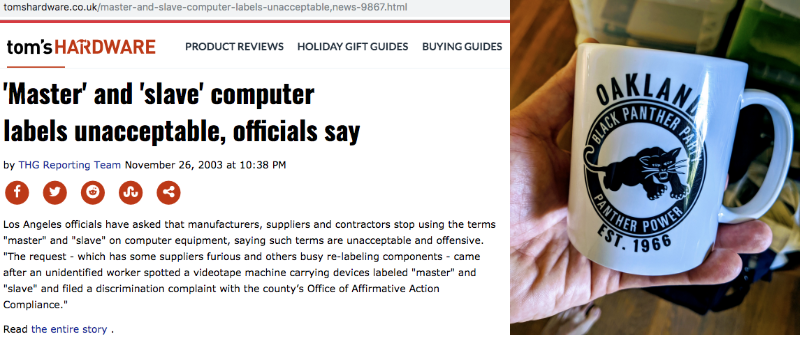

Например, Татьяна Волкова, известный специалист в области электронного образования, носит футболку с эмблемой «Черных пантер» — калифорнийского движения, которое в свое время сочло мирный протест недостаточным и занялось вооруженным протестом.

Полное изображение эмблемы под кожаной курткой Татьяны Александровны под катом, но в основном я буду говорить о дельта-циклах и конечных автоматах:

Ниже скриншот статьи про хозяина/раба и обещанную эмблему Чёрных Пантер, после чего переходим к самой книге.

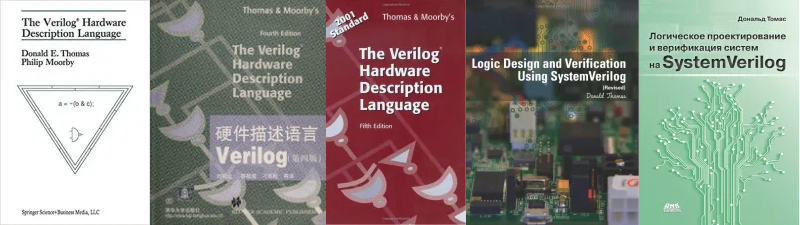

Прежде всего, Дональд Томас, автор книги «Логическое проектирование и верификация систем с использованием SystemVerilog» (2019 на русском из ДМК-Пресс, 2016 на английском) — это тот самый Дональд Томас, который в соавторстве с Филипом Мурби написал в 1991 году книгу Дональда Томаса и Филипа Мурби «Язык описания аппаратного обеспечения Verilog».

Еще в 1991 году многие компании, производящие электронику, все еще проектировали микросхемы по старинке, рисуя их на экране с помощью мыши; технологии логического синтеза только что вышли из лабораторий в производство; языки описания аппаратуры считались предназначенными для написания моделей и тестов, а не исходного кода для создания конечных схем; помимо закрытого на тот момент VHDL и Verilog существовало множество небольших и проприетарных языков, таких как Abel, CUPL, PALASM; а у Intel и MIPS были внутренние языки описания оборудования.

Именно в этой среде была опубликована книга Томаса и Мурби, ставшая для разработчиков цифровых микросхем 1990-х годов тем же, чем была книга Кернигана-Ритчи для программистов на C, а для программистов на C++ — книгами Бьярни Страуструпа.

Книга выдержала пять изданий, с 1991 по 2002 год, но оказалась явно недостаточной для эпохи iPhone. А в 2016 году Дональд Томас решил наверстать упущенное и опубликовал новую книгу, в которой описал ключевые инновации в языке и методологии за 25 лет. Те самые 25 лет, за которые Verilog стал общей основой для всей индустрии, на нем написаны схемы всего — от пресловутых айфонов и управляющих компьютеров в Теслах до российских военных вертолетов.

Далее я выделю свои комментарии синим текстом, чтобы отделить их от картинок в книге.

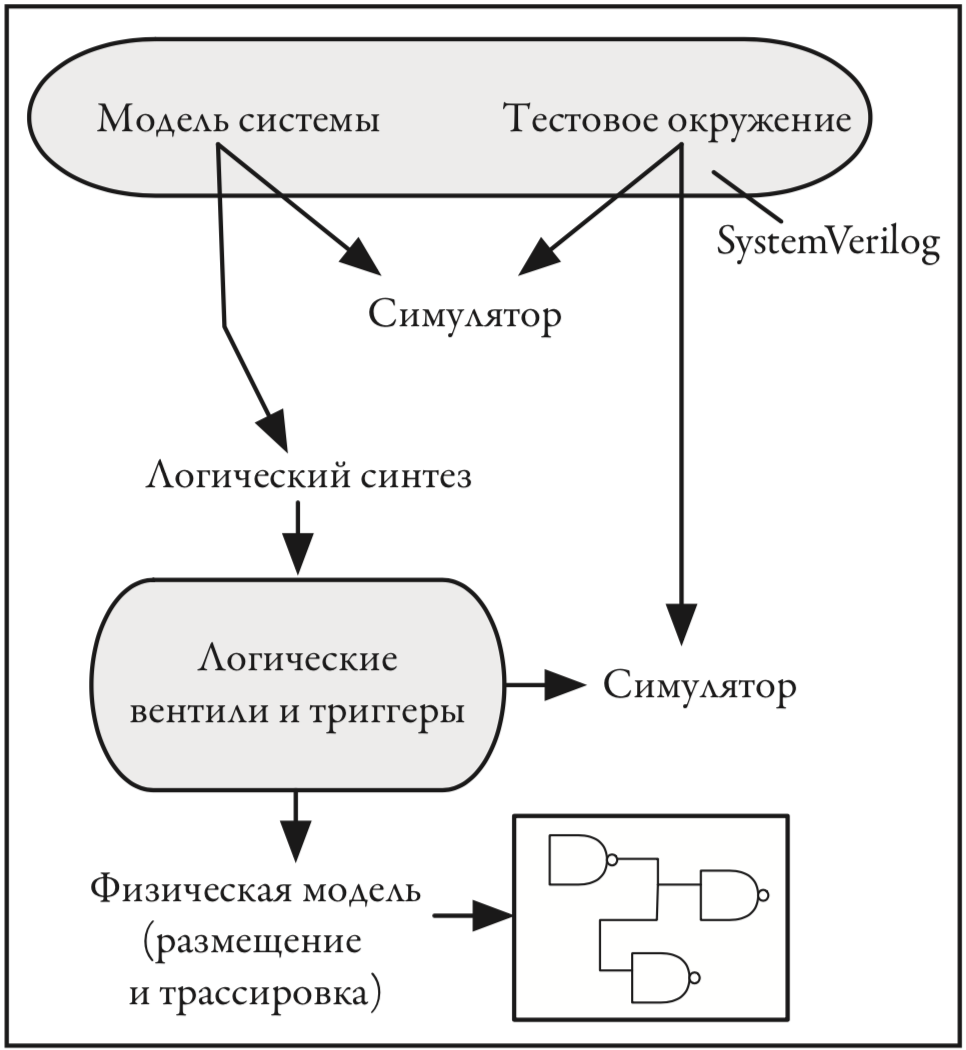

Еще перед основным текстом книги есть предисловие «Контекст: проектирование на уровне переноса регистров», чтобы программист, школьник или, скажем, тот, кто любит потренироваться с макетами, случайно берет с полки эту книгу, сразу понимает, о чем идет речь и как можно применить книгу.

Там говорится:

Сейчас производятся цифровые системы с миллиардами транзисторов на кристалле.Заодно вот упрощенная картинка, иллюстрирующая, как текст на верилоге превращается в дорожки и транзисторы микросхемы на заводе:Дилетант, конечно, может в качестве спецификации (для реализации на макетной плате) нарисовать несколько логических вентилей и соединить их проводами, но для коммерческих проектов это древняя история.

Современные системы задаются на языках описания аппаратуры, таких как SystemVerilog.

Первое слово в книге после предисловия — «симулятор».

Чтобы разобраться в языках описания аппаратуры, необходимо четко понимать, что синтезированное подмножество verilog — это не язык программирования, а язык описания электрических схем.

Точно так же, как, скажем, HTML — это не язык программирования, а язык описания веб-страниц.

В то время как язык программирования предназначен для компиляции в цепочку команд процессора, язык описания аппаратного обеспечения предназначен для компиляции (в частности) в аппаратное обеспечение самого процессора.

При этом перед заброской в аппаратуру необходимо проверить код на языке описания аппаратуры, для чего используется специализированный интерпретатор, называемый симулятором.

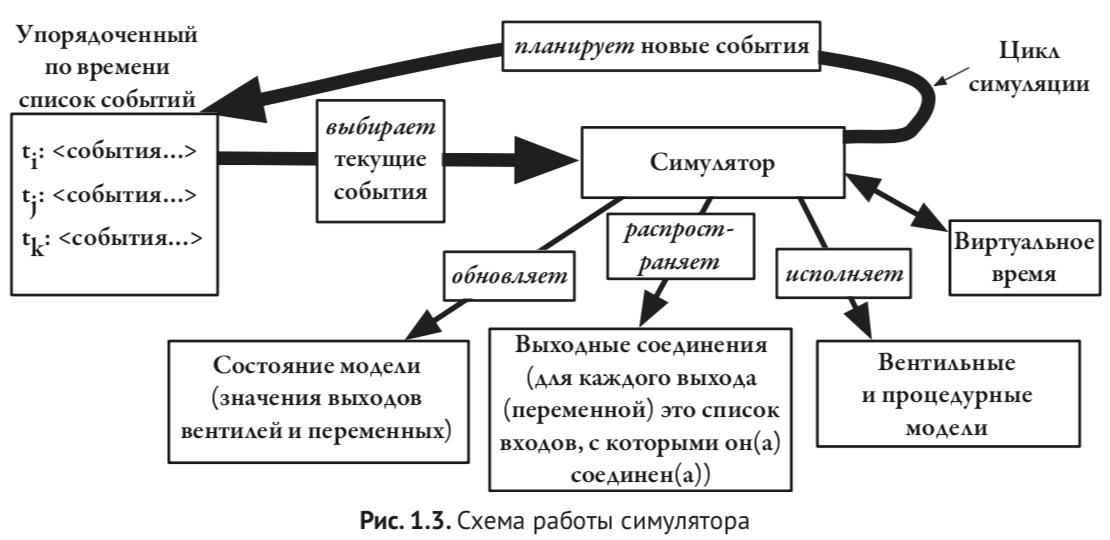

В начале книги Дональд Томас показывает упрощенную картинку симулятора, а в конце уточняет и дополняет ее:

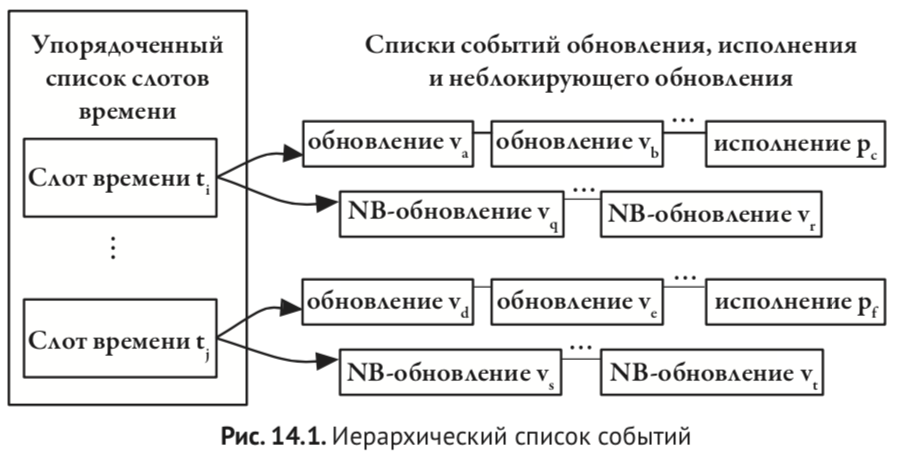

В симуляторе есть очереди событий и моделируемое время:

Событие может породить новое событие как в текущий момент моделирования (в текущем дельта-цикле), так и в будущем.

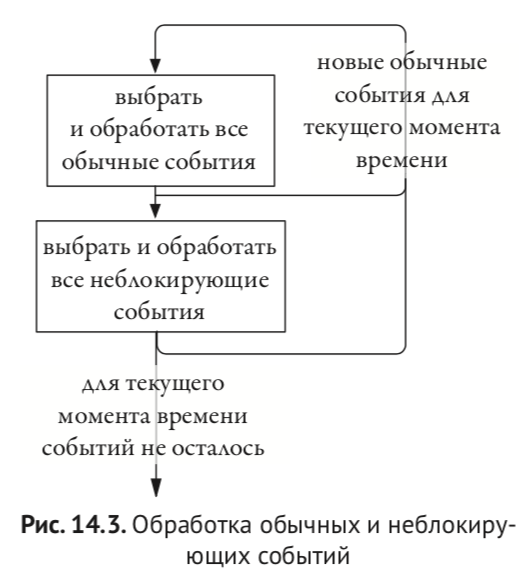

В текущем дельта-цикле сначала обрабатываются все события, генерируемые так называемыми блокирующими назначениями, а затем обрабатываются события, генерируемые неблокирующими назначениями.

Это необходимо для корректного моделирования параллельной семантики распределения электрических сигналов в аппаратном обеспечении:

Помимо синтезированного подмножества verilog, существует еще несинтезируемое подмножество.

Он предназначен для описания тестовой среды и тестов, поэтому его можно рассматривать как своего рода язык программирования.

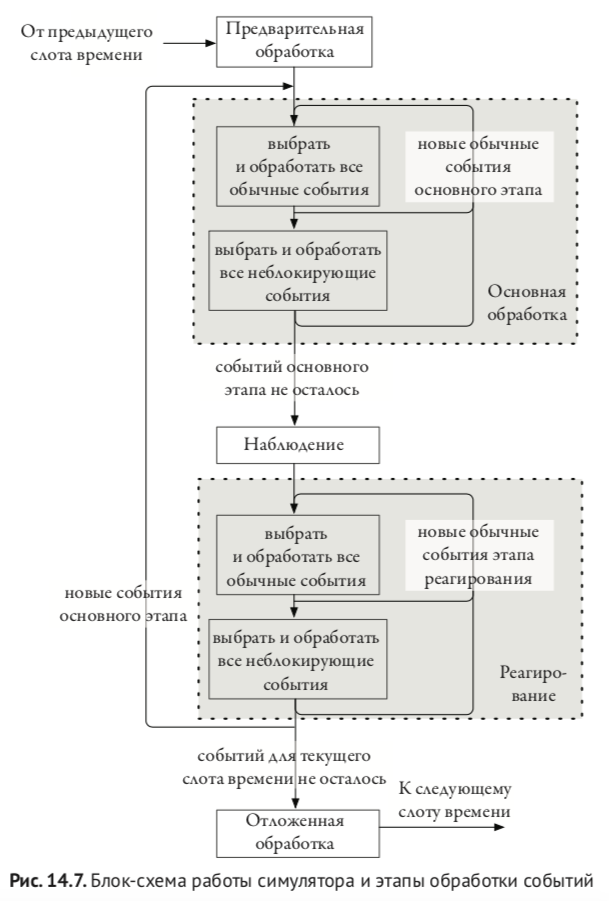

Для тестовой среды и событий мониторинга введены дополнительные шаги симулятора:

Точное знание алгоритма работы симулятора очень полезно во избежание различных ошибок, связанных с так называемым состоянием гонки.

Когда я беру интервью у инженеров, я всегда прошу их привести пример состояния гонки в Verilog. Более того, если для молодых инженеров по проектированию и верификации проектов RTL такие знания очень желательны, но не 100% необходимы во всех аспектах, то есть профессии, в которых непосредственно за эти знания платят деньги.

Я говорю о программистах, которые работают в командах Synopsys VCS, Cadence IES и Mentor ModelSim. Synopsys и Cadence — две компании, расположенные в Калифорнии в 15 минутах друг от друга.

У них работает всего несколько тысяч человек, но они контролируют разработку чипов по всему миру — в Intel, Apple, Samsung, Huawei, даже в секретных российских институтах, производящих чипы для военной техники.

Если товарищи Путин, Рогозин и Вексельберг действительно хотят внедрить импортозамещение в России, то они могли бы профинансировать разработку российского аналога Synopsys VCS (для моделирования verilog), Synopsys Design Compiler (для логического синтеза verilog) и Synopsys IC Compiler ( для физического размещения результатов логического синтеза).

В России, вероятно, несколько тысяч математически подкованных программистов.

Хотя лицензии на эти программные продукты довольно легко взломать, использовать их без поддержки сложно.

Если Huawei отключить от Synopsys и Cadence, им придется в некотором смысле хуже, чем если бы они были отключены от Android и даже ядер ARM. Да, вот усовершенствованный алгоритм в конце книги Дональда Томаса.

Если вы его не запомните, бесполезно проходить собеседование в симуляционных группах Synopsys, Cadence, Siemens/Mentor, Xilinx и т. д. — вас попросят нарисовать это на доске и попросят придумать, как оптимизировать какую-то конкретную задачу.

случай:

После объяснения моделирования в начале книги Дональд Томас описывает сам язык SystemVerilog. Этот язык возник как надмножество Verilog в 2002 году в результате слияния Verilog-2001, Vera и Superlog, а также с добавлением идей из языка спецификации свойств (PSL), которые были преобразованы в утверждения SystemVerilog (SVA).

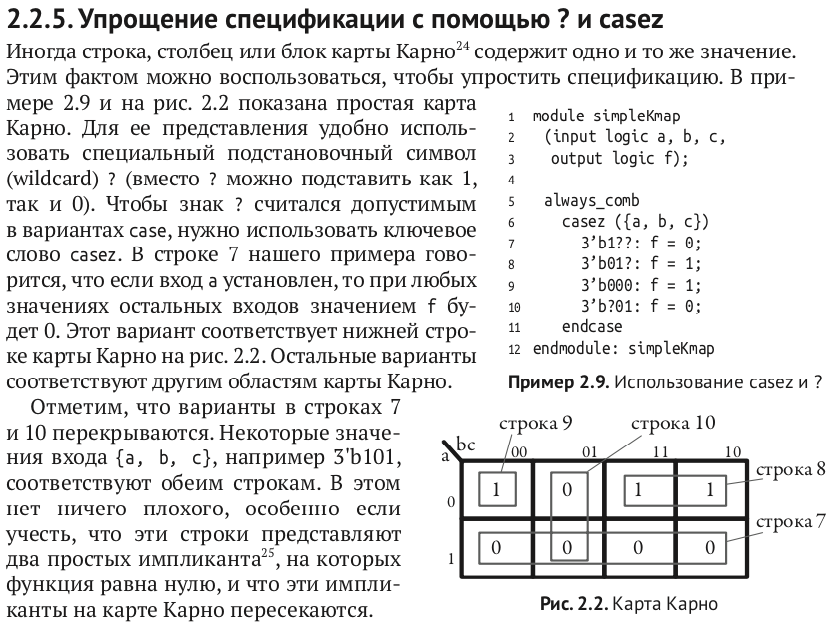

Дональд Томас считает, что основы цифрового дизайна вы где-то уже изучили, поэтому вплетает в ткань истории разные известные вещи вроде карт Карно.

Карты Карно использовались для ручного проектирования схем в 1960-х годах, после чего этот метод был заменен автоматической логической оптимизацией с использованием алгоритма Куайна-МакКласки и автоматического логического оптимизатора Espresso. Поэтому карты Карно присутствуют во всех университетских учебниках по проектированию цифровой логики, но они словно висят в воздухе.

А здесь Дональд Томас связывает карты Карно с жизнью верилог-дизайнера XXI века:

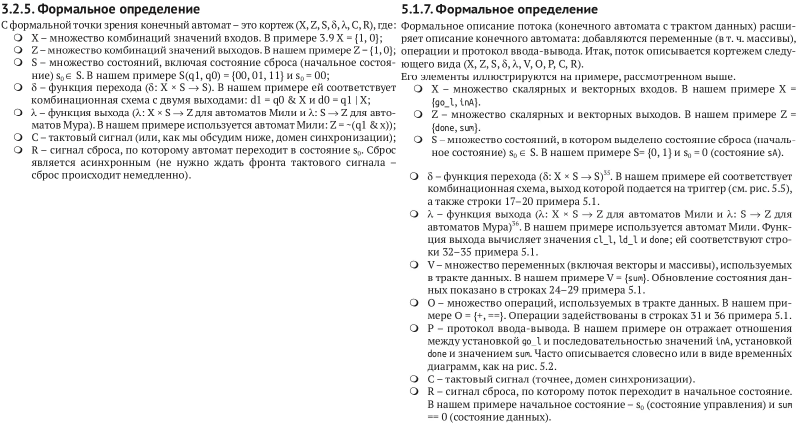

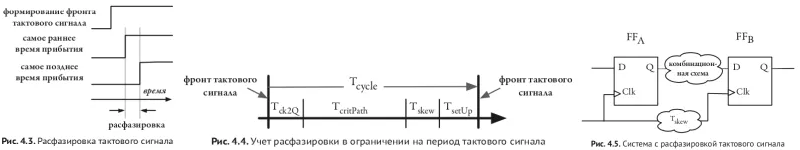

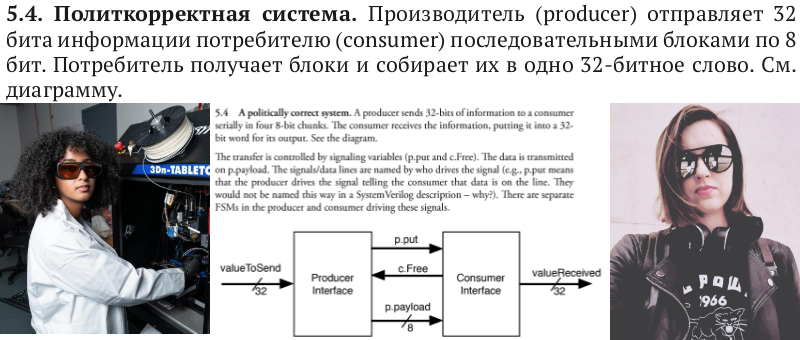

Далее Дональд Томас пишет о конечных автоматах и дает 1) строгое математическое определение; 2) диаграммы; 3) код; 4) после чего начинает расширять их до конечных автоматов с путем передачи данных - аппаратные потоки; 5) после чего эти потоки начинают с ним взаимодействовать, как по простым «политкорректным» (см.

выше) протоколам, так и с помощью аппаратных очередей.

Вот код простого автомата с путем передачи данных, который Томас приводит в качестве первого примера:

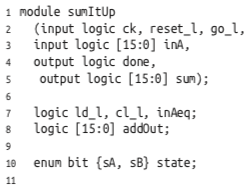

Далее у Томаса есть глава, посвященная статическому временному анализу.

Ничего особенного, но чище, чем многие популярные индийские сайты «Как пройти собеседование по СБИС».

И еще более полно, чем в некоторых книгах по верилогу, которые нудно разжевывают синтаксис языка, но толком не показывают, как им пользоваться.

Зачем нужен статический временной анализ? В реальном железе, в отличие от иллюзии, которую показывает программисту процессор, каждый расчет проходит через интервал времени, когда на проводах есть всякая фигня - не только четко рассчитанные нули и единицы, но и всякие случайные глюки, то есть глюки и вообще нецифровые значения в запретной зоне.

Например, если все напряжения выше 0,7 вольт считать цифровой единицей, а все напряжения ниже 0,3 вольт считать цифровым нулём, то на проводе может быть 0,4 вольта.

В конце концов все сигналы в схеме идут своим чередом, и ситуация стабилизируется, но это «в конце концов» должно быть меньше тактового цикла.

Этот цикл обратно пропорционален частоте, на которой работает схема (гигагерц, мегагерц).

Если устоявшийся результат вычислений или логических операций не попадет в D-триггер (минимальный элемент памяти) в момент открытия (интервал вокруг изменения такого сигнала), состояние схемы станет мусорным - взорвется спутник или реактор, айфон перестанет отвечать на звонки.

Проектировщику аппаратуры необходимо знать всю эту тему не менее досконально, чем логику.

Почему анализ статичен? В 1980-е годы оно было динамичным – задержки определялись с помощью моделирования.

Это оказалось ненадежным для схем с сотнями тысяч, миллионами или миллиардами транзисторов, и теперь все задержки рассчитываются статически, на основе анализа путей прохождения сигнала после синтеза.

Тактовый сигнал также может поступать в разные части микросхемы с некоторой задержкой, что добавляет на эту кухню еще одну неопределенность, которую необходимо устранять (к счастью, не вручную, а с помощью программ синтеза дерева тактовых сигналов и других методов):

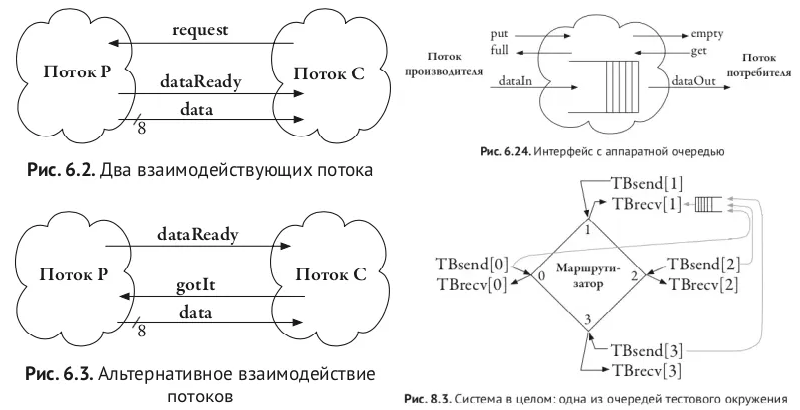

В главе о потоках Томас рассматривает несколько основных вариантов того, как параллельные конечные автоматы с путями данных могут обмениваться информацией, включая использование буферов и очередей.

Как в самом проекте/схеме, на уровне передачи регистров, так и в поведенческой модели или тестовой среде схемы.

Читая Томаса, рекомендуется самостоятельно писать и отлаживать примеры для всех случаев описанных им протоколов.

Дело в том, что код на такие темы (небольшой управляющий конечный автомат, поток данных между двумя модулями, конвейерные пути данных или просто код для аппаратной очереди) часто дают написать на доске или на компьютере во время собеседований второго уровня.

в компаниях по производству электроники.

Если вы сможете написать пример любой из комбинаций, которые описывает Томас, за 20 минут с 30-50 строками кода, то вы произведете хорошее впечатление.

Трудно научиться, но легко бороться.

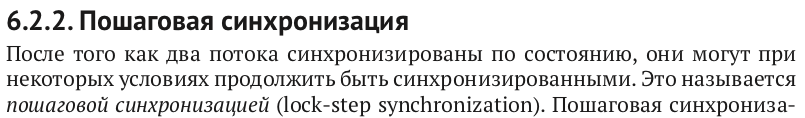

Тестовая среда маршрутизатора (рис.

8.3) с очередями для нескольких портов является популярным примером, используемым для объяснения методологий проверки.

Вероятно, потому, что некоторые из этих методологий были изобретены в Cisco и других компаниях, разрабатывающих чипы для сетевого оборудования.

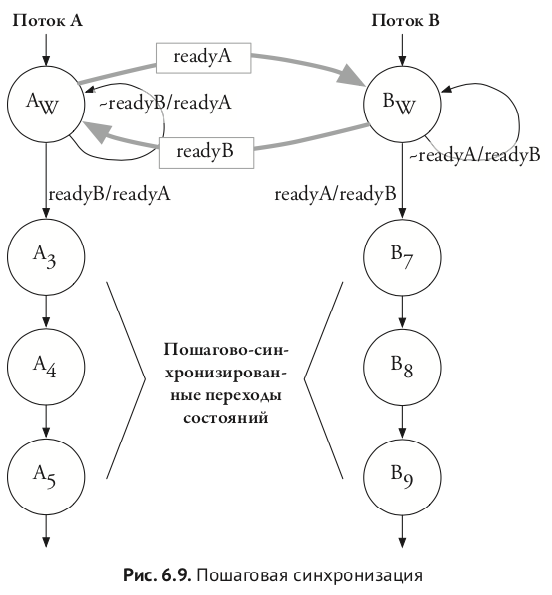

В главе 6.2.2. Томас описывает один из вариантов взаимодействия потоков — пошаговую синхронизацию (Lock-step).

Одно из применений фиксированного шага — в системах высокой надежности, например, в автомобильной электронике.

Особый случай: два процессора могут выполнить одну и ту же программу с задержкой в несколько тактов, и во время этого исполнения специальная схема может проверить совпадение их результатов.

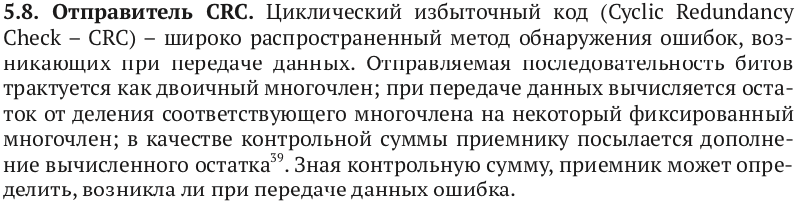

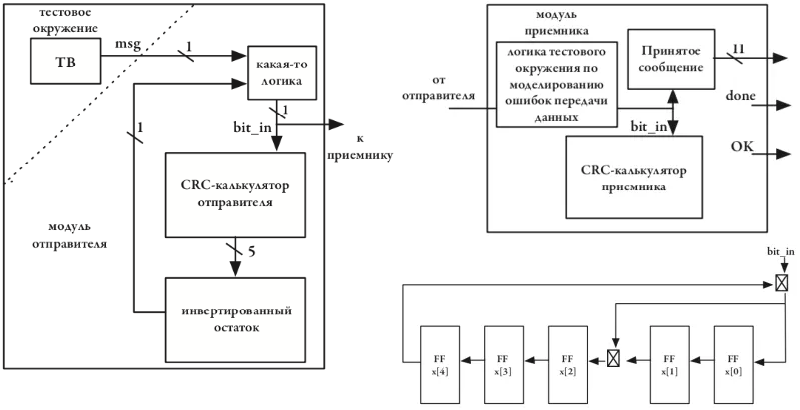

Томаса явно беспокоила надежность, поскольку помимо блокировки шага он ссылается на использование CRC — циклического избыточного кода для обнаружения ошибок при передаче данных.

При этом Томас объясняет, как вычислить CRC с помощью LFSR, регистра сдвига с линейной обратной связью.

Молодой инженер должен уметь и то, и другое.

В этом заслуга книги Томаса — она хоть и не всегда копает глубоко, но затрагивает многие темы и показывает, куда копать:

Описывая CRC, Томас ссылается на очень интересную и непонятую в России книгу.

Хакерское наслаждение :

Дональд Томас в своей новой книге также затрагивает три технологии, которых вообще не было в старой книге:

- Автоматическая генерация псевдослучайных транзакций с правилами ограничений (constrained случайные транзакции/ограничители).

- Учитывая покрытие интересных сценариев, возникающих при бомбардировке дизайна ограниченными случайными транзакциями, функциональное покрытие.

- Язык темпоральных логических утверждений (параллельных утверждений) и его использование как в моделировании, так и в автоматическом доказательстве свойств конструкции с использованием формальных программ проверки.

Поначалу все они использовались для создания сред тестирования инженерами по верификации, но теперь от проектировщиков также требуется знание функционального покрытия и языка темпоральных операторов (SystemVerilog Assertions — SVA).

Томас дает некий минимум, который поможет вам не застрять, скажем, на телефонном собеседовании, но для реальной работы нужно знать гораздо больше.

И не только язык темпоральных операторов как таковой, но и практика отладки с его помощью параллельных конечных автоматов, генерируемых симулятором для каждого оператора, а также использование формальных программ проверки.

В последние годы формальная проверка на основе утверждений широко внедряется в Apple, AMD и других подобных компаниях.

У меня есть друг, который скачал Вот книга о языке временных утверждений и изучал его все новогодние каникулы вместо того, чтобы поехать с девчонками на Гавайи.

Отсюда вы можете понять, насколько важны утверждения SystemVerilog (SVA) для вашей карьеры и отрасли.

Правда, для полноты картины следует упомянуть, что он сын выходцев из Тайваня, а они к таким вещам относятся более жестко, чем русские.

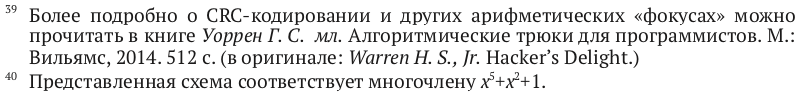

Вот как Томас справляется с генерацией псевдослучайных транзакций (транзакция с полями rand и их ограничением с помощью конструкции ограничения):

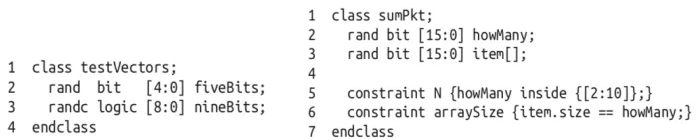

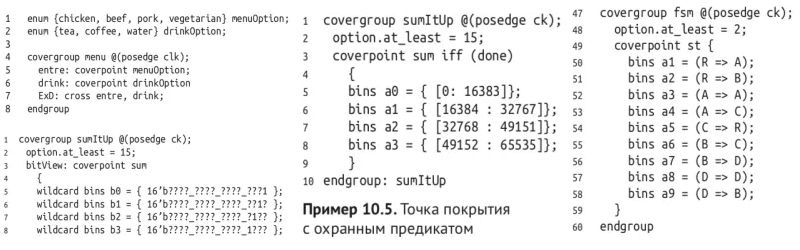

А вот как Томас относится к функциональному покрытию — Covergroup/coverpoint/bins с учетом комбинаций покрытий нескольких переменных (перекрестных), использования групповых интервалов, диапазонов значений, а также покрытия переходов в конечных автоматах:

Вот пример простейшего темпорального утверждения «если q истинно по положительному фронту тактового сигнала, то через цикл должна выполняться последовательность s2, в которой сначала r истинно, а еще через три такта — s»:

Что читать до и после книги Дональда Томаса «Логическое проектирование и верификация систем с помощью SystemVerilog»?

Если вы вообще ничего не поняли в моем посте, то можете попробовать прочитать книгу «Проектирование цифровых схем и компьютерная архитектура», Дэвид Харрис и Сара Харрис.

.

Книгу Харриса и Харриса может понять любой, кто умеет читать и считать, при условии, что читатель мотивирован.

Книга начинается с уровня средней школы — напряжения, двоичные числа — и заканчивается разработкой собственного процессора с использованием Verilog. Внимание, спойлер: Дэвид Харрис и Сара Харрис не муж и жена и даже не брат и сестра.

Это просто однофамильцы, случайно начавшие работать преподавателями в том же университете и попутно написавшие книгу.

Вот слева на фото девушка Ирина из новосибирского Академгородка держит в руках английское издание Harris&Harris, а справа – ее русское издание.

После книги Дональда Томаса рекомендую скачать статьи Клиффа Каммингса.

Он самый известный тренер Verilog как по синтезу, так и по проверке.

Читая книгу Дональда Томаса, у меня много раз возникала мысль: «тут неплохо бы для полноты вставить такой-то отрывок из Клиффа Каммингса».

Клифф взимает от 1000 до 3000 долларов за каждого участника своих семинаров, в зависимости от продолжительности семинара (от дня до недели), а компании по производству электроники платят за повышение квалификации своих недостаточно подготовленных инженеров.

Даже в Стэнфорде, увы, не все этому учат — у меня был стажер из Стэнфорда, я от него это знаю.

Если вы загрузите все бесплатные статьи Клиффа Каммингса после прочтения Дональда Томаса, вы сэкономите все эти деньги.

Эти две статьи обязательны — все любят спрашивать об этом на собеседованиях: Методы проектирования и проверки пересечения тактового домена (CDC) с использованием SystemVerilog Методы моделирования и синтеза для асинхронного проектирования FIFO с асинхронным сравнением указателей Желательно прочитать эти три статьи, особенно об удалении асинхронного сброса, перекодировании состояний автомата и стиле автомата «case (1'b1) // Synopsys Parallel_case.state[STATE_N]: .

», который уже давно использовался в высокоскоростных чипах еще в Sun Microsystems и продолжает использоваться сегодня: Методы проектирования асинхронного и синхронного сброса — вторая часть Методы кодирования и написания сценариев для проектов конечных автоматов с оптимизированными для синтеза выходными данными без сбоев Методы проектирования синтезируемых конечных автоматов с использованием новых усовершенствований SystemVerilog 3.0 Но вот интересная статья, где вы увидите непродуманность вериологии, оставшуюся с 1980-х годов.

Хотя сейчас это не так актуально, в эпоху статического временного анализа в литературе и коде иногда упоминаются инерционные и транспортные задержки, и стоит знать, как их моделировать: Правильные методы добавления задержек в поведенческие модели Verilog

Это я с Клиффом Каммингсом:

В опросе могут участвовать только зарегистрированные пользователи.

Войти , Пожалуйста.

Какие темы поста вас заинтересовали? 33,82% Алгоритм моделирования и импортозамещение 23 29,41% Аппаратные потоки и системы безопасности автомобилей 20 32,35% Языки темпоральных утверждений, решатели ограничений псевдослучайной генерации и функциональное покрытие 22 29,41% Харрис и Харрис и статьи Клиффа Каммингса 20 48,53% Конечно, «Черные пантеры» ! Проголосовали 33 68 пользователей.

37 пользователей воздержались.

Теги: #Интервью #Высокая производительность #Системный анализ и проектирование #Аномальное программирование #Параллельное программирование #FPGA #триггер #verilog #vhdl #vhdl #vhdl #vhdl #systemverilog #systemverilog #методологии разработки #формальная проверка #языки описания оборудования #цифровые электроника #проектирование микросхем #учебник #влси

-

Энергия, Которая Объединяет Все Воедино

19 Oct, 24 -

Разработка Веб-Систем «Здесь» И «Там»

19 Oct, 24