На эту конструкцию меня подтолкнуло наличие на каком-то этапе обучения макетной платы EP2C20F484C7 от Altera (семейство Cyclone-II).

FPGA содержит возможности, позволяющие превратить ее в интегральную схему с любой цифровой логической функцией.

Проектирование сводится к выявлению программируемых элементов (перемычек или ячеек памяти), после удаления которых в структуре схемы остаются только те соединения, которые необходимы для выполнения требуемых функций.

На практике эта задача весьма сложна, поскольку современные ПЛИС содержат в среднем несколько десятков тысяч перемычек.

Поэтому для проектирования обязательно используются системы автоматизированного проектирования (САПР FPGA).

В каких случаях целесообразно использовать FPGA?

При разработке оригинального оборудования, а также для замены традиционных электронных схем низкой и средней степени интеграции.При этом значительно уменьшаются размеры устройства, снижается энергопотребление и повышается надежность.

Наиболее эффективно использование ПЛИС — в изделиях, требующих нестандартных схемотехнических решений.

Проектирование цифровых часов на ПЛИС позволяет сократить время отладки.

Количество используемых элементов, интегральных схем и блоков памяти.

Весь процесс создания часов сводится к следующим моментам: 1. Выбор модели ПЛИС.

2. Написание управляющей программы FPGA на языке VHDL. 3. Отладка программы на отладочном стенде.

4. Создание принципиальной схемы элементов питания и индикации.

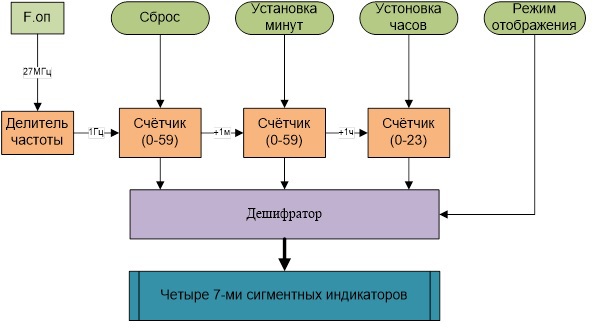

Функциональная схема Функциональная часть часов представлена на рис.

1, где 4-семисегментные индикаторы отображают часы и минуты или минуты и секунды в зависимости от состояния кнопки «Другое».

Кнопка «Сброс» предназначена для сброса счетчика секунд в зависимости от его значения, если оно больше 30, то добавляется 1 минута и секунды сбрасываются, если меньше, то секунды просто сбрасываются.

Кнопки «Час» и «Мин» предназначены для установки часов (нажатием).

Также для реализации часов понадобится кварцевый генератор, который предназначен для получения фиксированной частоты с высокой температурной и временной стабильностью, низким фазовым шумом и стабильностью частоты примерно (10-5-10-12).

Структурная схема часов и описание их работы

При составлении структурной схемы рис.2 учитываем, что у пользователя должна быть возможность обнуления секунд, установки часов и минут, а также режим отображения двух вариантов: час/мин или мин/сек.

При проектировании было решено использовать кварцевый генератор импульсов частотой 27 МГц.

Так как текущая частота гарантирует высокую точность отсчета секунд. Сигнал с кварца подается на блок делителя, который в свою очередь преобразует сигнал частотой 27 МГц в тактовый сигнал прямоугольной формы частотой 1 Гц.

Что в свою очередь означает, что один период колебаний пройдет за 1 секунду.

Затем сигнал с делителя поступает на первый счетчик (счетчик секунд), который также получает команду сброса, счетчик анализирует входы и считает от 0 до 59. Каждый такт отправляет свое состояние в декодер.

При достижении 59 (максимальное количество) или если была нажата кнопка «Сброс», когда состояние счета больше или равно 30, на счетчик слежения посылается тактовый импульс прямоугольного типа.

Второй счетчик (счетчик минут) работает аналогично первому, за исключением того, что входной сигнал не «Сброс», а «Мин» (установка минут).

В результате к текущему состоянию аккаунта один раз добавляется 1, что способствует увеличению счета.

Третий счетчик (счетчик часов), получая сигнал от ведущего счетчика и от «Часа» (Clock Setting), отсчитывает от 0 до 23. Каждый счет отправляет значения счетчика в декодер.

Декодер, обрабатывая сигнал с кнопки «Другое» (режим отображения), выбирает необходимые входные сигналы: для мин/сек выбирает значения первого и второго счетчика, для часов/мин выбирает значения второго и третьего счетчиков.

Он их расшифровывает, а затем шифрует в сигнал, необходимый для отображения чисел времени на блоке из четырех 7-сегментных индикаторов.

Разработка проекта, часы на языке VHDL

При разработке программы на VHDL было решено использовать структуру с использованием компонентов.Это позволяет написать программу для выполнения каждого блока структурной схемы отдельно, а также возможно объединение нескольких блоков в один компонент. Обратите внимание, что нажатое положение кнопки — «0», а нажатое положение — «1».

Рассмотрим компонент под названием timeMS, это универсальный компонент; он используется для отсчета секунд и минут, какими они кажутся.

Библиотека ieee; используйте ieee.std_logic_1164.all; используйте ieee.std_logic_unsigned.all; используйте ieee.std_logic_arith.all; Сущность timeMS Порт ( C: в std_logic; — +1 минута Р: в std_logic; — используйте сброс в течение сек.Сначала мы объявляем необходимые пакеты и описания используемых пакетов.clk: в std_logic; — тактовый сигнал 1 сек.

М: выход std_logic; — передать +1 дальше hex:out std_logic_vector(0 to 5) — вывод на семизначный индикатор ); время окончания MS; Поведение архитектуры timeMS сигнал cl:std_logic; начинать Процесс(clk,R,C) Переменная nex:целый диапазон от 0 до 59; начинать кл<= clk or not; если R='0', то если nex> 29, то М<='1'; следующий:=0; еще М<='0'; следующий:=0; конец, если; еще если (cl'event и cl = '1'), то если nex = 59, то следующий := 0; М<='1'; еще некс:=некс + 1; М<='0'; конец, если; конец, если; конец, если; шестигранник<=conv_std_logic_vector(nex,6); завершить процесс; конечное поведение;

Затем переходим к описанию портов.

Как уже говорилось ранее, данная программа объединяет два счетчика, в результате имеются входные порты как для счетчика минут, так и для счетчика секунд. Входные порты программы: — Порт «С» — принимает два значения («0» и «1») и предназначен для установки минут. — Порт «R» — принимает два значения («0» и «1») и предназначен для сброса секунд. — Порт «clk» — тактовый сигнал прямоугольного типа, для секунд от делителя (см.

дополнения делитель), для минут сигнал от управляющего счетчика секунд. Входные порты программы: — Порт «М» — принимает два значения («0» и «1»), отправляет тактовый сигнал при достижении максимума счета следующему счетчику.

— Порт «hex» – 6-битный вектор для отправки состояния счетчика в декодер (компонент hexMS, см.

дополнение).

Процесс «чувствителен» к изменению сигналов: clk, C, R. Это также асинхронный процесс сброса в случае секунд и асинхронное прибавление к счету +1 в случае минут. Для подсчета используется переменная nex целочисленного типа от 0 до 59. В начале процесса суммируется сигнал тактового импульса и сигнал от кнопки «Мин», затем проверяется следующее: Проверяются условия «Reset» = «0», текущие значения счетчика больше 29, если нет, то просто сбрасывается, иначе сбрасывается и на порт М отправляется «1».

«Сброс» = «1» проверяет, пришел ли нарастающий фронт тактового импульса.

Затем проверьте условия заполнения счетчика и напишите на него +1. В конце программы значения переменной nex преобразуются в шестнадцатеричный порт и отправляются.

Теги: #vhdl #vhdl #vhdl #vhdl #часы на VHDL #EP2C20F484C7 #altera #altera #Cyclone-II #разработка сайтов

-

Веб-Альбомы Picasa – Обновления

19 Oct, 24 -

Проблемы Mysql + Leopard

19 Oct, 24 -

Логика Перехвата Sharejs

19 Oct, 24