Всем привет! Давно не писал статей на любимые темы и наконец-то готов к чему-то более-менее приличному и стоящему.

В этой статье пойдет речь об очень интересной проблеме, с которой инженер-разработчик сталкивается практически каждый день.

Я приглашаю вас увидеть, как можно использовать всю мощь и простоту TCL-скрипты для дизайна на ПЛИС .

В этой статье описание основано на FPGA компании.

Ксилинкс , но это не отменяет возможностей TCL-скриптов для чипов FPGA других производителей.

Интересный? Идти…

Что такое ТКЛ?

TCL (язык команд инструментов) — язык сценариев высокого уровня для выполнения различных задач.Часто TCL используется совместно с графической оболочкой.

ТК (набор инструментов) , но этот аспект не будет рассматриваться в рамках данной статьи.

Язык широко используется в различных задачах автоматизации процессов:

- Тестирование сложных модулей, узлов, частей кода;

- Быстрое прототипирование;

- Создание графических интерфейсов консольных приложений;

- Внедрение в прикладные приложения и задачи.

Программы TCL не требуют компоновки или компиляции, что делает задачу отладки скриптов простой и понятной.

Интерпретатор TCL лицензируется бесплатно и доступен практически для всех платформ (во многих дистрибутивах Linux он доступен по умолчанию).

Это означает, что вы можете использовать его для разработки частных программ и проприетарных приложений без каких-либо ограничений.

На момент написания текущей версии TCL — 8.6. Доступно множество дистрибутивов для работы со скриптами TCL, их отладки и визуализации — MyTcl, TclKit, ActiveTcl и т. д. Цена за 1 лицензию ActiveTcl составляет около ~$1500, что неоправданно для разработки коммерческих приложений.

По личному опыту большинство разработчиков используют знакомую командную строку.

Все программы TCL состоят из команды , которые разделены символом ";" или символ новой строки.

Как и во многих других языках программирования, первое слово — это команда, остальные слова — аргументы команды.

команда arg1 argt2 … argN Например:

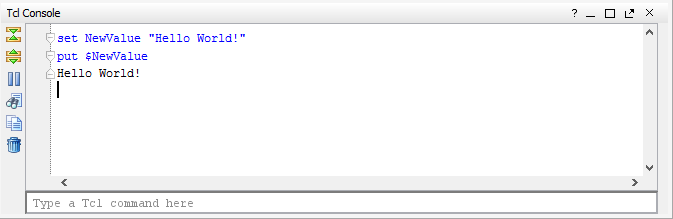

Первая команда создает переменную Новое значение , а вторая команда выводит значение переменной на консоль.set NewValue “Hello World!” puts $NewValue

Для использования переменных с пробелами используются кавычки.

В остальных случаях они не требуются.

Результат выполнения команд показан на рисунке ниже:

На мой взгляд, главное удобство языка TCL в том, что любой аргумент команды можно заменить другой командой.

Для этого его необходимо поместить в квадратные скобки.

Я продемонстрирую эту функцию на примере ниже.

Помимо прочего, TCL способен управлять поведением программы на основе различных событий.

Это означает, что командный процессор может выполнять определенные действия не только на основании записанного в скрипте условия, но и на различные внешние события (изменение значения переменной во внешнем файле, захват данных в канале, завершение выполнения приложения, достижение определенное значение счетчика таймера и т. д.).

Язык TCL имеет богатый набор команд и содержит достаточно удобные инструменты для работы с массивами данных и регулярными выражениями.

TCL предоставляет возможность писать функции и процедуры; доступны описания циклов и условных выражений, что значительно упрощает написание кода.

Зачем вам нужен TCL?

Практически все разработчики FPGA/ASIC рано или поздно сталкиваются с языком TCL в своих проектах.В современной разработке FPGA сценарии TCL активно используются для задач автоматизации и интеграции процессов.

TCL включен во все ведущие CAD FPGA – Квартус Для Альтера , Дизайнерский пакет ISE И Вивадо Для Ксилинкс .

Что может сделать TCL?

- создание проекта (добавление исходных файлов, настройка параметров, иерархии дизайна, назначение файла верхнего уровня и т. д.),

- синтез и трассировка (вплоть до создания самостоятельных этапов с разными настройками),

- тестирование готовых узлов, отдельных модулей и всего проекта,

- автоматическое создание файлов ограничений (UCF/XCI) на основе шаблонов,

- проверка временных ограничений для синтезированного и отслеживаемого проекта.

- настройка параметров схем, компонентов и примитивов ПЛИС, настройка параметров IP-ядер,

Обычно сложные проекты содержат большое количество модулей, написанных разными разработчиками, несколько IP-ядер, файлы ограничений, библиотеки и пакеты функций.

В результате завершенный проект имеет определенную иерархическую структуру и набор правил подключения определенных модулей к необходимым узлам проекта.

Разработчику сложно удержать в голове знания о том, где и как должны располагаться отлаживаемые модули и какие функции они выполняют, если они используются в его работе, но знание их работы на этапе разработки не требуется (т. называется " черный ящик «модули»).

На помощь приходит TCL-скрипт, который управляет структурой проекта и соединяет необходимые узлы по заранее подготовленным шаблонам.

Это обеспечивает гибкость в разработке и дает возможность повторять выполненные модули при переходе из одного проекта в другой.

Как правило, одновременно с этапом создания новых узлов для ПЛИС, этап отладки этих узлов происходит отдельно от проекта и совместно с готовой системой.

Первичное моделирование осуществляется абстрагировано от ПЛИС на компьютере в специализированных САПР и средах моделирования: Modelsim, ISim, Aldec Active-HDL и других.

Для реализации задачи отладки проектов также приходят на помощь TCL-скрипты, позволяющие обрабатывать события, происходящие в ходе моделирования, и принимать решения на основе результатов моделирования.

При отладке узла RTL исключительно на языках HDL могут возникнуть трудности с написанием модели, поскольку любое изменение поведения схемы приведет к необходимости изменения модели и наборов тестов.

Использование связки моделей на языке HDL и скриптов TCL достаточно удобно и для многих решений позволяет ускорить процесс отладки, а также унифицировать сложные тесты.

За этапами написания кода и отладки следуют обычные этапы синтеза, размещения и маршрутизации проекта в чипе FPGA. Это, пожалуй, один из самых сложных этапов, требующий больших вычислительных ресурсов рабочей станции и длительного времени выполнения.

Скрипты TCL позволяют управлять событиями выполнения на каждом этапе, анализировать результаты тех или иных расчетов для достижения наилучших характеристик для проводки и отслеживания проекта (количество занимаемых ресурсов, максимальные тактовые частоты, допустимые значения задержек по таймингам и т. д.).

).

Кроме того, TCL позволяет исключить рутинные действия по выбору и изменению настроек, повторному прогону этапов тестирования и перезапуску определенного этапа при создании файла прошивки ПЛИС.

Такая автоматизация проектирования практически полностью исключает постоянное присутствие человека на этих этапах.

Надеюсь, что, прочитав эти строки, вы уже убедились, что TCL — удобная и мощная вещь, которую совершенно необходимо использовать в своих проектах.

Ниже я разберу один из полезных скриптов, которые использует наша команда для создания проекта в среде Vivado, для добавления уже написанных исходных файлов, различных IP-ядер, файлов ограничений XCI и многого другого.

TCL ваша ПЛИС!

Давайте рассмотрим один из простейших TCL-скриптов для автоматического создания проекта на ПЛИС.Предварительные шаги совсем минимальны: на локальной машине необходимо иметь каталог с исходные коды проекта , как показано на рисунке ниже.

Для удобства я использую независимые каталоги для проектов, созданных в среде.

Пакет Xilinx ISE Design Suite И в Вивадо , если семейство FPGA это позволяет ( Эпизод 7: Артикс, Кинтекс, Виртекс ).

Исходные файлы находятся в каталоге /источник , проект вивадо в одноименной директории, а проект для среды ISE создается в директории /исэ , но результаты синтеза и проводки сохраняются в каталоге /осуществлять .

Все это сделано для удобства управления проектом в целом и независимого управления в разных средах.

Это также делает иерархию более наглядной и избавляет вас от кучи ненужных файлов в исходном коде.

Отдельного упоминания заслуживает каталог.

/вершина в исходном каталоге, где расположены файл верхнего уровня и необходимые файлы ограничений (для ISE это *.

ucf файл, для Vivado это *.

xdc файл).

Проект содержит смешанные IP-ядра – старые, созданные в ISE, и новые, созданные в Vivado. Каталог core_k7 содержит все ядра, созданные в CoreGenerator для ISE. Они не регенерируются и не обновляются при использовании в проекте Vivado (файл *.

vhd используется для моделирования, файл *.

ngc используется для синтеза, а файл *.

xco не добавляется в проект Vivado).

Каталог /ipcores содержит новые ядра в формате *.

xci, созданные непосредственно в среде Vivado. Следует отметить, что для каждого ядра требуется отдельный подкаталог, иначе атрибут « ЗАБЛОКИРОВАНО », что не дает возможности обновить ядра и регенерировать их для синтеза.

Перейдем к описанию TCL-скрипта: # Stage 1: Specify project settings

set TclPath [file dirname [file normalize [info script]]]

set NewLoc [string range $TclPath 0 [string last / $TclPath]-5]

set PartDev "xc7k325tffg900-2"

set PrjDir [string range $TclPath 0 [string last / $NewLoc]]

set TopName [string range $NewLoc [string last / $NewLoc]+1 end]

Первая строка ищет расположение сценария TCL на локальном компьютере (находится в каталоге источник/tcl ) и создает строковую переменную с полным путем к файлу.

Вторая строка создает дополнительную переменную, из которой вырезается часть пути.

Обе переменные нужны, чтобы не указывать вручную путь к проекту и имя файла верхнего уровня в следующих переменных.

Переменная ПартДев содержит имя микросхемы FPGA. И это единственная переменная, которая меняется в проекте! Все остальные строки скрипта остаются НЕИЗМЕНИМЫЙ в любом проекте.

# Stage 2: Auto-complete part for path

set PrjName $TopName.xpr

set SrcDir $PrjDir/$TopName/src

set VivNm "vivado"

set VivDir $PrjDir/$TopName/$VivNm

cd $PrjDir/$TopName

pwd

if {[file exists $VivNm] == 1} { file delete -force $VivNm }

file mkdir $VivNm

cd $VivDir

На следующем этапе создаются дополнительные переменные, которые определяют расположение исходных файлов, создают каталог vivado, если он не существует и т.д. Хочу отметить, что я проверяю наличие каталога vivado на локальной машине.

.

Если каталог существует, он удаляется и создается заново, чтобы в новом проекте не было конфликтов.

Команда cd меняет рабочий каталог, а команда pwd показывает местоположение рабочего каталога.

# Stage 3: Find sources: *.

vhd, *.

ngc *.

xci *.

xco *.

xdc etc. # This stage used instead of: add_files -scan_for_includes $SrcDir set SrcVHD [findFiles $SrcDir "*.

vhd"] set SrcVer [findFiles $SrcDir "*.

v"] set SrcNGC [findFiles $SrcDir "*.

ngc"] set SrcXCI [findFiles $SrcDir "*.

xci"] set SrcXDC [findFiles $SrcDir "*.

xdc"]

set SrcPCI [findFiles $SrcDir "cl_pcie*"]

set NewLoc [string range $SrcPCI 0 [string last / $SrcPCI]-6]

Здесь все примитивно и понятно — создаются переменные, определяющие имена всех исходных файлов в каталоге /src. Для поиска файлов используйте процедуру findFiles, к которой мы вернемся позже.

Отдельный поиск ведется по компоненту узла PCI-E, который является базовой и неотъемлемой частью для всех наших проектов.

# Stage 4: Find all subdirs for IP cores (VHD, XCO, NGC, EDN)

set PrjAll {}

lappend PrjAll $DirIps $DirAdm $SrcDir/core_v2_ise $SrcDir/core_v4_ise $SrcDir/core_v5_ise $SrcDir/core_v6_ise $SrcDir/core_k7 $SrcDir/TestBench

set SrcSim {}

for {set i 0} {$i < [llength $PrjAll]} {incr i} {

Теги: #FPGA #fpga/asic #xilinx #xilinx #TCL #tcl/tk #tcl/tk #tcl/tk #tcl/tk #vivado #FPGA #FPGA #FPGA #Высокая производительность #Алгоритмы #Функциональное программирование #FPGA #Программирование микроконтроллеры

-

Поддержка Hp – Когда Обращаться За Помощью

19 Oct, 24 -

Шкловский Иосиф Самуилович.

19 Oct, 24 -

Переместите Дата-Центр За 14 400 Секунд

19 Oct, 24 -

Я Написал Более Быстрый Алгоритм Сортировки

19 Oct, 24 -

Патенты Microsoft В России.

19 Oct, 24 -

Пятый Номер Журнала Full Circle.

19 Oct, 24 -

Большой Брат По Требованию

19 Oct, 24