Проектирование электронных устройств с использованием быстрых модулей DDR SDRAM требует особого внимания к проблеме целостности сигнала.

В статье описан современный инструмент моделирования для решения подобного рода задач.

Сегодня практически вся современная электроника оснащена модулями памяти.

Серверы, компьютеры, смартфоны, игровые приставки, GPS-навигаторы и большинство других устройств спроектированы на базе процессоров и FPGA. Таким устройствам требуется высокоскоростная многоканальная память или память с двойной скоростью передачи данных (DDR).

С каждым новым поколением DDR SDRAM (синхронная динамическая оперативная память с двойной скоростью передачи данных) увеличивается скорость обмена данными и емкость, а энергопотребление памяти снижается.

При проектировании печатных плат для устройств с памятью DDR может возникнуть ряд трудностей, одной из которых является проблема целостности сигнала.

В данной статье рассматриваются вопросы обеспечения целостности сигнала в устройствах, использующих память DDR.

Шум и джиттер цифрового сигнала данных

При приеме/передаче тактового сигнала шины памяти от контроллера к микросхеме могут возникать различные помехи из-за собственного джиттера передатчиков и приемников, потерь в линиях передачи, шума и помех.Все это приводит к джиттеру и искажению формы сигнала цифрового интерфейса.

Шумом можно считать любую нежелательную энергию, добавленную к идеальному сигналу.

Это может быть вызвано помехами от соседних линий, плохо спроектированным каналом передачи, несогласованным импедансом и другими факторами, приводящими к дрожанию импульса.

При отсутствии шума реальный сигнал идентичен идеальному.

Любое отклонение от идеальной формы сигнала влияет на его целостность.

Изменения времени (дрожание) и изменения амплитуды/напряжения (шум) также влияют на производительность системы.

Если целостность сигнала не обеспечена, система DDR будет использовать неверную информацию, что значительно увеличит BER (частота битовых ошибок).

В конечном итоге система будет работать неправильно и неэффективно.

Давайте рассмотрим конкретный пример.

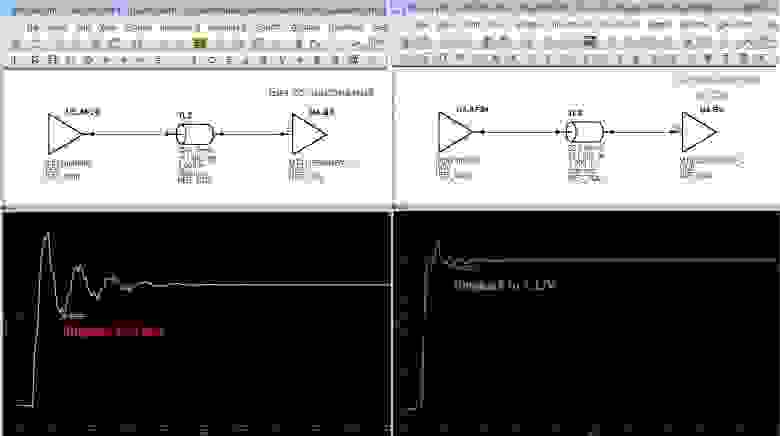

Если бы инженер подключил передатчик к несогласованному приемнику на некотором расстоянии, форма сигнала была бы аналогична показанной на рисунке 1а, с явным звоном 0,86 В и паразитным повышением напряжения 1,75 В при сигнале 1,2 В.

Все это может привести к неисправности логики DDR4 и, если печатная плата спроектирована с такой топологией, то со 100% вероятностью возникнут ошибки в потоке данных, что, в свою очередь, может привести к некорректной работе система .

Теоретически можно решить проблемы звона и перерегулирования за счет укорачивания линии передачи, но, к сожалению, на практике это редко работает. Наиболее эффективным способом является согласование приемника/передатчика по импедансу, в результате чего снижается уровень шума и существенно улучшается форма сигнала (см.

рис.

1б).

Рис.

1. Топология, имеющая проблемы с качеством сигнала: а) до согласования б) после согласования В связи с этим возникает вопрос, какое значение соответствия использовать и как его рассчитать, поскольку даже небольшое изменение значения может существенно повлиять на производительность системы.

Единственный способ решить эту проблему — моделирование, в частности использование интерактивных помощников по настройке сопоставления, используемых в HyperLynx.

Проблемы с синхронизацией в DDRx

Поскольку при проектировании печатных плат все чаще используются параллельные шины, работающие на гигагерцовых частотах, такие как DDR3/4, вопросы целостности сигнала становятся особенно острыми.DDR3 SDRAM, например, существенно отличается по показателям рабочей скорости и частоты от DDR2: максимальная тактовая частота DDR2 составляет 800 МГц, а максимальная тактовая частота DDR3 — 1600 МГц.

За счет снижения напряжения питания ячеек создателям нового типа оперативной памяти удалось снизить ее энергопотребление на целых 15%, что, учитывая впечатляющую производительность DDR2, можно назвать настоящим прорывом.

DDR3 использует летающую сетевую топологию с шиной управления/адреса/управления с внутримодульным (ODT) завершением.

В то же время DDR3 создает новые проблемы целостности сигнала, особенно связанные со схемами ODT, более высокими скоростями передачи данных и артефактами синхронизации.

Хотя существуют контроллеры, которые выполняют автоматическую калибровку чтения/записи для оптимизации времени, разработчик должен убедиться, что время правильное.

Временные ограничения интерфейсов DDR3 настолько жесткие, что эмпирического подхода к оптимизации уже недостаточно, и требуется детальный анализ конструкции, чтобы гарантировать работу интерфейса на высоких скоростях.

Такие сложные временные зависимости довольно сложно проанализировать без помощи дополнительных инструментов.

Чтобы выявить и устранить потенциальные проблемы в целом или рассчитать сложные временные зависимости, инженеры должны провести причинно-следственный анализ, что является сложной и трудоемкой задачей.

Подобные проблемы проектирования часто приводят к задержкам в планировании проекта и, как следствие, значительно увеличивают время вывода на рынок готового продукта.

Передовые и мощные инструменты моделирования могут помочь инженерам быстро находить ошибки и исправлять их, оптимизируя сигналы до приемлемых уровней BER.

Анализ целостности сигнала систем DDR SDRAM

Комитет по инженерной стандартизации полупроводниковой продукции JEDEC утвердил список требований, которые необходимо соблюдать при разработке качественной продукции.Важно, чтобы DDR SDRAM отвечала этим требованиям для обеспечения правильной работы и предотвращения проблем с целостностью сигнала.

Однако проведение всех необходимых измерений и расчетов зачастую связано со многими трудностями.

Иногда этих вычислений можно вообще избежать, строго следуя инструкциям по компоновке, предоставленным производителем контроллера.

Но что, если такие рекомендации не могут быть реализованы из-за различных ограничений в конкретных проектах? Что делать, если требуется много времени, чтобы убедиться, что проект соответствует всем рекомендациям и требованиям? В таких ситуациях необходимо использовать инструменты для быстрого тестирования конструкции перед запуском ее в производство.

С помощью HyperLynx DDR (см.

рис.

2) вы можете смоделировать весь канал DDR за одну итерацию.

Для этого вам достаточно связать соответствующие модели устройств, которые доступны на сайтах производителей.

Время настройки моделирования тогда займет всего десять минут, что позволит запускать будущие симуляции без задержек.

Рис.

2. Моделирование с помощью интерактивного помощника HyperLynx DDR. Процесс настройки интуитивно понятен, поскольку все параметры, необходимые для настройки моделирования, запрашиваются помощником в интерактивном режиме.

Пользователь просто вводит соответствующую информацию, такую как выбор моделей IBIS для контроллеров и устройств памяти, скорость передачи данных для циклов чтения/записи, ODT и т. д. Все созданные конфигурации можно сохранить для использования в будущем, что сокращает время настройки в будущих проектах.

Моделирование можно выполнить до или после трассировки, чтобы определить требования к компоновке печатных плат.

Анализ результатов моделирования

Моделирование включает в себя анализ целостности сигнала и синхронизацию всей шины DDR. По завершении процесса моделирования формируется отчет, включающий данные о прохождении (неуспехе) проверок, в соответствии с конфигурационной информацией и данными, введенными в интерактивный помощник.Результаты можно отфильтровать и должным образом организовать для тщательного изучения проблем синхронизации и целостности сигналов в циклах чтения/записи, адресных и командных шинах или дифференциальных схемах.

Все результаты отчета связаны с соответствующими данными моделирования для быстрого доступа к графическому средству просмотра сигналов.

Данные пакетного моделирования, созданные мастером DDRx, можно сохранить на диск, что позволяет использовать осциллограф HyperLynx для одновременного моделирования нескольких цепей и углубления в проблемы целостности сигнала в автономном режиме.

Заключение

Память DDR SDRAM открывает новые возможности при разработке электронных устройств.Как и в случае с другими высокоскоростными интерфейсами, использование памяти DDR имеет ряд особенностей.

Проблема целостности сигнала должна быть тщательно изучена, чтобы избежать ненужных и дорогостоящих итераций при производстве продукции.

Моделирование — отличный способ решить эту проблему, позволяя учитывать эффекты на уровне платы, такие как изменения импеданса и временные задержки, обеспечивая полный контроль над интерфейсом памяти.

Мощные инструменты анализа помогут обеспечить соответствие ваших проектов рекомендациям JEDEC, а конечный продукт будет работать с высокой производительностью и надежностью.

HyperLynx DDR можно использовать со многими программными системами для проектирования печатных плат, включая PADS и Xpedition. Данная статья опубликована в журнале СОВРЕМЕННАЯ ЭЛЕКТРОНИКА №7, 2018 г.

(www.soel.ru) Теги: # Производство и проектирование электроники # Системный анализ и проектирование # CAD/CAM # моделирование # ddr # Mentor Graphics # целостность сигнала # целостность сигнала #hyperlynx #hyperlynx #hyperlynx #hyperlynx #hyperlynx #hyperlynx # целостность сигнала # целостность сигнала # целостность сигнала #целостность сигнала #целостность сигнала #целостность сигнала

-

Видеоредакторы Для Linux

19 Oct, 24 -

Мифология Здорового Образа Жизни

19 Oct, 24 -

Пикаба Выиграл Open Web Awards

19 Oct, 24 -

Интересный Скетч Factorio: Симулятор Фабрики

19 Oct, 24 -

Расширение Google Chrome Для Отправки Sms

19 Oct, 24 -

Конференция Семтех 2008

19 Oct, 24 -

Три Мудрых Мужчины

19 Oct, 24 -

Ученые Изучают «Жизнь Онлайн»

19 Oct, 24 -

Всегда Начеку: Важность Осознанности

19 Oct, 24 -

Создание Виртуального Mpos-Терминала

19 Oct, 24