Наконец, пришло время продолжить изучение возможностей платы Zynq QMTech и SoC XC7Z020. Следующая интересная задача, которую я придумал для себя в качестве обучающего задания — оснастить плату Wi-Fi-модулем Realtek RTL8822CS и, если Wi-Fi-модуль не нужен, а нужна еще одна флешка, со второй порт для SD-карты.

Если вас интересуют подробности того, как я это все реализовал, добро пожаловать под кат.

Важный! Прежде чем начать рассказ, хотелось бы заранее оговориться, что основная цель, которую я преследую при написании этой статьи, — рассказать о своем опыте, с чего можно начать при изучении плат разработки на базе Zynq. Я не являюсь профессиональным разработчиком ПЛИС и SoC Zynq, не являюсь системным программистом под Linux и могу допускать некоторые ошибки в использовании терминологии, использовать не самые оптимальные способы решения задач и т.п.

Но отмечу, что любой конструктивный подход и аргументированная критика приветствуется.

Ну, поехали.

Сформулируем цель и задачи

Итак, у нас есть плата, описанная в Эта статья и есть желание прикрепить к нему Wi-Fi модуль Realtek RTL8822CS. Модуль, естественно, должен быть правильно инициализирован в ОС Linux и обеспечивать пропускную способность до 150 Мбит/с (именно в этом причина такого ограничения и эта цифра ниже).В качестве альтернативы использованию выхода SDIO нужно организовать второй порт для подключения SD-карт. Исходя из этого, можно сформулировать несколько задач, решив которые, мы сможем достичь цели:

- Проверьте возможность расширения линий SDIO через EMIO (т.е.

через выводы PL-части Zynq) и подготовьте файл битового потока;

- Проверьте работоспособность SDIO через EMIO в baremetal-приложении с помощью карты microSD;

- Сделайте мезонинные платы для модуля Wi-Fi и смонтируйте на них компоненты;

- Подготовьте загрузчик первого этапа, источник дерева устройств, U-Boot, ядро Linux в необходимой конфигурации для запуска модуля Wi-Fi;

- Подготовьте модуль ядра для модуля Wi-Fi, а именно модуль cfg80211, который представляет собой API Linux для устройств 802.11;

- Подготовьте модуль ядра 88x2cs, который является драйвером для модуля Wi-Fi RTL8822CS, работающего поверх шины SDIO;

- Проверяйте производительность сети, делайте широковещательные сканирования, смотрите уровни работы, измеряйте скорость нисходящего/восходящего трафика через iPerf;

Перейдем к реализации задуманного, в целом это не выглядит очень сложно =)

Настройка проекта в конфигурации Vivado и PL

В этой главе я кратко (без скриншотов) опишу процедуру создания нового проекта, подчеркнув важные моменты.Если вам нужны инструкции с картинками, вы можете обратиться к моим предыдущим статьям.

Открытие Вивадо и создайте проект с помощью кнопки Создать проект .

Откроется мастер настройки нового проекта, давайте быстро пройдемся по шагам.

- Дайте проекту имя, например SDIO_EMIO и укажите папку сохранения;

- Мы указываем, что это Проект РТЛ , оставьте флажок включенным На данный момент не указывайте источники ;

- Найдите модель SoC, используемого на плате.

В моем случае это xc7z020clg400-1 ;

- Нажмите «Готово».

Назовем это для простоты блок_дизайн .

Добавьте на диаграмму примитив процессорной системы Zynq, щелкнув правой кнопкой мыши.

Добавить IP — система обработки ZYNQ7 .

Предлагаемые действия мы немедленно выполним от агента автоматизации, через команду на зеленом поле.

Запустить автоматизацию блоков и откройте системные настройки процессора.

Шаблон настроек PS я сохранил заранее, чтобы не пришлось все перепрописывать в каждом проекте.

Вы можете получить его здесь: ссылка на гитхаб .

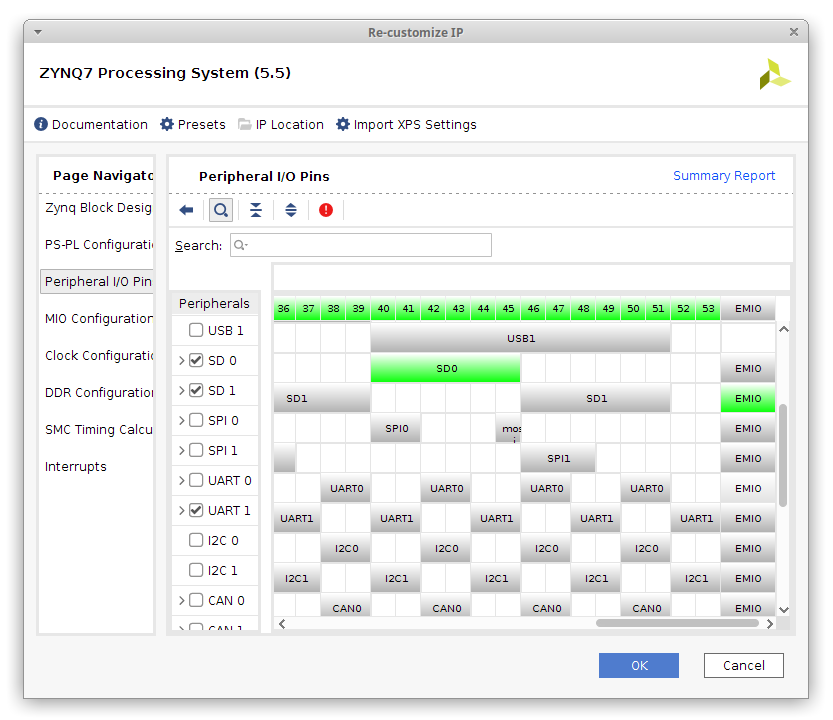

Через меню Пресеты — применить конфигурацию примените его и сразу зайдите в меню Периферийные контакты ввода/вывода .

Поставьте галочку напротив меню СД 1 и проверьте, что опция подключения через ЭМИО :

Остальные настройки я оставил без изменений, в т.ч.

тактовые частоты SDIO, пл.

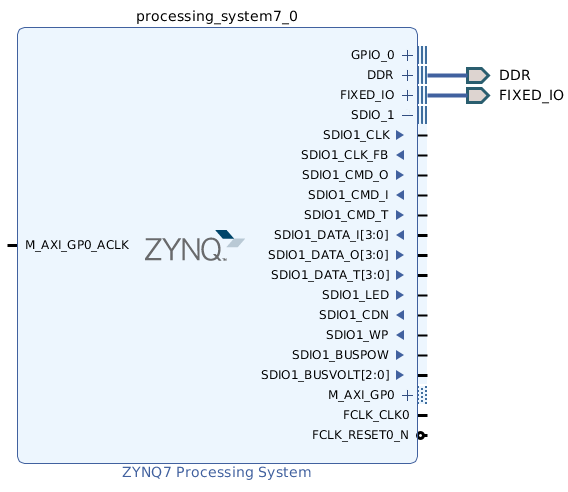

Получаем следующую картину (если расширить группу сигнальных линий SDIO_1 ):

В данном случае нас интересуют линии CLK, CMD и 4 линии DATA, что в целом является стандартным набором для шины SDIO. Но вот незадача, каждая из линий организована тремя отдельными сигналами.

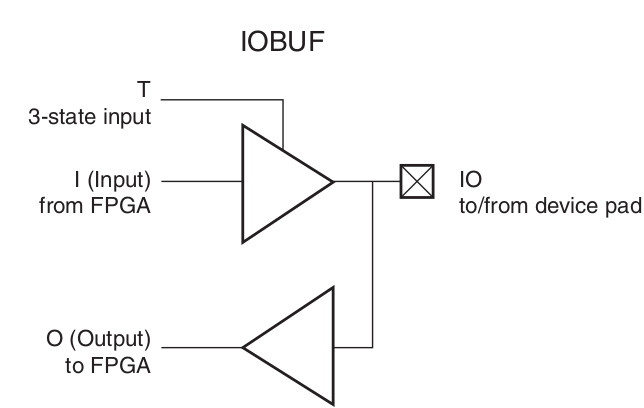

Чтобы решить эту проблему, нам нужно вручную создать буфер IOBUF, который будет управляться через активный вывод T с тремя состояниями и разрешать сигналы ввода и вывода, поскольку нам нужно использовать его с двунаправленным сигналом ввода-вывода.

Это выглядит так:

Т.

к.

его нет в стандартной библиотеке графических примитивов — вам нужно будет создать свой IP-модуль и добавить его на диаграмму.

Для каждого сигнала оно будет разным.

Через меню Источники — Добавить источники (Alt + A) добавлять Исходный код проекта — Создать файл , выберите тип файла Верилог и назовем это iobuf_cmd .

Запишем следующее содержание:

Теги: #linux #Процессоры #Сделай сам или Сделай сам #Электроника для начинающих #wifi #FPGA #howto #verilog #buildroot #zynq #zynq-7000 #qmtech #sdio over emio #realtek rtl8822csmodule iobuf_cmd

-

Давайте Будем Честными О Статическом Анализе

19 Oct, 24 -

Экскурсия По Фабрике Kingston В Шанхае

19 Oct, 24 -

Анализ Рынка Смартфонов Спустя 10 Лет

19 Oct, 24 -

Ленивые Потоки: Необязательный Параллелизм

19 Oct, 24 -

Nokia Выпустила Qt 4.6

19 Oct, 24 -

Первые Шаги Vmware: Сервер Gsx И Сервер Esx

19 Oct, 24