Всем привет! Многим специалистам известно, что топовое сетевое оборудование использует для обработки трафика специальные чипы.

Я принимаю участие в разработке таких молотилок и хочу поделиться своим опытом создания таких высокопроизводительных устройств (с интерфейсами 10/40/100G Ethernet).

Для создания нового канала сетевики чаще всего берут оптику, пару модулей SFP+, подключают их к устройствам: лампочки радостно загораются, пакеты начинают поступать: чип начинает передавать их получателям.

Но как чип получает пакеты из среды передачи? Если вам интересно, то добро пожаловать под кат.

И??? 802.3

Ethernet — это стандарт, принятый IEEE. Стандарты 802.3 охватывают все возможные разновидности Ethernet (от 10M до 100G).Остановимся на конкретной реализации физического уровня: 10GBASE-R («обычный» 10G, без излишеств).

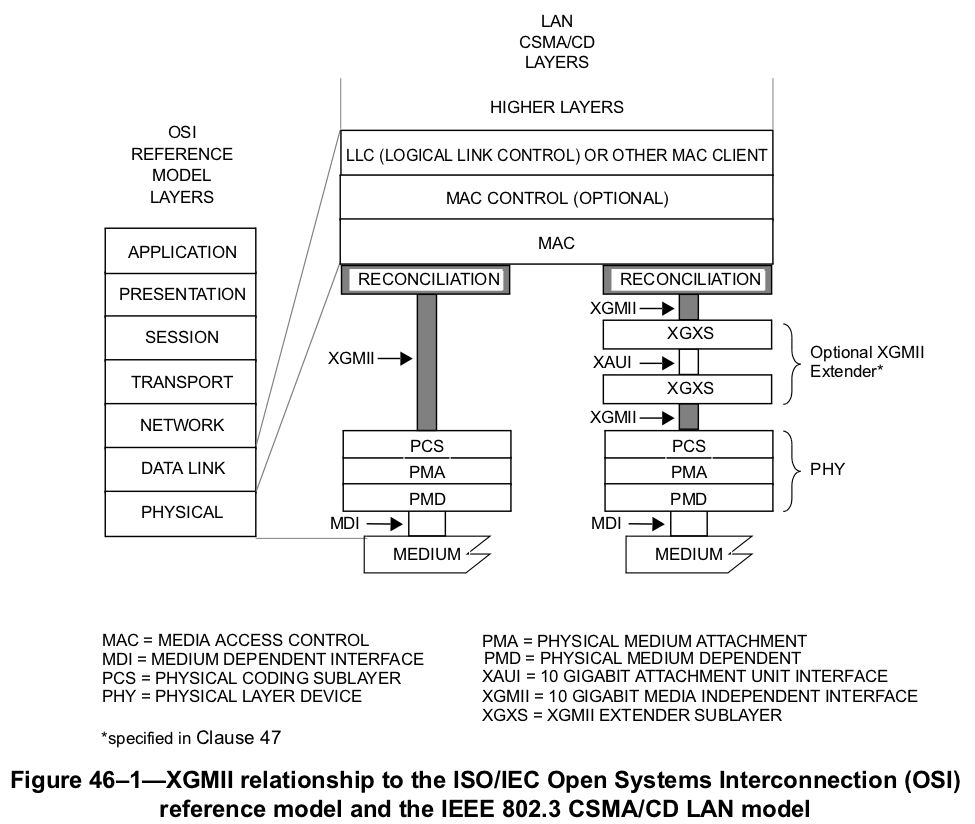

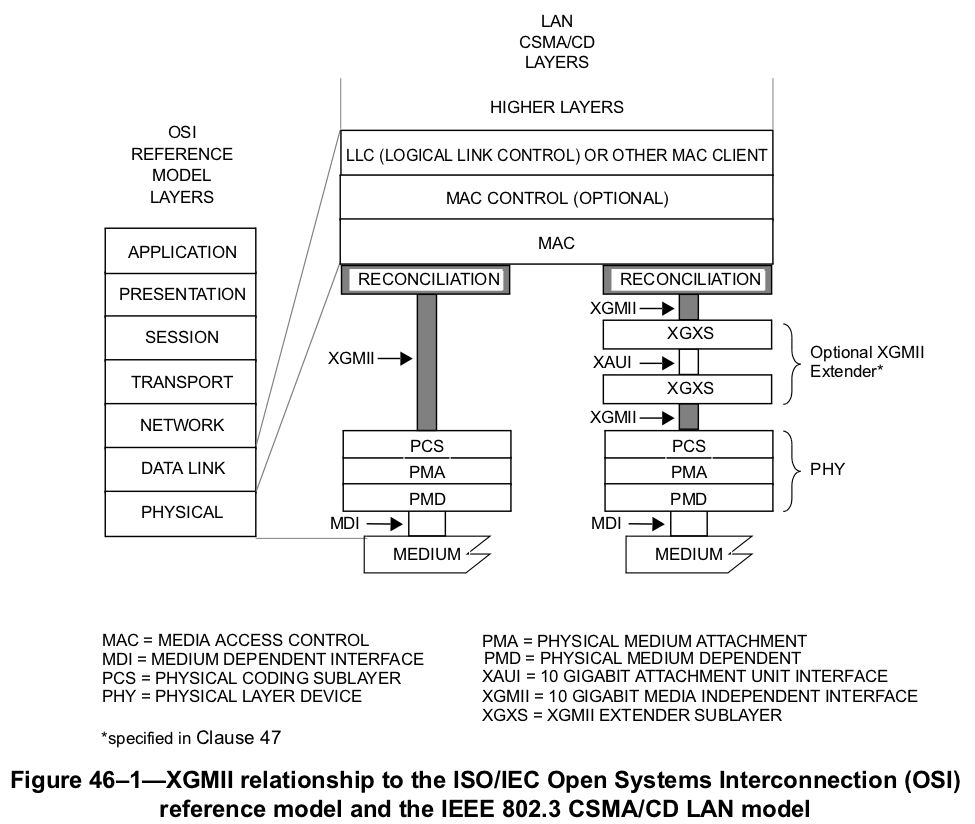

На этом рисунке показаны уровни модели OSI и то, как они сопоставляются с подуровнями протокола Ethernet.

Подуровни:

- ФИЗИЧЕСКИЙ — физический подуровень.

- MAC — подуровень контроля доступа в окружающую среду.

- ПМД — обеспечивает передачу и прием отдельных битов по физическому интерфейсу.

- П.

М.

А.

— обеспечивает сериализацию/десериализацию данных, а также извлечение фрагмента из последовательных данных (при приеме)

- ПКС — обеспечивает скремблирование/дескремблирование, а также кодирование/декодирование (64b/66b) блоков данных

- XGXS — Расширитель XGMII: используется, если PHY и MAC расположены на расстоянии друг от друга (опционально).

- ПРИМИРЕНИЕ — подуровень, преобразующий XGMII в сигналы MAC.

- Середина — среда передачи.

- МДИ — интерфейс, зависящий от среды передачи данных.

- XGMII — Интерфейс 10G, независимый от среды передачи данных.

Цель XGMII — обеспечить простое и недорогое соединение между PHY и MAC.

- ХАУИ — Интерфейс 10G для подключения к трансиверу.

Наличие независимого от среды интерфейса (XGMII) упрощает разработку прикладной логики чипов, т.к.

при любом подключении разработчик где-то получит XGMII. О том, что такое XGMII, мы поговорим позже.

ПМД

Подуровень PMD расположен ближе всего к окружающей среде: его задачи решают специальные модули, хорошо известные сетевым специалистам:| Тип модуля | Интерфейс |

|---|---|

| КСЕНПАК | ХАУИ |

| Х2 | ХАУИ |

| XFP | XFI |

| SFP+ | СФИ |

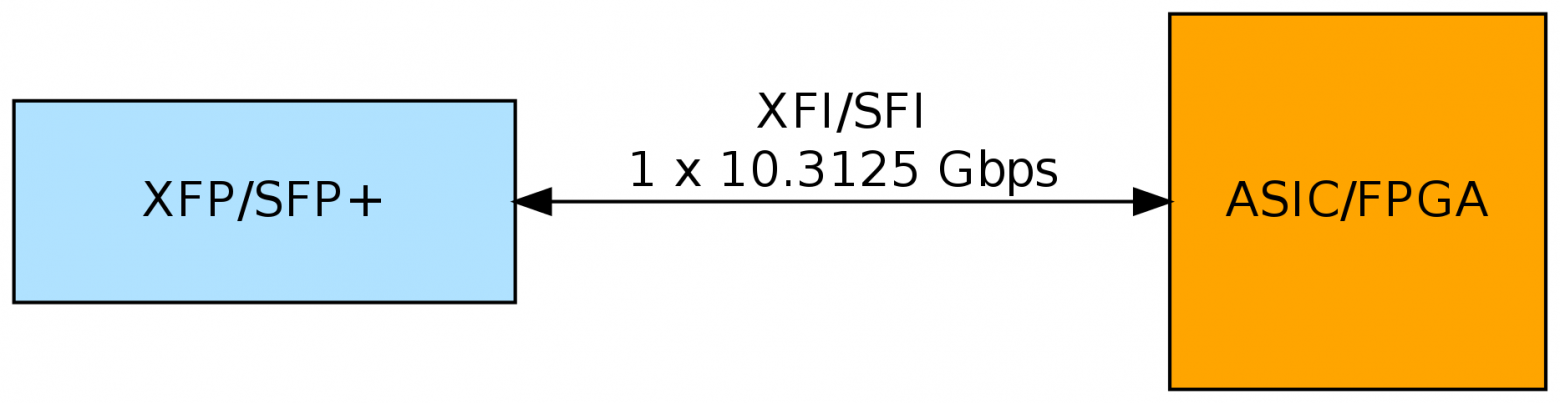

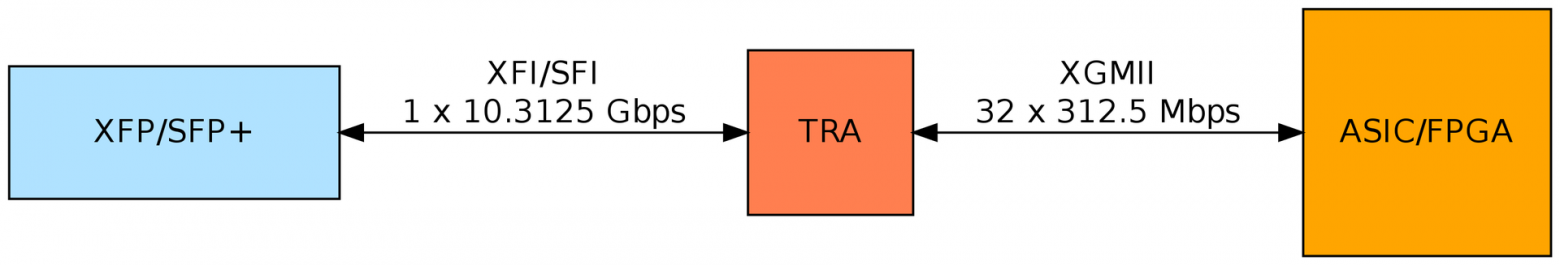

XFI/SFI

XFI и SFI — это по сути один и тот же интерфейс: дифференциальная пара, работающая на скоростях от 9,95 до 11,10 гигабод. Диапазон скоростей определяется тем, что этот интерфейс могут использовать несколько стандартов: от 10GBASE-W WAN до 10GBASE-R over G.709. Нас интересует LAN 10GBASE-R со скоростью 10,3125 гигабод. Одна дифференциальная пара используется для приема, другая – для передачи.

XFI/SFI подключается напрямую к ASIC/FPGA.

Задачи подуровней PMA и PCS можно решить на чипе, где мы будем осуществлять дальнейшую обработку Ethernet-пакетов (после того, как извлечем их из XGMII).

Напомню, что в подуровне PMA необходимо выбрать тактовую частоту на приеме и десериализовать входной сигнал.

Такую работу могут выполнять специальные аппаратные блоки, которые нельзя использовать для других задач.

Эти блоки называются трансиверами.

Их подробное описание могло бы занять целую статью: кому интересно, может посмотреть смотреть Структурная схема трансиверов на ПЛИС от Altera. После десериализации данные поступают на подуровень PCS, где выполняются дескремблирование и декодирование (64b/66b) и данные отправляются в форме XGMII на MAC. Во время передачи выполняются обратные шаги.

PCS может быть реализован либо с использованием специальных аппаратных блоков (Hard PCS), либо с использованием логики, доступной пользователю (Soft PCS).

Конечно, это утверждение справедливо только для FPGA: в ASIC все делается аппаратно.

Производители FPGA предоставляют аппаратные блоки PCS для стандартных протоколов, экономя время и ресурсы разработчиков FPGA. Наличие таких блоков очень подкупает, ведь.

многие стандартные протоколы По опыту, они работают «из коробки», и для большинства из них код бесплатно предоставляется производителем ПЛИС.

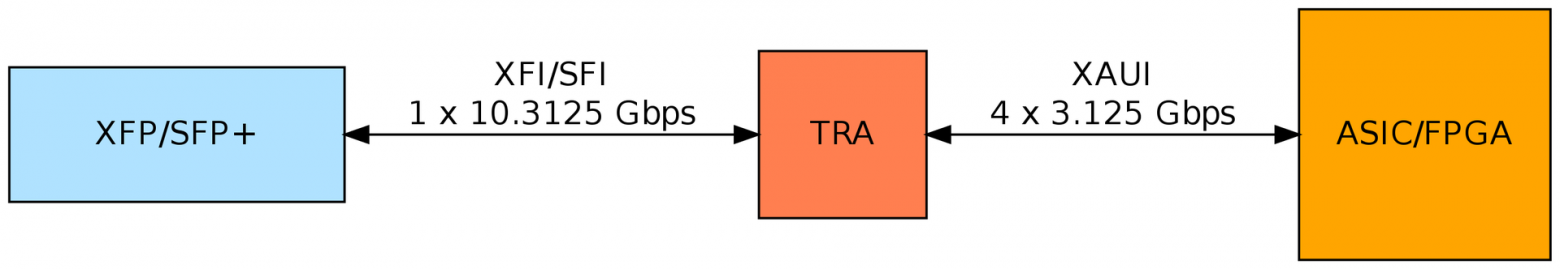

Подключение через внешний чип трансивера

Трансиверы в FPGA дороги; дополнительные десять трансиверов могут существенно повысить цену чипа.

Есть более дешевые чипы, трансиверы которых работают на более низких скоростях (они могут сериализовать/десериализовать данные на более низких частотах).

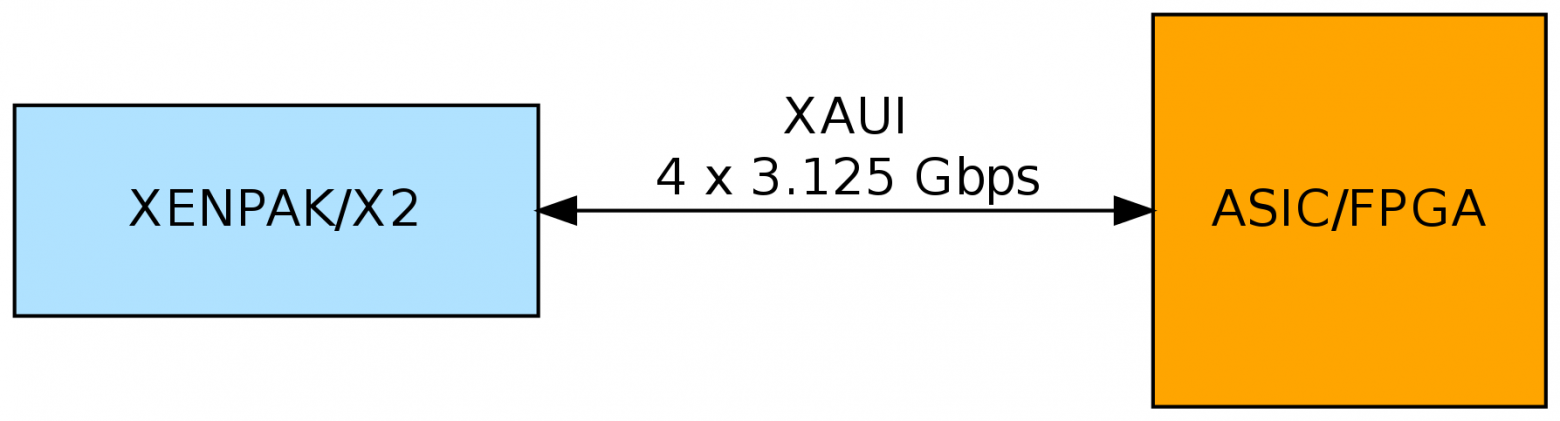

Еще один высокочастотный интерфейс, определенный в разделе 4 стандарта 802.3, — это XAUI: 4 дифференциальные пары со скоростью передачи данных 3,125 гигабод (для одной линии передачи).

При использовании XAUI возникает дополнительный уровень XGXS, который позволяет дистанцировать PHY и MAC друг от друга.

Например, запустить на разных чипах.

Задачу PMA и PCS в таком соединении могут выполнять специальные 10G-трансиверы (допускаю, что может возникнуть путаница, ведь чуть раньше в ПЛИС появились «трансиверы», а теперь здесь появляется этот термин.

Кстати, XFP/SFP+ модули также называются трансиверами.

) Примеры трансиверов 10G:

- www.vitesse.com/products/productLine/10GE-PHYs

- www.marvell.com/transceivers/alaska-x-gbe

- www.broadcom.com/products/Physical-Layer/10-Gigabit-Ethernet-PHYs

Фактически такой трансивер использует блоки PMA и PCS для преобразования XFI/SFI в XGMI, а затем XGMII преобразуется в XAUI. XAUI передается на ASIC/FPGA, который использует приемопередатчики, аналогичные обсуждавшимся ранее, но со скоростью 3,125G. Работа трансивера отличается от того, как это происходит в режиме 10G:

- Требуется четыре трансивера (четыре аппаратных блока), поскольку для этого интерфейса используются 4 дифференциальные пары.

- XAUI PCS использует кодировку 8b/10b. ПК 10G использует 64b/66b.

Этот способ подключения имеет существенные недостатки:

- Высокое потребление выводов: в версии XGMII один чип использует минимум 78 выводов, против 16 в версии XAUI.

- Параллельные интерфейсы могут потребовать выравнивания дорожек на плате, что иногда является нетривиальной задачей.

Соединение XENPAK/X2

Как я и обещал, мы дошли до таких типов модулей.

Нетрудно заметить, что их подключение сводится ко второму варианту, только без использования внешнего чипа-трансивера.

Модуль возьмет на себя задачи подуровней PMD, PMA и PCS.

XGMII

XGMII определен в пункте 46 стандарта 802.3. Этот интерфейс состоит из независимого приема и передачи.Каждое направление имеет 32-битную шину данных (RXD/TXD [31:0]), четыре сигнала управления (RXC/TXC [3:0]) и тактовый сигнал, по которому работает направление (RX_CLK/TX_CLK).

Стандарт определяет, что шины данных и сигналов управления анализируются по каждому фронту тактовой частоты (DDR).

Сам пакет перемещается по шине данных; сигналы управления определяют начало, помогают «выбрать» начало и конец пакета, а также сообщают об авариях.

Значение RX_CLK/TX_CLK составляет 156,25 МГц.

Умножение 156,25 * 10^6 * 32 * 2 дает ровно 10 Гбит/с.

Чаще всего фиксации на обоих фронтах тактовой частоты можно избежать, увеличивая частоту или ширину данных:

- Шина 36 бит (32+4) на частоте 312,5 МГц.

- Шина 72 бита (32*2+4*2) на частоте 156,25 МГц.

Только топовые (читай: дорогие) ПЛИС могут себе позволить работать на частотах ~300 МГц.

Чтобы «отхватить» пакет от XGMII, используется специальное ядро MAC:

- Собственный.

Купив лицензию на такое IP-ядро, вы (чаще всего) получаете зашифрованные исходники (без возможности модификации) и специального ограничения на количество чипов, в которых может использоваться это ядро, нет. Пример .

- Открытый источник.

Такие ядра очень полезны для новичков, потому что.

Код открытый, и вы можете разобраться, как он работает. Лицензия на использование определяется отдельно.

Пример .

- Самописный.

Однако существует производитель FPGA, которая реализует ядра MAC на аппаратном уровне, экономя ресурсы для пользователя.

MAC-ядро, выбрав пакет из XGMII и поместив пакет во внутреннюю память чипа, «передаёт» управление пакетом прикладной логике чипа: парсерам, фильтрам, системам коммутации и т.п.

Например, если чип находится на сетевой карте, и принимается решение: если пакет необходимо отправить на хост, его можно отправить с помощью PCIe в ОЗУ, подключенное к ЦП.

Личный опыт

L1 в основном занимаются схемотехники, которые раскладывают платы для устройств.Программисты FPGA работают с этим только в начале аппаратного подъема: когда XGMII работает и все трансиверы прошли тесты, тогда мы концентрируемся на том, как делать обработку трафика.

Одно устройство подключается по первому варианту: SFI выходит напрямую в ПЛИС.

В двух других - второй вариант (с использованием трансивера и XAUI).

Также есть устройство, имеющее подключение как напрямую SFI, так и через XAUI, но без трансивера (ПЛИС подключается к другому чипу).

Чтобы использовать внешние трансиверы (да и большинство специализированных чипов), необходимо подписать NDA. Чаще всего с этим особых проблем не возникает. Вместе с NDA выдаются различные документы, например, настройки регистра чипа.

По опыту работы с трансиверами двух разных производителей отмечу, что при подъеме аппаратуры первой партии стабильно возникают некоторые проблемы с настройкой трансивера, которые решались относительно быстро: трансиверы многофункциональны и иногда приходится экспериментировать, чтобы настроить необходимый режим работы.

Иногда бывает, что документация на чипы очень плохая, и приходится перебирать разные варианты, а техподдержка не отвечает или открыто заявляет, что не осуществляет поддержку этих чипов.

Одним из преимуществ использования чипа трансивера является то, что вместе с документацией может распространяться набор настроек прошивки, который необходимо загрузить в трансивер при установке определенного типа модуля.

Насколько я понимаю, в этих прошивках есть хитрые настройки эквалайзеров, без которых определенный тип модулей будет работать с битовыми ошибками.

Именно так поступили с одним из таких модулей SFP+ (с ограничительным усилителем).

Если вы подключаетесь без трансивера, то вам придется самостоятельно подготовить такие настройки для ASIC/FPGA, что может оказаться нетривиальной задачей.

Наличие интерфейса, независимого от среды передачи, значительно упрощает жизнь, потому что.

код (логику приложения: парсеры, генераторы, анализаторы, фильтры и т. д.) очень легко портировать из старых проектов в новые, потому что он не Не имеет значения, какой тип соединения использовался.

Подключение (и обработка) 40G/100G к ASIC/FPGA аналогично 10G, однако есть некоторые нюансы.

Если интересно, этому можно было бы посвятить отдельную статью, хотя она и не будет большой.

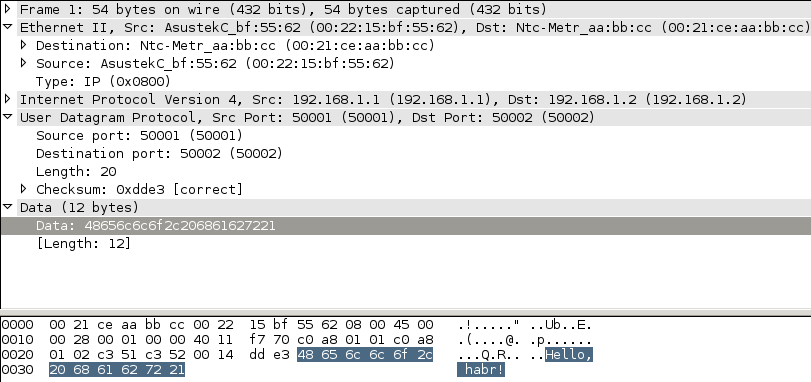

Привет, хабр!

Возьмем обычный UDP-пакет со строкой «Привет, хабр!» и отправьте его на устройство, чтобы посмотреть, как оно будет выглядеть на XGMII.

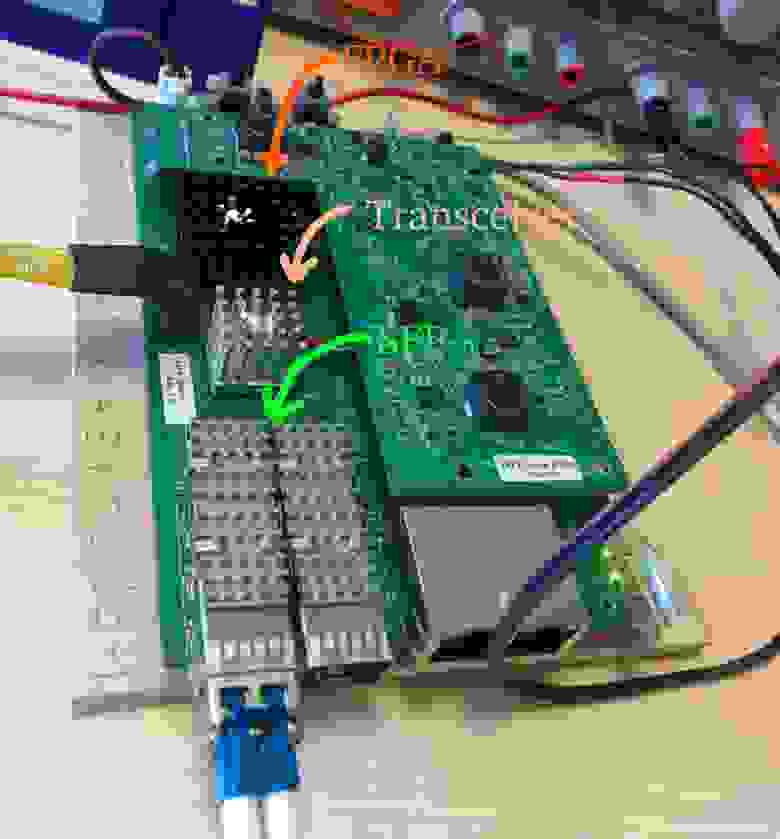

У меня на столе лежит разобранный.

устройство , где чаще всего тестируются новые функции: мы используем его как наглядный пример.

Для этого подготовим специальную прошивку и подключим отладчик, чтобы увидеть сигналы внутри чипа.

Подключение 10G осуществляется вторым вариантом: с помощью внешнего трансивера, отправляющего данные через XAUI на ПЛИС.

Этот трансивер двухканальный: он может работать с двумя SFP+.

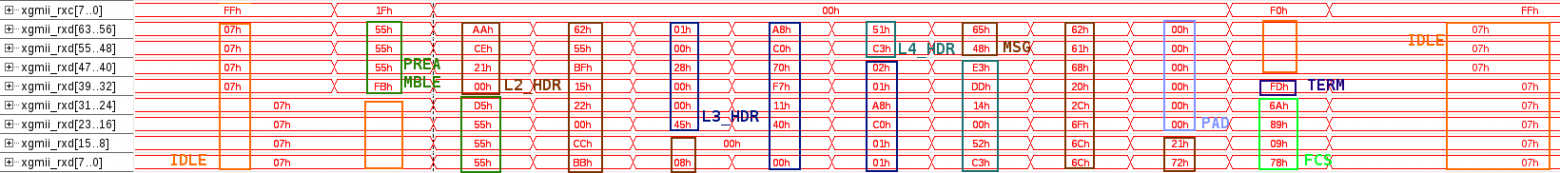

Как XGMII (и наш пакет) выглядит внутри FPGA:

Это устройство использует 72-битную шину XGMII внутри FPGA, работающую на частоте положительного фронта 156,25 МГц.

Легенда:

- xgmii_rxc — набор управляющих сигналов.

- xgmii_rxd — набор сигналов данных (для удобства разбит на байты).

- ПРАЗДНЫЙ — сигналы отсутствия передачи пакета.

- ПРЕАМБУЛА — преамбула, указывает на начало передачи пакета.

- L2_HDR — Заголовок уровня 2: Ethernet.

- L3_HDR - Заголовок уровня 3: IP.

- L4_HDR - Заголовок уровня 4: UDP.

- глутамат натрия — наше сообщение («Привет, хабр!»).

- ПАД - наполнение.

Присутствует в пакете, если исходная длина полезных данных была меньше 60 байт.

- ФТС — контрольная сумма пакета.

С его помощью можно определить, был ли пакет поврежден во время передачи или нет.

- СРОК — сигнал окончания передачи пакета.

Спасибо за ваше время и внимание! Если у вас есть вопросы, задавайте без колебаний.

P.S. Благодарю коллег по цеху des333 И паулиг за конструктивную критику и советы.

Теги: #10g #10gbe #ethernet #FPGA #pls #FPGA #pls #xgmii #xaui #SFP #xfp #phy #сетевое оборудование #программирование #FPGA