Синхронизация является основным методом борьбы с конфликтами сигналов в цифровых цепях.

В отличие от обычных асинхронных триггеров, где в соответствии с таблицей истинности переключение происходит в те моменты времени, когда изменяются сигналы на информационных входах, синхронизирующие (тактируемые) триггеры имеют еще и управляющий вход (обычно обозначаемый как вход С).

в схемах).

Если сигнал на этом входе принимает разрешающее значение, то триггер работает как асинхронный.

Если сигнал на тактовом входе имеет запрещающее значение, то триггер не реагирует на изменение сигналов на информационных входах и сохраняет ту информацию, которую он записал, когда ему в последний раз была разрешена запись.

Существует несколько типов синхронизации:

- Путем синхронизации уровня сигнала

- По уровню сигнала «1»

- По уровню сигнала «0»

- Вдоль фронта

- На задней кромке

- Вдоль линии фронта

Синхронизация по уровню сигнала «1»

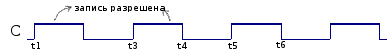

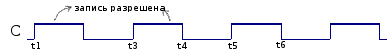

При сигнале С= «1» (в моменты от t2n-1 до t2n) запись разрешена, при С=0 – режим хранения.

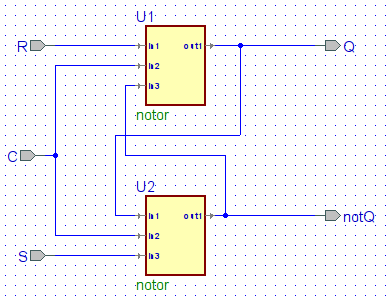

Проиллюстрируем это на примере RS-триггера с синхронизацией по элементам «или-нет» (U1, U2) с тремя входами.

Временная диаграмма срабатывания этого триггера (без считывания задержки на клапанах):

В логических элементах «или-нет» доминирующим сигналом является «1», поэтому при сигнале C = 1 сигналы на входах R и S блокируются и триггер будет находиться в режиме хранения.

При C = 0 схема работает как обычный RS-триггер.

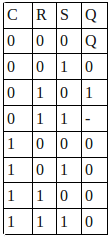

Таблица истинности этой схемы:

Синхронизация по уровню сигнала «0»

При сигнале С = «0» (в моменты от t2n до t2n+1) запись разрешена, при C = «1» — режим хранения.

Представим себе работу тактового триггера на основе синхронизирующего Е-триггера на логических элементах «и-не» (U9, U3, U4, U1, U6, U5) и «не» (U10, U7, U8).

, У2).

На схеме вентили «и-не» U9, U3 и инвертор U10 образуют обычный трехвходовой вентиль «и-не».

Аналогично для U1, U2, U6.

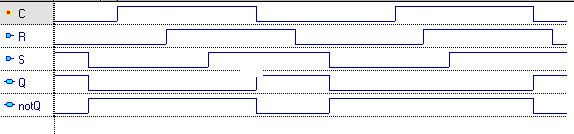

Временная диаграмма работы схемы:

Поскольку доминирующим сигналом в элементах «и-не» является «0», входящие сигналы С=0 блокируют сигналы R и S и поэтому триггер сохранит исходное состояние.

При C = 1 будет разрешено поступление сигналов со входов R и S и схема будет работать как обычный S-триггер (переходит в одиночное состояние): Сигналы C, S и notR поступают на входы U3, а C, notS и R – на входы U6. На RS-входы триггера (U4+U5) получаем сигналы (не S || R) и (S || не R).

Таблица истинности этой схемы:

Триггеры с синхронизацией уровня имеют один недостаток: входные сигналы могут измениться и вернуться в исходное положение, пока включен тактовый сигнал, в результате чего выходной сигнал схемы проходит через вход в течение определенного периода времени.

Теги: #схемотехника #схемы #CAD #дискретная математика #математика

-

Новая Концепция Olap

19 Oct, 24 -

Сервисное Меню В Benq E2220Hd

19 Oct, 24 -

Начать Работу С Роботами Должно Быть Легко.

19 Oct, 24 -

Минибар Для Программистов V0.1

19 Oct, 24 -

Hp Не Хочет Производить Камеры

19 Oct, 24 -

Где Найти Рекламодателя Для Стартапа?

19 Oct, 24 -

Сокобан На Javascript В 30 Строк

19 Oct, 24