Статья с сайта сумасшедшего DIY-инженера Крис Фентон

Встречайте ZedRipper, 16-ядерный зверь на базе Z80 с частотой 83 МГц, который настолько же портативен, насколько и непрактичен.

Это моя последняя попытка собрать компьютер просто для развлечения и удовлетворения сразу нескольких желаний:

Наконец, используйте гигантскую FPGA, которая у меня валялась.Сыграйте в альтернативную историю создания компьютеров, подойдя к вопросу многозадачности с точки зрения аппаратного обеспечения.

Собрать компьютер, на котором я мог бы писать забавные короткие программы в поезде на работу.

Создать платформу, на которой можно было бы проводить относительно простые эксперименты с компьютерной архитектурой.

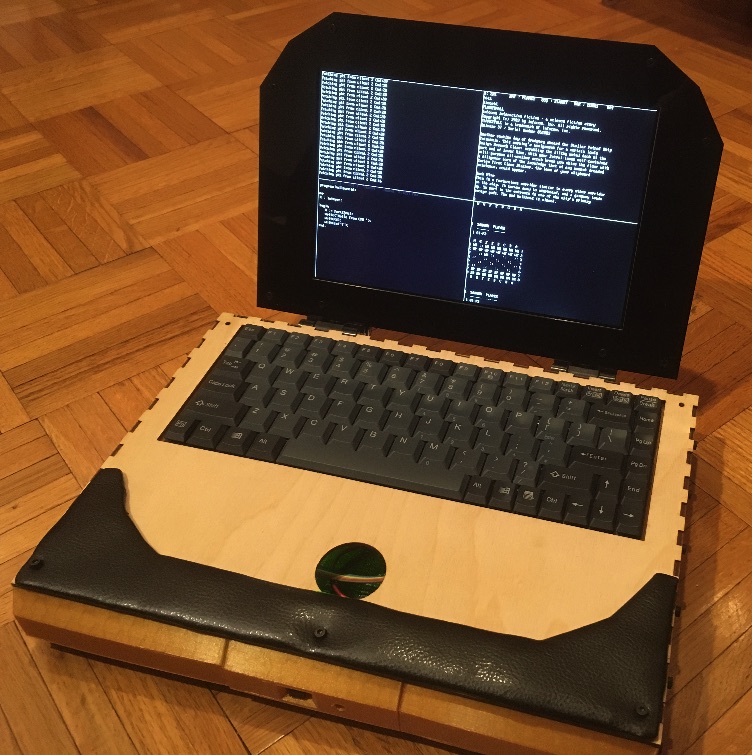

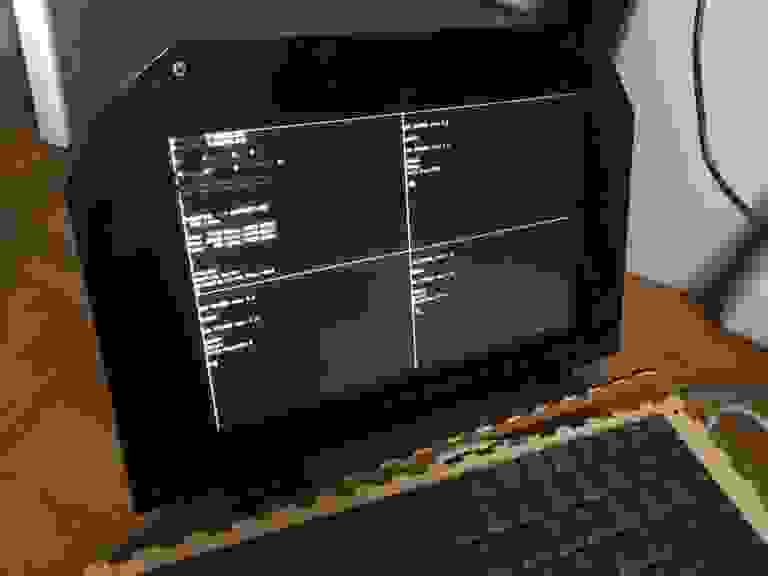

Гламурные фотографии

Если у вас нет времени читать листок текста о непрактичной компьютерной архитектуре.

Так что это за зверь?

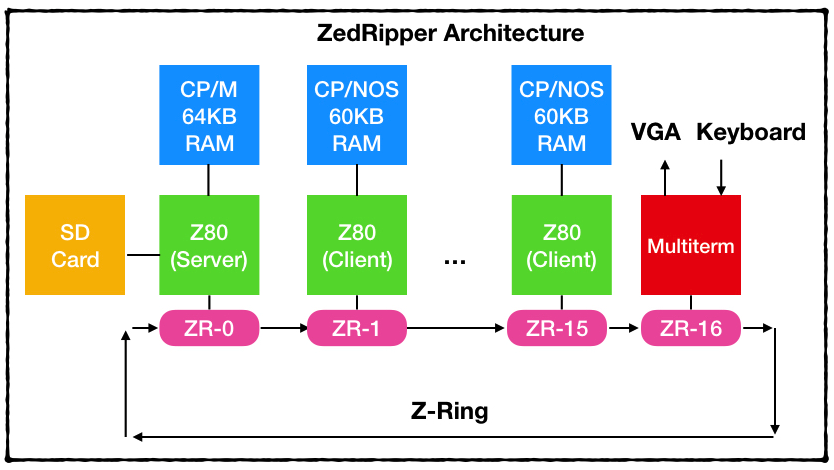

ZedRipper — результат попытки собрать самый крутой компьютер с CP/M 2.2: 16 процессоров Z80, работающих на частоте 83,33 МГц.

64 КБ выделенной памяти для каждого Z80. Терминальный ускоритель, соответствующий стандарту ANSI, с 16 выходами.

Все процессоры и устройства соединены полностью синхронной однонаправленной кольцевой сетью, работающей на частоте 83 МГц.

128 МБ памяти на SD-карте (16 x 8 МБ памяти в CP/M).

«Серверное» ядро, которое загружает CP/M 2.2 и запускает файловый сервер CP/NET (написанный на Turbo Pascal 3 на том же компьютере!), обеспечивая общий доступ к SD-карте.

15 «клиентских» ядер, запускающих CP/NOS из ПЗУ.

Каждый клиент имеет доступ к общему хранилищу, и каждый может запускать любую программу CP/M 2.2, не конкурируя за ресурсы с другими ядрами.

Другая дорога

Эти шахматы и Planetfall отвлекают меня от редактора Turbo Pascal? После моих приключений с портирование игр на Кайпро У меня сложилось удивительно приятное впечатление об этой примитивной операционной системе 40-летней давности, и у меня возникла идея, которую я решил развить: а что, если история повернётся в другую сторону, и ПК пойдут по пути развития с множеством процессоров, верно? прочь? Даже в 1980-е годы сами процессоры (а вскоре и оперативная память) были относительно недорогими, но многозадачность ПК основывалась исключительно на квантовании времени, при этом один большой ресурс (ОЗУ или ЦП) использовался совместно конкурирующими программами.

Аппаратное обеспечение не могло справиться с этим (и было очень сложно заставить программы хорошо работать в таких операционных системах, как DOS), пока мы не перешли в эпоху 386-х компьютеров и компьютеров с памятью более 4 МБ.

В процессе своего исторического увлечения компьютерами я наткнулся на кое-что очень интересное для меня: на ранних этапах разработки ОС КП/М поддерживал «сетевую» версию под названием CP/NET. Ее идея сегодня знакома большинству людей — установить в офисе одну-две «настоящие» машины с большими накопителями и принтерами, ресурсы которых будут совместно использоваться тонкими клиентами, терминалами с ЦП и оперативной памятью.

Каждый пользователь будет работать так, как если бы у него была собственная машина с CP/M и доступом к большим дискам и принтерам.

Как я уже упоминал, ЦП и ОЗУ (обычно у Z80 было 64 КБ DRAM) не были особенно дорогими, но все внешние компоненты, необходимые для создания полезного компьютера (диски, принтеры, мониторы и т. д.), добавлялись к общей стоимости.

.

В то время добавление нескольких ЦП/ОЗУ к компьютеру казалось несколько декадентским подходом к предоставлению нескольких ЦП и ОЗУ одному пользователю.

Даже CP/M пошел по пути разделения времени для ОС MP/M. Я обнаружил, что ближе всего к этому была компания Exidy — в 1981 году они выпустили свою машину Multi-NET 80, которая позволяла добавлять до 16 карт, каждая с Z80 и оперативной памятью.

Однако он был разработан для размещения до 16 отдельных пользователей, а не для одного пользователя, одновременно запускающего 16 программ.

Так близко…

Перенесемся на 40 лет вперед, и транзисторы действительно стали дешевле.

После закрытия лаборатории мне достались в наследство несколько ПЛИС чудовищных размеров (Stratix IV 530GX), и я задумался о том, что интересного можно сделать с одной из них.

В какой-то момент я наткнулся на очень интересный проект Гранта Сирла.

Мультикомп , и собрать работающую машину с CP/M и одним процессором оказалось довольно легко.

Но мне нужно было больше.

Я решил посмотреть, смогу ли я создать многоядерную машину CP/M с настоящей многозадачностью — ничего особенного, просто грубая сила.

Настройка и запуск программного обеспечения

В этом проекте я в основном сосредоточился на аппаратном обеспечении и не написал ни строчки ассемблерного кода.ЦП 0 загружается прямо из ПЗУ, которое я получил от Гранта, а остальные узлы загружаются из ПЗУ CP/NOS объемом 4 КБ, которое я получил от симулятора Atari. Оба ПЗУ ожидают подключения к последовательному терминалу через стандартный интерфейс, а клиенты CP/NOS ожидают подключения к серверу другого последовательного порта.

На таких больших ПЛИС легко разработать собственную логику.

Я разработал собственную логику декодирования адресов, благодаря которой Z-Ring для каждого CPU появляется в схеме отображения адресов там, где это необходимо.

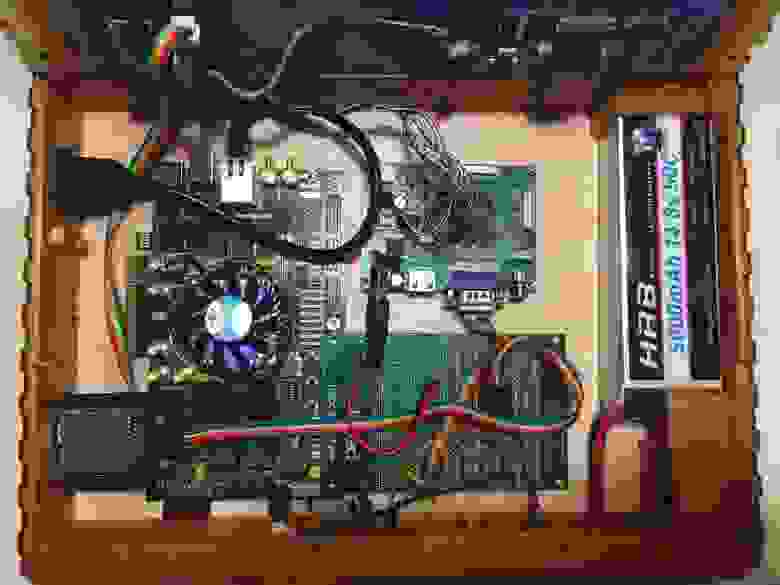

Внутренности

Сердцем ZedRipper является одна из огромных FPGA Stratix IV 530GX. Карта HSMC используется для отображения, получения данных от контроллера клавиатуры и подключения к SD-карте.

Для загрузки прошивки используется Ethernet, поэтому на боковой стороне корпуса есть такой порт, а также адаптер для SD-карты и слот для внешнего последовательного порта (пока не используется).

Клавиатура и контроллер

Клавиатура и отверстие на переднем плане, куда позже будет установлено устройство позиционирования У меня лежала компактная клавиатура PS/2 (из одного из моих старых проектов для ноутбуков), и я хотел подключить ее к входу-выходу 2,5 В моей FPGA. Я решил пойти простым путем и добавить к этому микроконтроллер Teensy 2.0.

Контроллер горячего клея в нижней части клавиатуры.

Это позволило перевести PS/2 в ASCII, а также для большего удобства легко сопоставить некоторые дополнительные клавиши (F1-F12) с «магическими» последовательностями команд терминала.

Затем контроллер выводит Z80 байтов через UART со скоростью 9600 бод (используя простой делитель напряжения, который изменяет напряжение от 5 В до 2,5 В для FPGA).

Учитывая, что данный проект был собран из разного хлама, валявшегося в моей мастерской, это было удобное решение, которое хорошо сработало.

Отображать

тап загрузки, в левом верхнем углу запущен сервер, и на отдельных ядрах работают три разные пользовательские программы Характеристики дисплея — 1280x800, 10,1 дюйма, он поддерживает VGA. FPGA использует простую сеть резисторов для вывода до 64 цветов (R2G2B2).

Для дисплея требуется таймер 83,33 МГц (1280x800 при 60 Гц), поэтому для простоты вся схема работает на этой частоте.

В проекте Гранта Multicomp был код VHDL для простого ANSI-совместимого терминала.

Я переписал его логику на Verilog, а затем разработал видеоконтроллер, поддерживающий 16 независимых терминалов, подключенных через один узел Z-Ring. Дисплей 1280x800 считается дисплеем 160x50 символов (со шрифтом 8x16), и каждый терминал работает как «спрайт» 80x25, который можно перемещать в любое место экрана (со списком приоритетов, регулирующим последовательность отрисовки терминалов).

Поскольку каждый терминал работает независимо от других, он имеет свой собственный конечный автомат с 2 КБ ОЗУ для символов и 2 КБ «атрибутной» ОЗУ (для хранения информации о цвете).

Каждый символ поддерживает 4-битный фон и цвет символа.

Поскольку все терминалы должны иметь одинаковый отступ, а «ячейка» 8x16 может содержать только один символ, все терминалы могут использовать одно и то же ПЗУ размером 2 КБ, содержащее шрифт. В общей сложности логика дисплея использует около 66 КБ блочной оперативной памяти.

В целом, это очень простой оконный менеджер для моих терминалов CP/M, почти полностью работающий на аппаратном уровне.

Это одна из самых богатых областей для исследований — пока переставлять терминалы может только ЦП сервера, но у меня есть далеко идущие планы добавить устройство позиционирования типа мыши, которое позволит, используя только аппаратное обеспечение, перетаскивать окна и изменять их.

приоритет отображений.

Поскольку контроллер терминала является лишь одним из узлов Z-Ring (и этот интерфейс очень легко перенаправить на любой из Z80), в планы на будущее входит, возможно, добавление «полноэкранного» терминала 160x50 (возможно, в качестве «фона») и настоящее отображение цветов 1280x800x64 с использованием быстрой внешней SRAM на плате.

Z-кольцо

Как соединить вместе несколько Z80? За время своей работы я усвоил одну вещь: развивать сети сложно.Общими целями этой сети были: Простая реализация.

Простой интерфейс.

Произвольная расширяемость.

Адекватная производительность.

Как я уже упоминал, мои Z80 предполагалось подключать к последовательным портам, поэтому создать интерфейс было довольно легко — его просто нужно было замаскировать под последовательный порт! По сути, Z-Ring — это синхронная однонаправленная кольцевая сеть, которая использует «кредиты» для управления потоком.

Каждый узел имеет 1-байтовый входной буфер для каждого другого узла в сети.

После сброса каждый узел имеет 1 «кредит» для каждого другого узла в сети.

Конструкция параметризована, поэтому ее легко масштабировать до сотен узлов с добавлением очень небольшого количества логики, но сегодня Z-Ring поддерживает до 32 узлов (поэтому каждому узлу требуется 32-байтовый буфер).

Сама «шина» состоит из допустимого бита, идентификатора «источника», идентификатора «цели» и 1-байтовой полезной нагрузки (19 бит).

Думаю, это было бы довольно легко реализовать с помощью TTL-логики (если человек вернулся в 1981 год и не нашел ПЛИС).

Каждый «узел» имеет 2 конвейера для триггеров шины — этап 0 и этап 1 — и когда сообщение поступает, оно ждет, пока этап 0 не опустеет, а затем переходит на этап 1. Сообщения вводятся в «исходный» узел и перемещаются.

по кольцу, пока не достигнут цели, после чего они попадают в соответствующий буфер и обновляют флаг «готовность данных».

Когда принимающий узел читает буфер, он повторно вводит исходное сообщение, которое продолжает путешествовать по кольцу, пока снова не достигнет источника, возвращая «кредит».

Если вы отправите посылку на несуществующий адрес, кредит будет возвращен автоматически, пройдя полный круг.

Поскольку каждая остановка на кольце состоит из двух этапов конвейера и противодавление отсутствует, для доставки каждого сообщения требуется не более 2*(количество узлов) циклов.

Текущая реализация имеет 17 узлов (16 ЦП + контроллер дисплея/клавиатуры) и работает с таймером 12 нс, поэтому для доставки сообщения и возврата кредита требуется около 400 нс.

Контроллер дисплея может отправлять трафик со своей скоростью поступления, поэтому каждый ЦП имеет пропускную способность 2-2,5 Мбит/с до своего терминала (шина пропускает достаточно для поддержки всех 16 ЦП), что довольно много для терминалов.

В текущей конфигурации все работает нормально, но можно внести несколько очевидных улучшений: Углубите приемные буферы, что увеличит пропускную способность узлов — на ПЛИС имеется много свободных блоков по 1 КБ ОЗУ, что позволит поддерживать 32 узла по 32 кредита каждый, поэтому теоретически каждый ЦП может насыщать шину.

Добавить поддержку адресного режима.

Добавление 16-битных (или более) адресов позволит обеспечить прямой доступ к памяти (DMA) (и добавить DMA к каждому узлу будет легко).

ПЛИС имеют огромное количество дополнительного оборудования (несколько мегабайт статической оперативной памяти и около гигабайта DDR3).

Добавьте управление потоком (и буферизацию) между узлами.

Но все это может подождать до лучших времен.

Питание!

Плате разработки FPGA требуется входное питание 12–20 В, дисплею — 12 В, а клавиатуре и контроллеру — 5 В.Удобно, что ПЛИС имеет стабилизаторы на 3,3, 5 и 12 В, которые довольно легко подключить, поэтому ПЛИС получает питание напрямую от литий-полимерного аккумулятора емкостью 5000 мАч с напряжением 14,4 В, а затем распределяет питание на все остальные устройства.

Одной из проблем было то, что мне не хотелось каждый раз разбирать ноутбук, чтобы зарядить его, но у аккумулятора был обычный разъем питания +/-, а также «балансный» разъем, который подключался к каждой отдельной ячейке.

.

Мое далеко не идеальное решение заключается в том, что кнопка питания переключает соединение аккумулятора между питанием FPGA и разъемом для зарядки, расположенным в углублении, закрытом сдвижной крышкой.

Это не очень удобно, но можно просто сдвинуть крышку и вытащить разъемы для подключения к зарядному устройству без использования шестигранных ключей.

Зарядка выглядит странно

Я не проверял батарею тщательно, но ее хватает как минимум на 3 часа (более чем достаточно, чтобы покрыть поездку на поезде).

Скорее всего, без какой-либо оптимизации потребления его хватит примерно на 6 часов.

Он не поддерживает использование во время зарядки, но аккумулятор работает достаточно долго, чтобы с ноутбуком не было проблем.

Рамка

Корпус стандартной «хакерской» конструкции представляет собой сочетание 3-миллиметровой фанеры, вырезанной лазером, и пластика, напечатанного на 3D-принтере.Я подпружинил шарниры экрана, так что он действительно выглядит как обычный, хотя и несколько медленный ноутбук.

Я хотел придать ему вид 1980-х годов, поэтому верхние углы экрана напоминают Cray, а также имеется подставка для запястий из искусственной кожи.

Край фанеры, вырезанной лазером, очень неприятен для рук, поэтому эта подставка оказалась на удивление функциональной.

Скорость

Специально для CP/M я не пробовал никаких тестов (предполагаю, что они существуют, но особо особо не искал).Поскольку эта машина была создана для написания программ на Turbo Pascal, я попробовал провести несколько микротестов скорости.

В результате получилось 15-35 тысяч операций с плавающей запятой в секунду (при использовании 48-битного типа Real в TP) и около 1 миллиона целочисленных операций в секунду (при использовании 16-битного типа Integer).

Неплохо для 8-битного процессора и достаточно удобной среды программирования.

Интересным будущим проектом может стать разработка ускорителя с плавающей запятой.

Утилизация ПЛИС

Вся логика, как я уже говорил, достаточно легковесна и занимает всего около 7% ресурсов чипа (хотя 40% всей блочной оперативной памяти и 100% оперативной памяти M144k).

Комбинированные ALUT 31 808 / 424 960 (7%)

Память ALUT 0/212 480 (0%)

Выделенные логические регистры 10 231/424 960 (2%)

Использование логики 10%

Всего регистров 10231

Всего бит блочной памяти 9 005 056 / 21 233 664 (42%)

Блок DSP 18-битные элементы 0/1024 (0%)

Планы на будущее

В моих ближайших планах (то есть фурнитура уже в мастерской, осталось только найти время на пайку): Нарисуйте все это.Ноутбук сделан из фанеры, и очень хочется его чем-нибудь прикрыть.

Устройство позиционирования джойстикового типа.

Подключите его к контроллеру клавиатуры.

Отслеживание батареи.

АЦП на контроллере клавиатуры позволял достаточно легко контролировать аккумулятор, чтобы я знал, каков уровень заряда.

Wi-Fi – у меня есть ESP32, на котором можно запустить Zimodem! В сочетании с режимом точки доступа телефона это должно позволить мне выходить в Интернет, находясь в пути.

Есть хорошие терминальные приложения для CP/M, но было бы здорово написать что-то вроде IRC-клиента или простого веб-браузера.

Также будет удобно использовать протокол передачи файлов Кермит на современном компьютере под управлением Linux. Доступный снаружи последовательный порт для подключения к другой машине (разъем для него уже распечатан, его нужно только припаять).

Светодиод, показывающий текущий статус.

Спереди для него уже есть отверстие - сейчас планирую подключить его к сигналу доступа к SD-карте.

В долгосрочной перспективе я рассчитываю на различные идеи аппаратного обеспечения, с которыми будет интересно поэкспериментировать: Насколько быстро можно разогнать Z80? Первый шаг — отделить скорость процессора от пиксельного таймера, но также будет интересно попробовать применить к Z80 современные компьютерные технологии (конвейеры, переименование регистров, предсказатель ветвей и т. д.).

Возможно, было бы интересно добавить специальные ускорители для таких вещей, как операции с плавающей запятой.

На чипе 1024 неиспользуемых блока DSP, и я не думаю, что кто-то когда-либо пытался построить в TP ускоритель для 48-битного формата Real. Используйте существующее оборудование! У меня еще много неиспользованной памяти, а именно: 512 МБ DDR3 SDRAM с 64-битной шиной данных 128 МБ DDR3 SDRAM с 16-битной шиной данных Две SRAM QDR II+ емкостью 4 МБ с 18-битными шинами данных.

флэш-память 64 МБ 2 МБ SSRAM Улучшите свое видео! Первым шагом является добавление поддержки «полноэкранного» терминала 160х50 и возможности масштабирования до обычного терминала 80х25 в 2 раза.

Используя внешнюю SSRAM, можно будет легко добавить 6-битный режим 1280x800. Расширьте возможности текущего терминала.

Я думаю, что смогу добавить совместимость с терминалом, таким как ADM-3A (и добавить поддержку графики), который использует Kaypro/84, тогда у меня будет доступ к более широкому спектру программного обеспечения (и мне не придется портировать DD9).

Полученные результаты

Пока машина работает всего несколько дней, но могу сказать, что она мне очень нравится.Тап приятный и четкий, клавиатура большая и удобная, корпус громоздкий, но весит мало (и помещается в рюкзак).

Ноутбук даже оказался на удивление эргономичным для работы в поезде.

Я думаю, что я на правильном пути.

Возможность открывать текстовый редактор в одном окне для заметок и отладку кода TP в другом чрезвычайно удобна (или возможность делать заметки во время игры в Zork!).

Чувствуется, что такой подход к созданию недорогих многозадачных компьютеров на базе CP/M мог бы существовать.

Хотите построить такой?

Пока что у меня нет простого способа извлечь файлы из машины, поэтому самая полезная часть программного обеспечения (файловый сервер CP/Net, написанный на Turbo Pascal) оказалась в ловушке.Оставайтесь с нами и следите за новостями (или пишите мне электронная почта , если уж совсем не терпится).

В какой-то момент я, вероятно, присоединюсь к 21 веку и открою аккаунт на github. Увы, все упирается в то самое «свободное время».

Теги: #Компьютерное железо #Сделай сам или Сделай сам #ноутбук #CP/M #z80 #cp/net

-

Миграция Данных В Sap Business One

19 Oct, 24 -

Классификатор Коворкингов

19 Oct, 24 -

Идеальная Cms, Какая Она?

19 Oct, 24