Программируемая логическая интегральная схема (FPGA) может реализовывать произвольную логику, от микропроцессора до генератора видеосигналов или майнера криптовалюты.

FPGA состоит из множества логических блоков, каждый из которых обычно состоит из триггера и логической функции, а также сети проводов, соединяющих логические блоки.

Что делает FPGA особенным, так это то, что это программируемое оборудование, вы можете настроить каждый логический блок и соединения между ними.

В результате вы можете построить сложную цифровую схему без физического подключения каждого логического элемента и триггера, что потребует затрат на разработку специальной интегральной схемы.

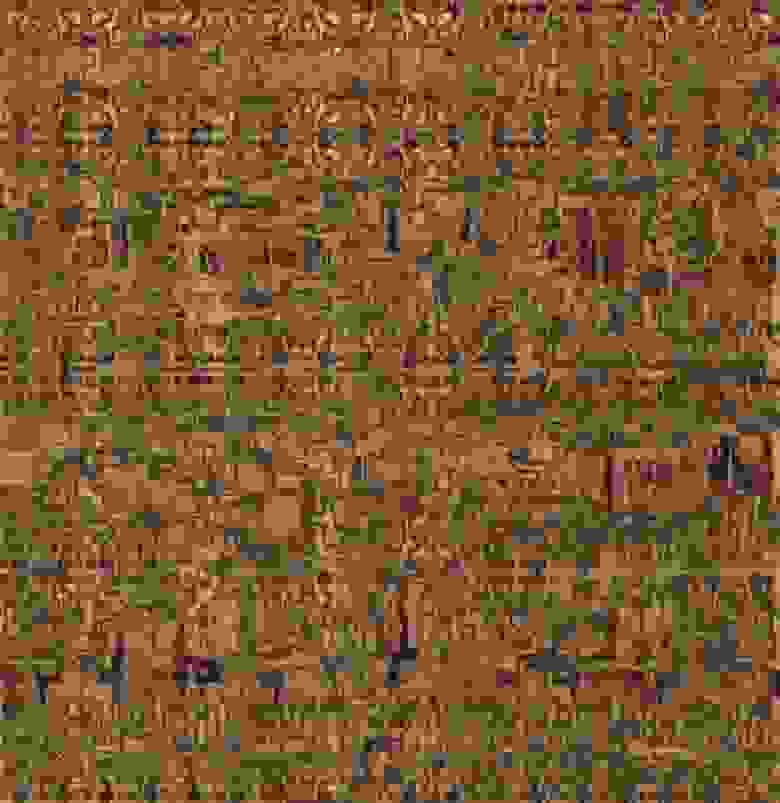

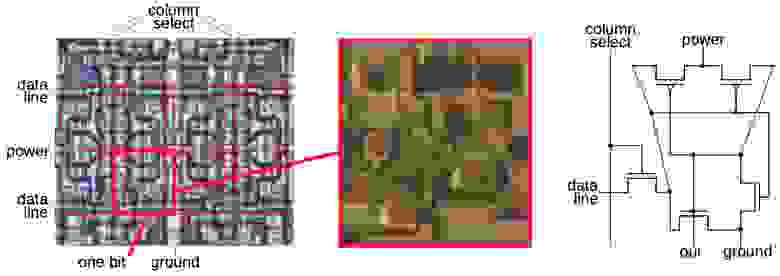

На фото один из 64 блоков микросхемы XC2064. Слои металлизации сняты, мы видим лежащие под металлизацией кремниевые и поликремниевые транзисторы.

Посмотреть фото в большем масштабе можно по ссылке: кремнийpr0n .

FPGA была изобретена Россом Фрименом, соучредителем Xilinx, в 1984 году, первым чипом FPGA был XC2064. Он был намного проще современных ПЛИС, содержащих всего 64 логических блока по сравнению с тысячами и миллионами современных ПЛИС, и его создание привело к возникновению миллиардной индустрии.

XC2064 настолько важен, что его включили в Зал славы IC. Я провел реверс-инжиниринг XC2064 и в этом посте в общих чертах объясняю его внутреннюю структуру и то, как он программируется с помощью битового потока.

Росс Фриман Росс Фримен трагически умер от пневмонии в возрасте 45 лет, через пять лет после изобретения FPGA. В 2009 году Фримен был помещен в Зал славы изобретателей .

Ксилинкс Xilinx была одной из первых компаний, не имеющих собственных производственных мощностей.

В отличие от большинства полупроводниковых компаний, которые проектировали и производили полупроводники, Xilinx только разработала конструкцию чипа, а производством занималась другая компания.

Xilinx использовала продукцию Seiko Epson Semiconductor Division (часы Seiko и принтеры Epson).

ХС2064 Нестандартные интегральные схемы имеют проблему высокой стоимости и длительного времени (месяцы или годы) на разработку и производство чипа.

Одним из решений является программируемое логическое устройство ( Программируемые логические устройства ,PLD), микросхема с матрицей логических вентилей, которую можно запрограммировать для выполнения различных функций, которая была разработана вокруг 1967 год. Первоначально их программировали с помощью маски, металлический слой чипа проектировали под требуемую функциональность, изготавливали маску и изготавливали чип по спецификациям.

Позже чипы, содержащие ППЗУ, смогли программироваться пользователем, на микросхеме выгорели перемычки, а также появились микросхемы со ППЗУ, которые можно было перепрограммировать.

Программируемые логические устройства имели множество маркетинговых названий, таких как Программируемая логическая матрица , Логика программируемых массивов (1978), Общая логика массива И Незафиксированный логический массив .

По большей части такие устройства состояли из логических элементов, соединенных в схему «суммы произведений», некоторые из них содержали триггеры.

Основным нововведением, которое представили FPGA, были программируемые соединения между логическими блоками, а не фиксированная архитектура, и логические блоки, содержащие триггеры.

Подробный обзор истории FPGA и эффекта масштабируемости см.

Три века FPGA: ретроспектива первых тридцати лет технологии FPGA "Также см" Краткая история FPGA ".

Xilinx XC2064 — первый чип FPGA. Взято отсюда: кремнийpr0n .

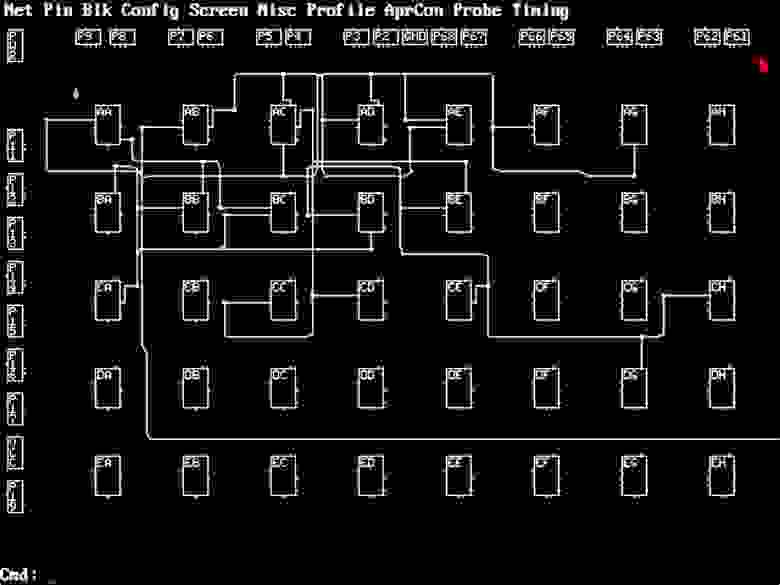

В настоящее время FPGA программируются на языках описания оборудования, таких как Verilog или VHDL, но в то время Xilinx предоставила собственное программное обеспечение для разработки, приложение MS-DOS под названием XACT, по огромной цене в 12 000 долларов.

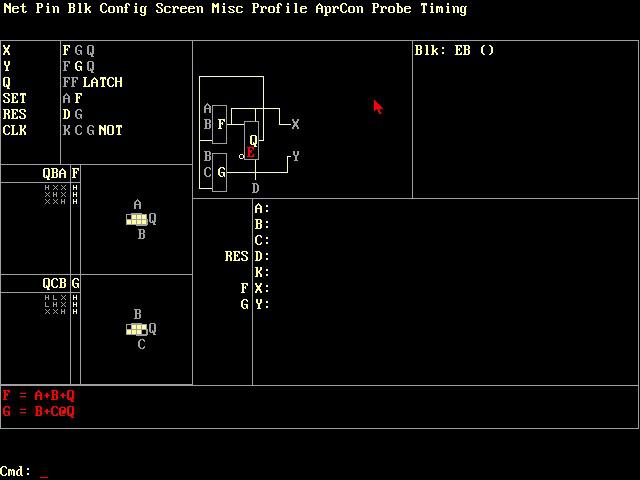

XACT работал на более низком уровне, чем современные инструменты: пользователь определял функцию каждого логического блока, как показано на скриншоте ниже, и связи между логическими блоками.

XACT маршрутизировал соединения и генерировал файл конфигурации (битовый поток), который загружался в FPGA.

Скриншот XACT. Две таблицы F и G реализуют уравнения, показанные в нижней части экрана, с картой Карно, показанной выше.

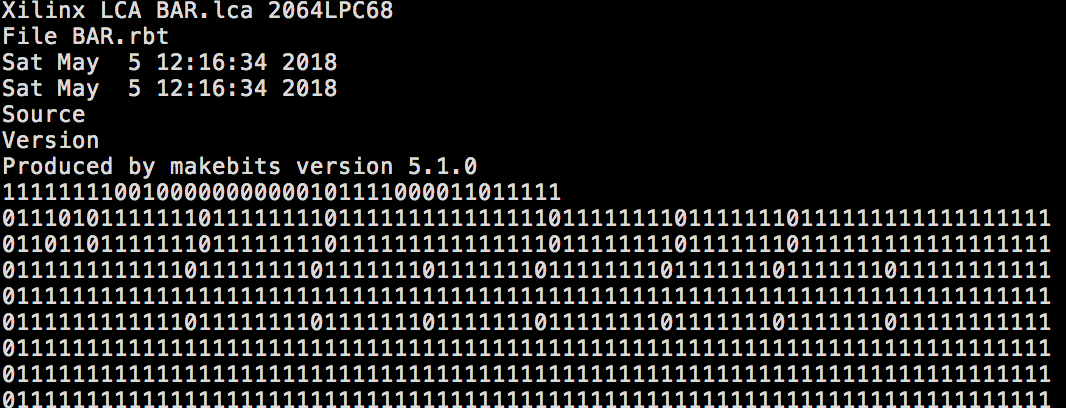

FPGA была настроена с использованием битового потока — последовательности битов в собственном формате.

Если вы посмотрите на битовый поток XC2064 (ниже), вы увидите загадочную смесь шаблонов, которые повторяются нерегулярным образом и разбросаны по всему битовому потоку.

Однако изучение физических схем ПЛИС раскрывает нам структуру данных битового потока и ее можно изучить.

Часть битового потока, созданного XACT.

Как работает FPGA?

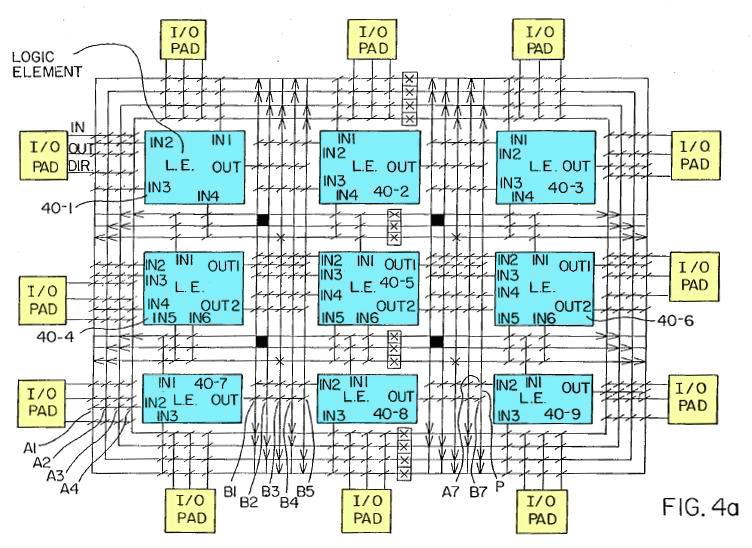

На рисунке ниже, взятом из оригинального патента на FPGA, показана базовая структура FPGA. Эта упрощенная FPGA имеет всего 9 логических блоков (отмечены синим цветом) и 12 портов ввода-вывода.Сеть межсоединений соединяет компоненты вместе.

Установив на соединениях переключатели (диагональные линии), логические блоки можно соединять друг с другом и с портами ввода-вывода.

Каждый логический элемент может быть запрограммирован на выполнение требуемой логической функции.

В результате такой программируемый чип может реализовать любое устройство, которое помещается в доступное пространство.

Патент на ПЛИС , логические блоки (LE), связанные друг с другом.

Конфигурируемые логические блоки (CLB, конфигурируемый логический блок)

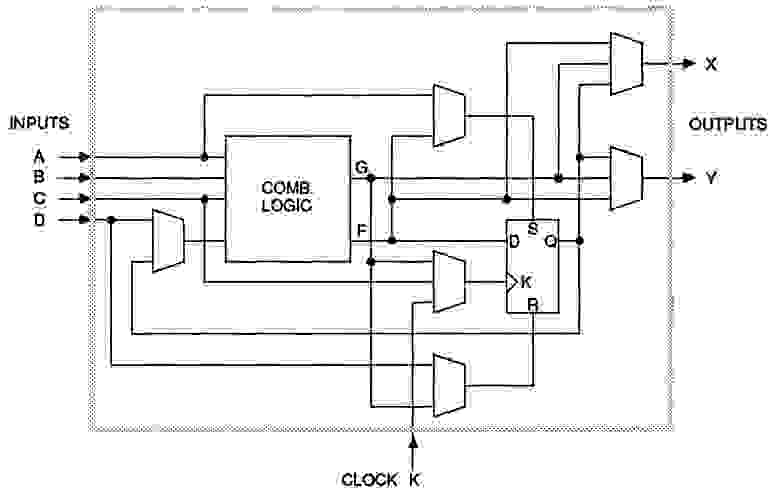

Хотя на рисунке выше показано 9 CLB, у XC2064 их 64 CLB. На рисунке ниже показана структура CLB. CLB имеет 4 входа (A, B, C, D) и два выхода (X и Y).Между ними находится комбинационная логика, которую можно запрограммировать на выполнение любой желаемой логической функции.

CLB также содержит триггер, наличие которого позволяет реализовать счетчики, регистры сдвига, конечные автоматы и другие схемы сохранения состояния.

Трапеции обозначают мультиплексоры, которые можно запрограммировать на передачу сигнала с любого из входов.

Мультиплексоры позволяют настроить CLB под конкретную задачу, выбрав определенные сигналы для управления триггером и выходами.

Настраиваемый логический блок в XC2064, взят отсюда: техническая спецификация .

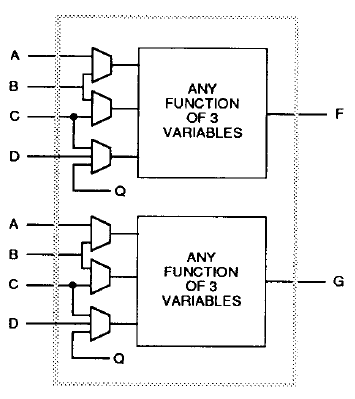

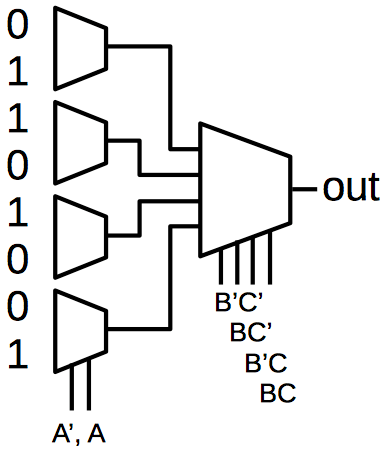

Вам может быть интересно, как комбинационная логика реализует произвольные логические функции.

Есть ли выбор между набором элементов AND, OR, XOR и т.д.? Нет, здесь используется хитрый трюк, называемый справочной таблицей (LUT), которая на самом деле является таблицей истинности для функции.

Например, функция трех переменных определяется таблицей из 8 строк.

LUT содержит 8 бит памяти.

Мы можем реализовать любую логическую функцию с тремя входами, сохранив эти три бита.

Посмотреть таблицы Таблицы представлений в XC2064 сложнее, чем просто таблицы.

Каждый CLB содержит две справочные таблицы с тремя записями.

Табличные входы XC2064 оснащены программируемыми мультиплексорами, позволяющими выбрать 4 различных потенциальных входа.

Кроме того, две таблицы поиска можно объединить для создания функции четырех переменных и других комбинаций.

Логические функции в FPGA XC2064 реализованы с использованием справочных таблиц.

Из документации.

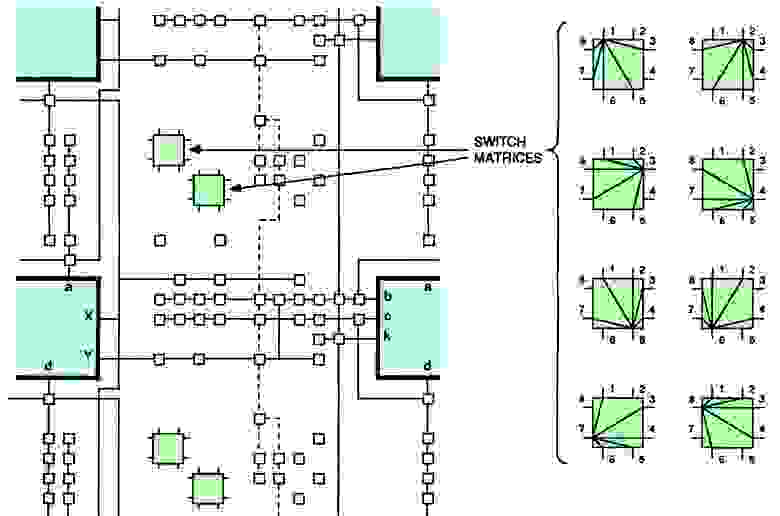

Соединения

Следующий ключевой аспект FPGA — это соединения, которые можно запрограммировать для переключения CLB различными способами.Связи сложны, но грубое описание состоит в том, что между всеми CLB существуют сегменты вертикальных и горизонтальных связей.

Вы можете соединять CLB горизонтальными и вертикальными линиями и создавать произвольные соединения.

Более сложный тип подключения – «матрица переключения».

Каждая матрица имеет 8 контактов, которые можно соединять друг с другом (почти) произвольными способами.

На рисунке ниже показана структура каналов XC2064, которая обеспечивает соединения между логическими блоками (синие) и линиями ввода-вывода (желтыми).

На вставке показаны детали механизма подключения.

Зеленые прямоугольники — это матрицы переключателей с 8 контактами, а маленькие квадраты — это программируемые точки подключения.

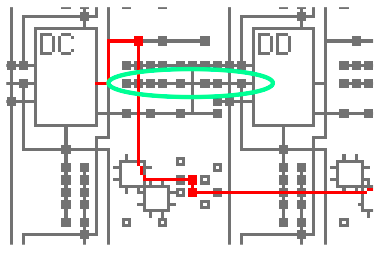

FPGA XC2064 имеет матрицу CLB 8x8. Каждый CLB имеет имена от AA до HH.

Соединение может переключать, например, выход блока постоянного тока на вход блока DE, как показано ниже.

Красная линия показывает путь прохождения сигнала, а маленькие красные квадраты показывают активированные точки подключения.

После выхода из блока постоянного тока сигнал направляется к первой точке подключения на 8-контактном переключателе (зеленый), который проходит через две точки подключения и еще один переключатель с 8 входами (неиспользуемые вертикальная и горизонтальная линии не показаны).

Обратите внимание, что соединение довольно сложное; даже такой короткий путь использует четыре точки подключения и два переключателя.

Пример маршрутизации сигнала с выхода блока DC на блок DE.

На снимке экрана ниже показано, как выполняется трассировка в программе XACT. Желтые линии показывают соединения между логическими блоками.

По мере увеличения количества сигналов становится все труднее устанавливать соединения без конфликтующих путей.

XACT автоматически отслеживает, но трассировки также можно редактировать вручную.

Скриншот программы XACT. Это программа MS-DOS, управляемая с помощью клавиатуры и мыши.

Выполнение

Далее мы рассмотрим внутреннюю схему XC2064, реконструировав ее по фотографии кристалла.Имейте в виду, что для этого необходимо некоторое знакомство с XC2064. Фотография кристалла Для анализа XC2064 я использовал собственную фотографию кристалла XC20186, а также фотографии кристаллов XC2064 и XC2018 от Siliconepr0n. Анализировать ПЛИС по изображениям оптического микроскопа сложно, поскольку они имеют два слоя металлизации.

Джон Макмастер использовал электронный микроскоп, чтобы устранить двусмысленность, вносимую этими слоями.

На фото ниже показано, как выглядит верхний слой металлизации под электронным микроскопом.

Фотография XC2064, сделанная электронным микроскопом, любезно предоставлена Джоном МакМастером.

ХС2018 FPGA Xilinx XC2018 (на фото ниже) имеет 100 ячеек, как и XC2064. Внутри он использует те же плитки, что и 64-ячеечный XC2064, но они расположены в сетке 10x10, а не 8x8. Формат битового потока XC2018 очень похож, но больше по размеру.

ПЛИС XC2018. Справа корпус был снят, обнажив кремниевый кристалл.

На кристалле слабо виден рисунок плиток.

На фото ниже вы можете увидеть сравнение кристалла XC2064 и XC2018. Кубики очень похожи, за исключением того, что у более крупного чипа есть два дополнительных ряда и два дополнительных столбца.

Сравнение кристаллов XC2064 и XC2018. Изображения масштабированы так, чтобы размеры плиток совпадали, не знаю, как соотносятся физические размеры кристаллов.

Фотографии кристаллов взяты из силиконпр0н.

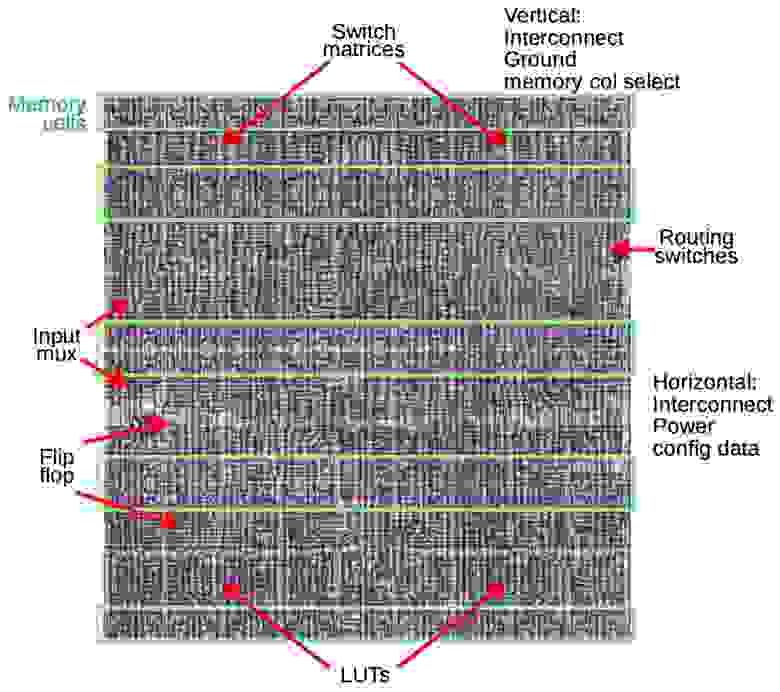

Ниже фото кристалла XC2064. Основная часть ПЛИС представляет собой матрицу из блоков 8х8, каждый из которых содержит логический блок и окружающие его схемы.

Хотя на диаграмме FPGA логические блоки (CLB) показаны как отдельные объекты схемы межсоединений, на самом деле это реализовано не так.

Фактически каждый логический блок и его окружение реализованы как один узел — тайл.

(Если быть точным, плитка включает в себя соединения вверху и слева от каждого CLB).

Компоновка блоков микросхемы XC2064. Взято отсюда: кремнийpr0n .

Расположенные по бокам интегральной схемы блоки ввода-вывода обеспечивают связь с внешним миром.

Они подключены к контактам чипа, которые показаны в виде маленьких зеленых квадратов, и подключены к контактам корпуса чипа.

На чипе имеются буферы (зеленые): два вертикальных и два горизонтальных.

Эти буферы усиливают сигнал, прошедший через чип на большое расстояние, и уменьшают задержку.

Регистр вертикального сдвига (розовый) и схема выборки горизонтального столбца используются для загрузки потока битов в чип, как показано ниже.

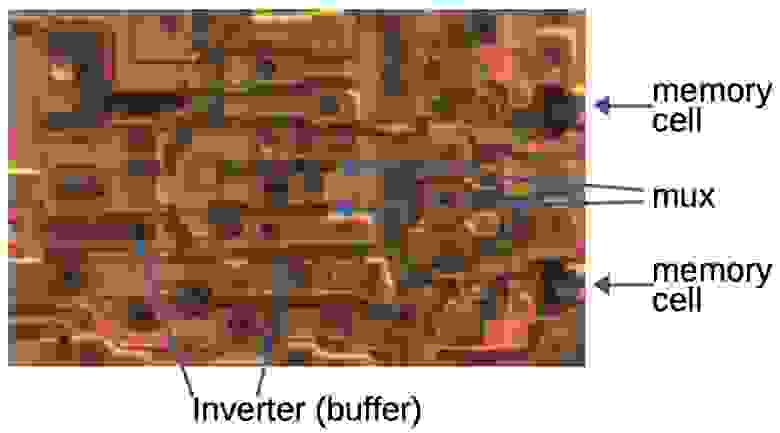

Внутри плитки

На рисунке ниже показана структура одного тайла XC2064, чип содержит 64 таких тайла, упакованных в один чип.Около 40% каждого тайла занимают ячейки памяти (показаны зеленым), в которых хранятся биты конфигурации.

Верхняя треть (приблизительно) плитки содержит схемы подключения: две матрицы переключателей и несколько отдельных переключателей каналов.

Ниже расположен логический блок.

Основной частью логического блока является входной мультиплексор, триггер и таблица поиска.

Тайл соединен с соседями через горизонтальные и вертикальные линии связи, а также подключен к шинам питания и заземлению.

Биты данных конфигурации поступают в ячейки памяти по горизонтали, а вертикальные сигналы выбирают конкретный столбец для загрузки.

Одна плитка FPGA, показывающая важные функциональные узлы.

Транзисторы

FPGA реализована на основе КМОП-логики, построенной на NMOS- и PMOS-транзисторах.Транзисторы выполняют две основные роли в FPGA. Во-первых, их комбинации составляют логические элементы.

Во-вторых, транзисторы используются в качестве переключателей, через которые проходит сигнал, например, для формирования связей между блоками.

Транзистор, выполняющий эту роль, называется проходным транзистором.

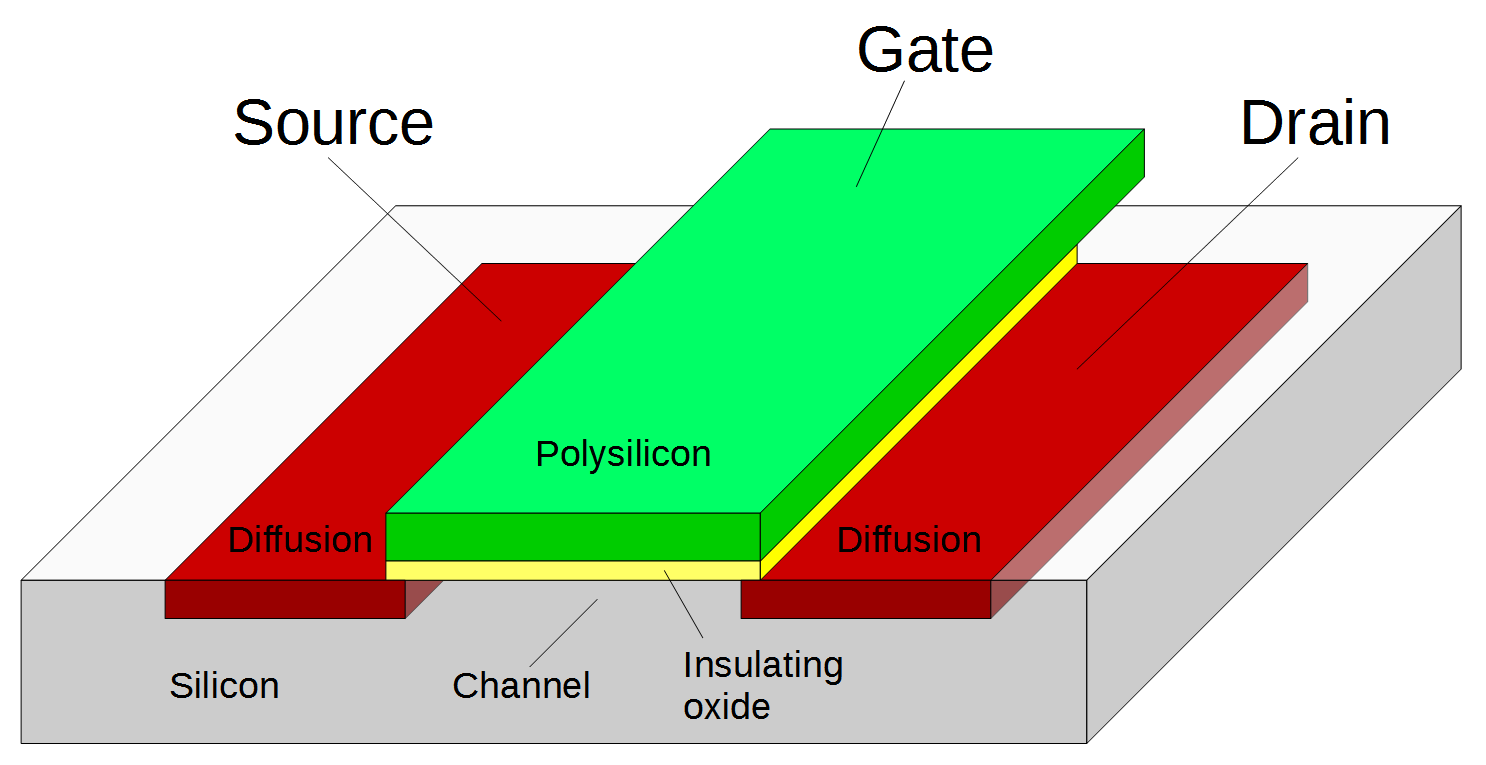

На рисунке ниже показана базовая структура МОП-транзистора.

Две секции кремния легированы примесями для создания стока и истока.

Между ними находится затвор, который включает и выключает транзистор и управляет током между стоком и истоком.

Затвор изготовлен из особого типа кремния, называемого поликремнием, и изолирован от кремния под ним тонким слоем оксида.

Над ним расположены два слоя металлизации, обеспечивающие соединения цепей.

Структура МОП-транзистора

На фотографии кристалла мы можем увидеть, как выглядит транзистор под микроскопом.

Затвор из поликремния представляет собой змеевидную линию между двумя легированными областями кремния.

Кружочки — это переходные отверстия, соединяющие кремний и металлический слой (на этой фотографии он удален).

MOSFET-транзистор на микросхеме FPGA.

Битовый поток и конфигурационная память

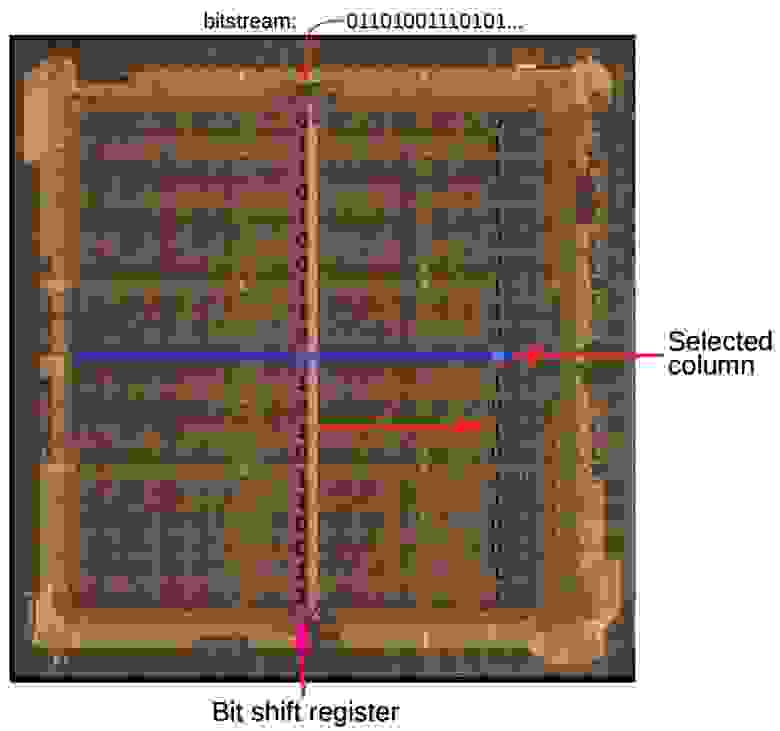

Информация о конфигурации в XC2064 хранится в ячейках памяти конфигурации.FPGA не использует для этого блочную память; вместо этого память конфигурации распределяется по чипу в виде решетки 160x71, где каждый бит размещается рядом со схемой, которой он управляет. На рисунке ниже показан битовый поток конфигурации, загруженный в FPGA. Битовый поток загружается в сдвиговый регистр, который находится в середине чипа (розовый).

После загрузки 71 бита в сдвиговый регистр схема выборки столбца (синяя) выбирает нужный столбец памяти, и биты загружаются в столбец параллельно.

Затем следующий 71 бит загружается в сдвиговый регистр и выбирается следующий столбец слева.

Процесс повторяется для всех 160 столбцов FPGA, и весь битовый поток загружается в FPGA. Использование сдвигового регистра устраняет необходимость в больших схемах адресации памяти.

Как битовый поток загружается в FPGA. Показанные биты являются условными; фактическое хранилище битов гораздо более плотное.

Три столбца справа уже загружены, четвертый загружается.

Фото кристалла взято отсюда: кремнийpr0n .

Важно то, что поток битов распределяется по чипу именно в том порядке, в котором биты появляются в файле: упаковка битов в потоке битов соответствует их физическому расположению на чипе.

Как мы покажем ниже, каждый бит хранится в FPGA рядом со схемой, которой он управляет. таким образом, формат файла битового потока напрямую определяется размещением аппаратных схем.

Например, если между тайлами есть разрыв, и в нем есть буфер, такой же разрыв будет и в битовом потоке.

Структура битового потока не зависит от абстракций программного обеспечения, таких как поля в таблицах данных или блоках конфигурации.

Понимание битового потока требует мышления с точки зрения аппаратного обеспечения, а не программного обеспечения.

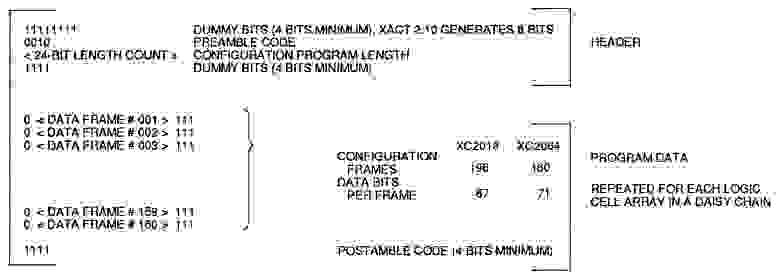

Битстрим Хотя битовый поток напрямую отображается в ячейки аппаратной памяти, файл битового потока (.

RBT) имеет некоторое форматирование, как показано ниже.

Формат данных битового потока из документации.

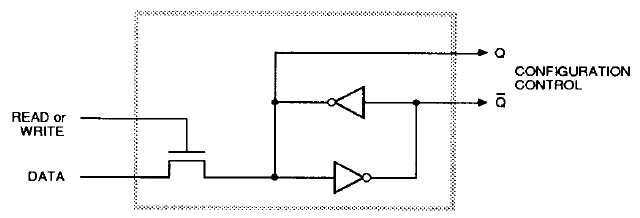

Каждый бит конфигурационной памяти реализован, как показано ниже.

Каждая ячейка памяти состоит из двух инверторов, соединенных в шлейф.

такая схема имеет два устойчивых состояния и может хранить один бит: либо верхний инвертор находится в состоянии 1, а нижний — в состоянии 0, или наоборот. Для записи в ячейку активируется проходной транзистор слева, пропускающий сигнал.

Сигнал по линии данных просто дергает инвертор, записывая нужный бит. (Вы также можете считывать данные конфигурации, используя ту же схему.

) Выход Q и инвертированный Q управляют определенной функцией в FPGA, такой как замыкание межсоединения, получение бита из справочной таблицы или управление триггером.

В большинстве случаев используется только выход Q. Ячейка SRAM Память конфигурации реализована с использованием статических ячеек памяти (SRAM).

Технически эта память не является оперативной памятью, поскольку доступ к ней осуществляется последовательно через сдвиговый регистр, но люди все равно называют ее SRAM. Эти ячейки памяти имеют пять транзисторов и известны как 5T SRAM. Остается сомнительным, есть ли в битовом потоке неиспользуемые биты.

Вероятно, многие биты не используются.

Например, каждый тайл имеет блок размером 18х18 бит, из которых 27 бит не используются.

Взгляд на микросхему показывает, что ячейки памяти, соответствующие неиспользуемым битам, полностью удалены, а их пространство на микросхеме используется для других схем.

На фотографии кристалла ниже видно, что 9 бит использованы и один отсутствует.

Ячейки памяти с пробелом, в котором отсутствует одна ячейка.

Взято из силиконпр0н.

Схема одного бита конфигурационной памяти из документации.

На рисунке ниже показана физическая структура ячеек памяти.

На фото слева показаны 8 ячеек памяти, одна из которых подсвечена.

Каждая горизонтальная линия данных подключена ко всем ячейкам памяти в строке.

Каждая строка выборки столбца выбирает все ячейки памяти в столбце, разрешая запись.

На средней фотографии показаны участки кремния и поликремния для одной ячейки памяти.

Слои металла были удалены, чтобы обнажить расположенные под ними транзисторы.

Слои металлизации соединяют транзисторы, на фото кружочки, это соединения-переходные отверстия между кремнием или поликремнием и металлом.

На схеме показано, как соединены пять транзисторов, расположение элементов на схеме соответствует их расположению на фотографии.

Две пары транзисторов образуют КМОП-инверторы, проходной транзистор слева внизу обеспечивает доступ к ячейке.

Восемь бит конфигурационной памяти: четыре сверху и четыре снизу.

Красный прямоугольник — это один бит. Когда активируется линия выборки столбца, строка данных строки загружает данные в соответствующую ячейку.

На увеличенной фотографии и схеме показан один бит конфигурационной памяти.

Взято отсюда: кремнийpr0n .

Мультиплексоры таблиц поиска

Как объяснялось ранее, FPGA реализует произвольные логические функции с использованием справочных таблиц.На рисунке ниже показано, как таблица поиска реализована в XC2064. Восемь значений слева хранятся в восьми ячейках памяти.

Четыре мультиплексора выбирают по одному из каждой пары значений в зависимости от значения на входе А, если А = 0, выбирается верхнее, если А = 1, то нижнее.

Затем большой мультиплексор выбирает одно из четырех значений на основе сигналов B и C. Результатом будет определенное значение, в данном случае A XOR B XOR C. Мы можем составить любую логическую функцию, если подставим разные значения в стол.

Реализация XOR в справочной таблице.

Каждый мультиплексор реализован с использованием проходных транзисторов.

В зависимости от сигналов управления активируется один из проходных транзисторов, передавая данные со входа на выход. На рисунке ниже показана часть схемы LUT с мультиплексированием двух битов.

Справа расположены две ячейки памяти.

Каждый бит проходит через инвертор, усиливается и проходит через проходные транзисторы мультиплексора посередине, выбирая один из этих битов.

Тип схем, реализующих ЛУТ.

Взято из силиконпр0н.

Курок

Каждый CLB содержит триггер, который позволяет FPGA реализовывать защелки, конечные автоматы и другие схемы с отслеживанием состояния.На рисунке ниже показана (несколько необычная) реализация триггера.

Она использует следующую схему.

Когда тактовый сигнал равен нулю, первый мультиплексор передает данные первой защелке, которая сохраняет значение.

Бит инвертируется дважды при прохождении через логические элементы ИЛИ, И-НЕ и инвертора и в конечном итоге остается прежним.

Затем мультиплексор второй защелки получает бит от первой защелки, когда тактовый сигнал возрастает до 1 (обратите внимание, что тактовый сигнал инвертируется).

Это значение является выходным сигналом триггера.

Когда тактовый сигнал установлен на 0, вторичный мультиплексор замыкает цикл, фиксируя бит. Таким образом, триггер чувствителен к фронту и фиксирует значение по нарастающему фронту тактового сигнала.

Линии установки и сброса устанавливают и сбрасывают триггер.

Реализация триггера.

Стрелки указывают на первый мультиплексор и два элемента ИЛИ-И-НЕ.

Фото кристалла взято отсюда: кремнийpr0n .

Восьмиконтактная матрица переключателей

Матрица коммутатора является важным элементом межсоединений.Каждый переключатель имеет 8 контактов (по два с каждой стороны) и может быть подключен практически любым способом.

Сигналы можно развертывать, разделять и пересекать с большей гибкостью, чем в отдельных узлах межсоединений.

На рисунке ниже показана часть сети межсоединений между четырьмя CLB (синий).

Матрицы переключателей (зеленые) можно подключать в любой комбинации соединений с правой стороны.

Обратите внимание, что каждый контакт может быть подключен к 5–7 другим контактам.

Например, контакт 1 можно подключить к контакту 3, но не к контактам 2 и 4. Это делает матрицу практически полной, с 20 возможными соединениями вместо 28.

Взято отсюда: Справочник по программируемой вентильной матрице Xilinx , рис.

7б.

Матрица переключения образована рядами проходных транзисторов, управляемых ячейками памяти выше и ниже них.

Две стороны транзистора представляют собой два вывода матрицы переключения, к которым может быть подключен транзистор.

Итак, каждая матрица имеет 20 управляющих битов, две матрицы на тайл дают нам 40 бит на тайл.

На фотографии ниже показана одна ячейка памяти, подключенная к волнистому затвору проходного транзистора под ней.

Этот транзистор обеспечивает соединение между контактом 5 и контактом 1. Таким образом, бит в потоке битов, соответствующий этой ячейке памяти, управляет соединением между контактами 5 и 1. Аналогично, другие ячейки памяти и связанные с ними транзисторы управляют другими соединениями.

Также обратите внимание, что порядок этих соединений не соответствует какому-либо определенному шаблону, в результате чего соответствие между битами в потоке битов и выводами переключателя выглядит случайным.

Матрица переключения Матрица переключения имеет 20 проходных транзисторов.

Поскольку каждая плитка имеет память шириной 18 ячеек, к дальнейшим ячейкам памяти подключено два транзистора.

Реализация 8-контактной матрицы подключения.

Области кремния обозначены номерами соответствующих контактов.

Металлические слои, соединяющие соответствующие выводы с транзисторами, удалены.

Взято из силиконпр0н.

Входные соединения

На входах CLB используется другая схема кодирования битового потока, что объясняется ее аппаратной реализацией.На рисунке ниже восемь эллиптических узлов являются потенциальными входами в CLB, называемый DD. В качестве входа можно настроить только один узел (максимум), поскольку подключение двух сигналов к одному и тому же входу может привести к их короткому замыканию.

Выбор входа.

Восемь входов, обведенных зеленым, являются потенциальными входами DD, из которых можно выбрать только один.

Требуемый вход выбирается мультиплексором.

Простым решением было бы использовать мультиплексор с 8 входами и тремя управляющими битами, выбирающими один из 8 сигналов.

Другим простым решением было бы использование 8-ми проходных транзисторов, каждый со своим собственным управляющим сигналом, один из которых выбирает нужный сигнал.

Однако ПЛИ Теги: #Электроника для начинающих #История ИТ #Анализ и проектирование систем #Старое оборудование #обратное проектирование #FPGA

-

Преимущества Удаленного Доступа

19 Oct, 24 -

Google Начала Переход На Новую Панель

19 Oct, 24 -

Smarty Обновлен До Версии 2.6.22.

19 Oct, 24 -

Элджей Открыл Ворота Джаберу

19 Oct, 24 -

Лайфстрим-Информер

19 Oct, 24 -

Рынок Антивирусов Привлекает Своей Динамикой

19 Oct, 24 -

Пикник С Инвесторами: Итоги

19 Oct, 24