На горизонте новые транзисторные структуры, новые инструменты и процессы – а вместе с ними масса проблем Несколько заводов пытаются вывести на рынок 5-нм техпроцесс, но их клиентам приходится решать, проектировать ли новые чипы с использованием нынешних транзисторов или переходить на новые, созданные по 3-нм техпроцессу.

Для перехода вам необходимо либо расширить существующие finFET на 3 нм, либо реализовать новую технологию кольцевого затвора [gate-all-around FET, GAA FET] на 3 нм или 2 нм.

GAA FET — это следующая эволюция finFET, они быстрее, но эти новые транзисторы более сложны и дороги в производстве, и переход на них может оказаться затруднительным.

С другой стороны, промышленность разрабатывает новые технологии травления, структурирования и т. д., чтобы расчистить путь для этих новых процессов.

Даты выпуска полевых транзисторов GAA варьируются от завода к заводу.

Samsung и TSMC производят finFET на 7 нм и планируют переделать finFET на 5 нм в этом году, а также производить чипы в полушаговом диапазоне от 5 нм.

Такие технические процессы позволят улучшить как скорость работы, так и энергопотребление.

Что касается 3 нм, то через год-два Samsung планирует перейти на нанолистовые полевые транзисторы — новый тип GAA-транзистора.

TSMC планирует впервые выпустить finFET на 3 нм техпроцессе.

Следующим шагом TSMC станет выпуск GAA по техпроцессу 3 или 2 нм — так считают многие аналитики и поставщики оборудования.

«TSMC ускоряет разработку 3-нм finFET, которые представляют собой сжатые версии 5-нм», — сказал Хэндел Джонс, директор IBS. – TSMC начнет производство первых прототипов 3-нм finFET в 2020 году.

Запуск производства запланирован на третий квартал 2021 года, что на четверть опережает запуск 3-нм процесса Samsung. Разработка GAA TSMC отстает от разработки Samsung на 12-18 месяцев, но агрессивная стратегия 3-нм finFET может восполнить этот пробел».

TSMC продолжает оценивать свои 3-нм варианты, и планы еще могут измениться.

Пока компания не прокомментировала ситуацию, но обещает вскоре раскрыть свои планы на 3 нм.

Однако переход TSMC на 3-нм finFET является логичным шагом.

Переход на новые транзисторы может негативно отразиться на потребителях.

Но в конечном итоге мощность finFET исчерпается, поэтому у TSMC не останется другого выбора, кроме как перейти на GAA. Другие компании также разрабатывают передовые процессы.

Intel, которая время от времени занимается коммерческим производством, производит чипы по 10-нм техпроцессу, одновременно изучая 7-нм процесс в лаборатории.

Тем временем SMIC производит finFET-транзисторы по нормам 16/12 нм и одновременно исследует в лаборатории технологию 10/7 нм.

Все передовые процессы требуют значительного финансирования, и не все чипы требуют 3-нм или других передовых технологий.

Рост цен вынуждает компании искать другие варианты развития.

Еще один способ воспользоваться преимуществами масштабирования — использовать новые типы корпусов для современных чипов.

Несколько компаний разрабатывают такие кейсы.

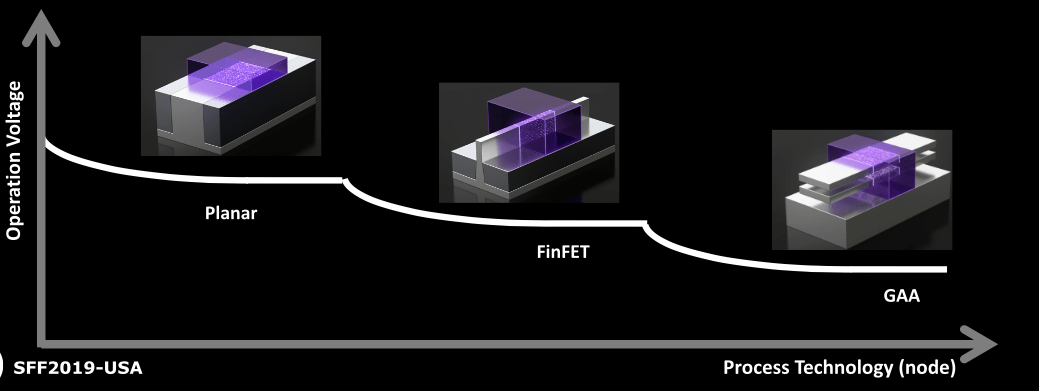

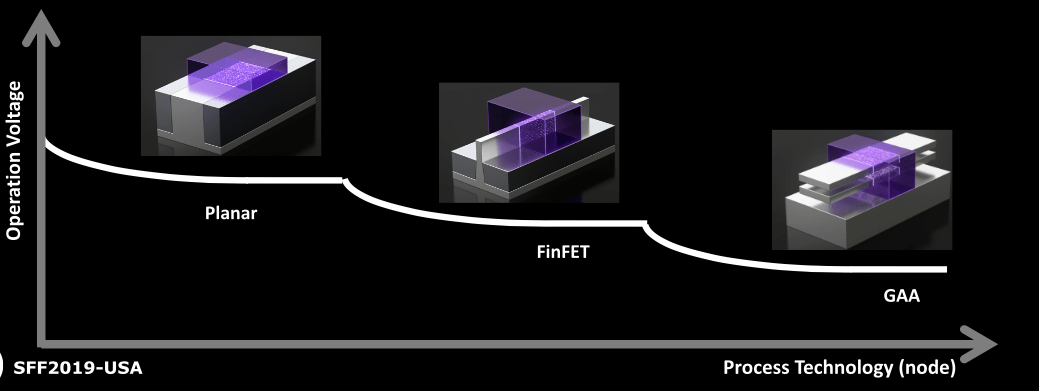

Рабочее напряжение различных технологий

Приближается ли конец масштабированию?

Микросхемы состоят из транзисторов, контактов и их соединений.Транзисторы действуют как переключатели.

Усовершенствованные чипы могут содержать до 35 миллиардов транзисторов.

Соединения наверху транзистора состоят из крошечных медных проводов, которые передают электрические сигналы между транзисторами.

Транзисторы и проводка соединены промежуточным слоем средней линии (MOL).

MOL состоит из крошечных контактов.

Масштабирование интегральных схем (ИС), традиционный способ их разработки, предполагает уменьшение размера ИС с каждым новым технологическим процессом и их упаковку на монолитном кристалле.

Для этого производители микросхем каждые 18-24 месяца внедряют новый технологический процесс, обеспечивающий постоянно растущую плотность упаковки транзисторов.

Каждому процессу присваивается числовое имя.

Первоначально эти названия были связаны с длиной транзисторного вентиля.

Для каждого последующего процесса производители масштабируют характеристики транзисторов с коэффициентом 0,7, что позволяет отрасли повысить производительность на 40 % при том же энергопотреблении и уменьшить размер на 50 %.

Масштабирование чипов позволяет выпускать новые, более функциональные электронные продукты.

Формула сработала, и производители чипов постепенно изменили свои техпроцессы.

Но на рубеже 20 нм произошла перемена — традиционные планарные транзисторы израсходовали весь свой ресурс.

С 2011 года производители перешли на finFET, что позволило масштабировать устройства дальше.

Однако производство finFET дороже.

В результате стоимость исследований и разработок резко возросла.

Поэтому сроки перехода от одного технического процесса к другому увеличились с 18 до 30 месяцев и более.

Intel следовала общей тенденции масштабирования 0,7x. Однако, начиная с 16 нм/14 нм, другие производители отошли от этой формулы, что вызвало некоторую путаницу.

С этого момента нумерация техпроцессов стала размываться и потеряла связь со характеристиками транзисторов.

Сегодня эти названия — всего лишь маркетинговые термины.

«Обозначение технических процессов становится менее осмысленным и понятным», — сказал Сэмюэл Вон, аналитик Gartner. – Например, при 5 нм или 3 нм не существует геометрического размера, равного 5 или 3 нм.

Кроме того, процессы у разных производителей становятся все более разными.

При одном и том же техпроцессе эффективность чипов у TSMC, Samsung и, конечно же, Intel различается.

Масштабирование передовых технологий также замедляется.

Согласно информации IC Knowledge и TEL, для 7-нм процесса шаг затвора транзистора [контактный полишаг, CPP] составляет 56-57 нм с шагом металла 40 нм.

Для 5-нм CPP составляет примерно 45-50 нм с шагом металла 26 нм.

CPP, ключевой показатель транзистора, обозначает расстояние между выводами истока и стока.

Кроме того, соотношение цена/качество уже не выглядит прежним, поэтому многие считают, что закон Мура уже устарел.

«Закон Мура на самом деле — это всего лишь наблюдение, которое стало самоисполняющимся пророчеством, которое поддерживает движение полупроводниковой промышленности вперед. «Экономика закона Мура начала ухудшаться из-за роста затрат на множественное моделирование и литографию в крайнем ультрафиолете (EUV)».

— сказал Дуглас Гереро, технический директор Brewer Science, — Новые архитектуры и конструкции обеспечат рост вычислительной мощности, но это уже не будет масштабирование.

Это означает, что будущие чипы будут увеличивать вычислительную мощность, но их стоимость не обязательно снизится.

та же ставка, что и раньше».

Масштабирование не прекращается полностью.

Искусственный интеллект, серверы и смартфоны требуют все более быстрых чипов и передовых технических процессов.

«Десять лет назад некоторые люди спрашивали: кому нужно больше транзисторов? Некоторые считали, что в мире заканчиваются идеи о том, что делать с более быстрыми компьютерами, за исключением очень экзотических приложений, сказал Аки Фудзимура, директор D2S. – Сегодня для Интернета вещей более низкая стоимость, достаточно хорошая производительность и возможности интеграции превосходят простое увеличение плотности.

Однако для производства более быстрых и экономичных чипов необходимы более быстрые транзисторы, где стоимость транзисторов снизится».

Очевидно, что не все требует передовых технических процессов.

Существует высокий спрос на чипы, производимые с использованием отработанных технологических процессов.

«Сюда входят микросхемы радиоволновых и OLED-дисплеев в смартфонах, а также микросхемы управления питанием, используемые в компьютерах и твердотельных накопителях», — сказал Джейсон Вон, сопрезидент UMC.

масштабирование finFET

Когда дело доходит до масштабирования чипов, производители уже много лет следуют одной и той же схеме с идентичными типами транзисторов.В 2011 году Intel перешла на 22-нм finFET, а затем на 16/14 нм.

В finFET контроль тока достигается путем размещения вентилей на всех трех сторонах плавника.

finFET имеют от 2 до 4 ребер.

Каждый из них имеет свою определенную ширину, высоту и форму.

22-нм finFET Intel первого поколения имел шаг ребер 60 нм и высоту 34 нм.

Затем при 14 нм шаг и высота были одинаковыми — 42 нм.

Intel сделала плавники выше и тоньше, чтобы масштабировать finFET. «Масштабирование finFET уменьшает боковые размеры устройства, увеличивает плотность площади и увеличивает высоту плавников, что повышает производительность», — написала в своем блоге Нерисса Дрегер, директор по связям с университетами компании Lam Research. При использовании техпроцесса 10/7 нм производители микросхем пошли по тому же пути масштабирования finFET. В 2018 году TSMC начала производство первых 7-нм finFET, а затем Samsung. Intel начала производство по 10-нм техпроцессу в прошлом году после нескольких задержек.

В 2020 году конкуренция на заводах усилится.

Samsung и TSMC готовят 5-нм и различные полуинтегральные техпроцессы.

Исследования в отношении 3 нм продолжаются.

Все процессы дорогие.

Стоимость разработки 3-нм чипа составляет 650 миллионов долларов США — сравните это с 436,3 миллионами долларов США для устройства 5-нм и 222,3 миллионами долларов США для устройства 7-нм.

Это стоимость такой разработки, после которой через год технология поступит в производство.

По сравнению с 7-нм 5-нм finFET от Samsung обеспечат увеличение логической области на 25%, снижение энергопотребления на 20% или увеличение скорости на 10%.

Для сравнения, 5-мм finFET TSMC предлагает «на 15% большую скорость при том же энергопотреблении или на 30% меньше энергопотребления при той же скорости, с увеличением логической плотности в 1,84 раза», — сказал Джеффри Йеп, директор по передовым технологиям TSMC. .

Производители чипов внесли серьезные изменения в техпроцесс 7 и 5 нм.

Для изготовления критически важных элементов чипов обе компании перешли от традиционной 193-нм литографии к литографии в крайнем ультрафиолете (EUV).

EUV использует длину волны 13,5 нм, что упрощает процесс.

Но EUV не решает всех проблем масштабирования чипов.

«Решение этих проблем требует множества технологий, выходящих за рамки масштаба, включая использование новых материалов, новых типов встроенной энергонезависимой памяти и передовых логических архитектур, новых подходов к травлению, инноваций в производстве корпусов и конструкции чиплетов», — сказала Регина Фрид, управляющий директор по технологиям Applied Materials. Тем временем, Samsung и TSMC за кулисами готовят варианты 3-нм техпроцесса.

В прошлом производители микросхем шли по одному и тому же пути, но сегодня их пути расходятся.

«3 нм выпускаются в разных вариантах, таких как finFET и GAA», — сказал Вон.

«Это позволяет клиентам выбирать различные комбинации стоимости, плотности, энергопотребления и скорости в соответствии со своими потребностями».

Samsung обещает представить 3-нм нанолистовой полевой транзистор.

TSMC также работает над ними, но планирует распространить использование finFET на следующее поколение.

«У TSMC будет 3-нм finFET в третьем квартале 2021 года», — сказал Джонс.

«TSMC GAA будет доступен в 2022-2023 годах».

Именно здесь клиенты завода должны взвесить все «за» и «против» в отношении затрат и технических компромиссов.

Расширение finFET — безопасный путь.

«Многие клиенты считают TSMC наименее рискованным производителем», — сказал Джонс.

Тем не менее, GAA обеспечивает некоторое улучшение производительности.

«GAA имеет более низкое пороговое напряжение на 3 нм и потенциально на 15-20% меньшее энергопотребление по сравнению с 3-нм finFET», — сказал Джонс.

«Однако разница в производительности будет на уровне 8%, поскольку MOL и BEOL — одно и то же».

Серверная часть линии (BEOL) и MOL являются узкими местами в производстве современных чипов.

Проблема с MOL заключается в контактном сопротивлении.

BEOL — это этап производства, на котором подключается проводка.

Из-за их постепенного уменьшения возникают задержки из-за емкости.

В finFET и GAA используются разные транзисторы, но схемы их соединений в 3-нм техпроцессе, вероятно, будут почти идентичными.

Задержки, связанные с емкостью, нанесут вред обоим типам транзисторов.

Есть и другие проблемы.

finFET достигнут своего предела, когда ширина плавника достигнет 5 нм.

finFET на техпроцессе 5 нм/3 нм уже достигают этого предела.

Кроме того, 3-нм finFET могут состоять из одного ребра по сравнению с двумя или более ребрами в других процессах.

«Чтобы расширить производительность finFET за пределы 3-нм, нам потребуются специальные технологии, которые увеличат мощность одного ребра и уменьшат паразитные помехи», — сказал Наото Хоригучи, директор CMOS в Imec. Один из способов расширить производительность finFET за пределы 3-нм техпроцесса — перейти на германий для p-канала.

3-нм finFET с каналами с высокой пропускной способностью помогут увеличить скорость чипов, но столкнутся с определенными проблемами интеграции.

Переход на нанолисты

В конце концов, finFET перестанут масштабироваться, и производителям микросхем придется перейти на новые транзисторы, а именно нанолистовые полевые транзисторы.Нанолистовые полевые транзисторы начали набирать обороты в 2017 году, когда Samsung представила 3-нм многомостовой полевой транзистор (MBCFET).

MBCFET — это нанолистовые полевые транзисторы.

Тестовые образцы начнут выпускать в этом году, а промышленное производство начнется в 2022 году.

TSMC также работает с нанолистовыми полевыми транзисторами, которые представляют собой разновидность транзистора GAA. Нанолистовые полевые транзисторы мало что дают при масштабировании finFET до 5 нм, но у них есть несколько преимуществ.

Полевой транзистор нанолиста, по сути, представляет собой плавник-транзистор, положенный набок и окруженный затворами.

Нанолист состоит из нескольких отдельных тонких горизонтальных листов, уложенных друг на друга.

Каждый лист представляет собой отдельный канал.

Вокруг каждого листа имеется затвор, в результате чего получается кольцевой транзистор.

Теоретически полевые транзисторы с нанолистами обеспечивают более высокую производительность при меньшей утечке, поскольку ток контролируется с четырех сторон структуры.

Первоначально нанолистовые полевые транзисторы будут состоять примерно из четырех листов каждый.

«Ширина типичного нанолиста составляет от 12 до 16 нм, а толщина — 5 нм», — сказал Хоригучи.

Вот чем нанолист отличается от finFET. Количество ребер на finFET ограничено, что сковывает работу конструкторов.

«Преимущество нанолиста в том, что его ширину можно менять.

Ширину можно выбрать по желанию дизайнера.

Это дает им некоторую свободу.

Они смогут найти лучший вариант с точки зрения энергопотребления и скорости», — сказал Хоригучи.

Например, транзистор с более широким листом будет иметь больший ток возбуждения.

Узкий лист позволяет использовать устройство меньшего размера с меньшим током возбуждения.

Нанолисты связаны с технологией нанопроволок, в которой провода служат каналами.

Ограничение ширины канала приводит к ограничению тока возбуждения.

Вот почему нанолистовые полевые транзисторы набирают обороты.

Однако эта технология и 3-нм finFET имеют несколько проблем.

«Проблемы finFET связаны с квантовым контролем ширины и профиля плавников.

Проблемы нанолистов связаны с дисбалансом p/n, эффективностью нижнего листа, прослойками между листами, контролем длины клапана», — сказал Джин Кай, заместитель директора TSMC, во время презентации на IEDM. Учитывая все эти сложности, внедрение технологии нанолистовых полевых транзисторов займет некоторое время.

«Существует множество препятствий на пути перехода к новой транзисторной архитектуре», — сказал Герреро.

«Это определенно потребует новых материалов».

В простейшем варианте процесса изготовление нанолистового полевого транзистора начинается с формирования сверхрешетки на подложке.

Питаксиальный инструмент наносит на подложку чередующиеся слои кремний-германиевого сплава (SiGe) и кремния.

Пакет будет состоять как минимум из трех слоев SiGe и трех слоев кремния.

Затем в сверхрешетке с помощью структурирования и травления формируются вертикальные ребра, что требует очень точного контроля процесса.

Дальше начинается один из самых сложных этапов – формирование внутренних прокладок.

Во-первых, внешние части слоев SiGe утоплены заподлицо в сверхрешетку.

При этом создаются небольшие углубления, заполненные диэлектриком.

«Внутренние прокладки необходимы для уменьшения пропускной способности клапана», — сказал Кай.

«Их создание — важнейшая часть процесса».

И такие технологии уже существуют — IBM и TEL недавно описали новую технику травления, подходящую как для внутренних прокладок, так и для выпусков каналов.

Для этого используется изотропное сухое травление SiGe в соотношении 150:1. Эта технология позволяет создавать очень точные внутренние прокладки.

«Для создания углублений в SiGe требуется очень избирательное боковое «слепое» травление слоев», — сказал Николас Лубе, менеджер по исследованиям и разработкам в IBM. Затем формируются исток и сток.

После этого слои SiGe удаляются из сверхрешетки с помощью травления.

Остаются кремниевые слои или листы, составляющие каналы.

Структура содержит Хай-к -материалы и, наконец, образуются соединения MOL, образующие нанолист. Это упрощенное описание этого сложного процесса.

Однако, как и любая новая технология, нанолисты могут иметь дефекты.

Требуется дополнительное изучение и измерение всех этапов.

«Как и в случае с предыдущими технологическими переходами, мы видим проблемы, связанные с изучением и измерением нанолистов», — сказал Чет Ленокс, директор по решениям для управления процессами в KLA. «Многие дефектные моды могут появляться как во внутренних прокладках, так и в нанолистах.

Производителям микросхем нужны точные размеры отдельных нанолистов, а не просто средний размер каждой стопки, чтобы уменьшить изменчивость в своих производственных процессах».

Это также требует новых технологий.

Например, компании Imec и Applied Materials недавно представили работу по технологии сканирующей микроскопии сопротивления распространению скальпеля (s-SSRM) для создания кольцевых ворот. В технологии s-SSRM крошечный скальпель отламывает небольшую часть структуры, и в этот срез можно добавить легирующие примеси.

Другие варианты

В рамках научно-исследовательских усилий Imec разрабатывает более совершенные GAA, такие как CFET и полевые транзисторы с вилочными листами, ориентированные на 2 нм и ниже.К тому времени масштабирование микросхем станет слишком дорогим для большинства производителей, особенно если преимущества в мощности и производительности уменьшатся.

Поэтому усовершенствованные конструкции микросхем становятся все более популярными.

Вместо того, чтобы впихивать все функции в один чип, идея состоит в том, чтобы разбить устройства на более мелкие чипы и интегрировать их в передовые корпуса.

«Все зависит от приложения», — сказал Рич Райс, старший вице-президент по развитию бизнеса ASE. «Мы определенно наблюдаем рост таких попыток, даже в технологических процессах, уходящих глубоко в субмикронные размеры.

Это развитие будет продолжаться и дальше.

Многие компании делают это.

Они решают, смогут ли они интегрировать чипы по 5-нм техпроцессу и хотят ли они этого.

Они активно ищут способы взлома систем».

Это не так-то просто сделать.

Плюс есть несколько вариантов корпуса с разными компромиссами — 2.5D, 3D-ИС, чиплеты и разветвление.

Заключение

Конечно, не всем понадобятся такие передовые технологии.Однако Apple, HiSilicon, Intel, Samsung и Qualcomm не зря делают ставку на передовые технологии.

Потребителям нужны новейшие, лучшие и более быстрые системы.

Единственный вопрос заключается в том, принесут ли новые технологии какие-либо реальные выгоды по доступной цене.

Теги: #Производство и разработка электроники #3 нм #5 нм #Закон Мура #FinFET #технический процесс #нанолисты #гаа фет

-

Bluetooth-Клавиатура Ipad: Большой Выбор

19 Oct, 24 -

Согласны Ли Мы На Некачественный Код?

19 Oct, 24 -

Защита Почты

19 Oct, 24