Продолжаем рассматривать многоядерное DSP-устройство TMS320C6678. Данная статья посвящена проектированию рабочих ядер процессора.

Базовая архитектура описана кратко с акцентом на сравнение платформы C66x с более ранними, хорошо известными моделями C6000. Операционное ядро процессора сигналов — это основной элемент, непосредственно реализующий вычислительные действия, направленные на обработку сигнала в соответствии с алгоритмом, продиктованным программой, встроенной в процессор.

Многоядерные процессоры семейства TMS320C66xx содержат набор рабочих ядер, что является необходимым условием соответствующего увеличения вычислительной производительности устройства по сравнению с одноядерными процессорами.

Далее мы рассмотрим одно типичное ядро DSP процессора TMS320C66xx. Процессоры TMS320C66x являются развитием платформы сигнального процессора Texas Instruments C6000. Основы архитектуры остались прежними, однако их возможности и, частично, интерпретация их функционирования претерпели некоторые изменения.

Ядро процессора TMS320C66xx построено на архитектуре с очень длинным командным словом (Very Long Instruction Word — VLIW — «Vi-Эl-I-Double-U»).

Каждое ядро включает в себя 8 параллельных вычислительных блоков (2 умножителя и 6 АЛУ) и регистровый файл из 64 32-битных регистров.

По сравнению с последними моделями процессоров линейки TMS320C6000 процессоры TMS320C66xx обладают следующими особенностями.

- Количество операций умножения и накопления, выполняемых за такт, увеличено в 4 раза как для фиксированной, так и для плавающей точки.

Каждое ядро способно выполнять 32 операции умножения с фиксированной запятой размером 16x16 бит или 8 операций умножения с плавающей запятой размером 32x32 бита за один такт.

- Повышена эффективность арифметики с плавающей запятой: реализована поддержка быстрого выполнения основных операций с плавающей запятой; вычисления с плавающей запятой в режиме SIMD (параллельные операции над частями слов данных); комплексное умножение в формате с плавающей запятой; другие расширения функционала.

- Возможности векторной арифметики были расширены как в форматах с фиксированной, так и с плавающей запятой.

Векторная арифметика относится к следующей концепции.

Операнды на входе арифметических блоков представлены 128-битными векторами, состоящими из 4-х 32-битных векторов; 8 16-битных или 16 8-битных слов данных.

Арифметические операции могут выполняться одновременно со всеми операндами в векторах (режим SIMD).

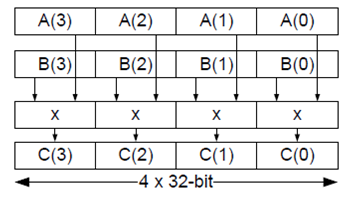

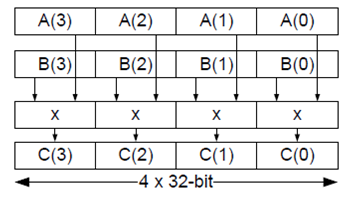

Пример векторного умножения с помощью команды QMPY32 показан на рисунке 1.

Рисунок 1 – Пример векторного умножения - Появились дополнительные специальные наборы инструкций для комплексной и матричной арифметики.

Этот функционал аналогичен векторному умножению, однако вместо режима SIMD используются более сложные схемы, позволяющие реализовать, в частности, до двух комплексных умножений вектора размерности (1х2) и матрицы размерности.

(2x2) за один такт. Также поддерживаются дополнительные операции, такие как, например, получение комплексно-сопряженного числа.

За счет этого производительность вычислений увеличивается более чем в 30 раз (если сравнивать процессор TMS320C6455 с тактовой частотой 1,2 ГГц и производительностью 9600 MMACS и процессор TMS320C6678 с частотой 1,25 ГГц и производительностью 320 GMACS).

Основные вычислительные возможности процессоров TMS320C66x в сравнении с процессорами предыдущего семейства TMS320C674x с плавающей запятой сведены в таблицу 1.1. Обратите внимание, что производительность, выраженная в количестве MAC в секунду, не полностью отражает вычислительную мощность процессора.

Векторная арифметика накладывает ряд ограничений на операнды.

Один умножитель, выполняющий 16 умножений за такт, — это не то же самое, что 16 умножителей, выполняющих, казалось бы, одни и те же 16 умножений за такт. Не все задачи можно решить с помощью векторной арифметики.

В таких случаях ресурсы процессора могут простаивать и выигрыш в архитектуре не будет ощущаться.

| C674x | C66x | |

|---|---|---|

| Количество операций умножения-накопления за такт в формате с фиксированной запятой 16x16 бит. | 8 | 32 |

| Количество операций умножения-накопления за такт в формате 32x32-бит с фиксированной запятой | 2 | 8 |

| Количество операций умножения-накопления за такт в формате с плавающей запятой обычной точности | 2 | 8 |

| Количество распространенных операций с плавающей запятой за цикл | 6 | 16 |

| Пропускная способность канала чтения/записи между ядром и памятью | 2x64 бита | 2x64 бита |

| Размерность векторных операндов (Возможности обработки SIMD) | 32 бита (2x16 бит, 4x8 бит) | 128 бит (4x32 бита, 4x16 бит, 4x8 бит) |

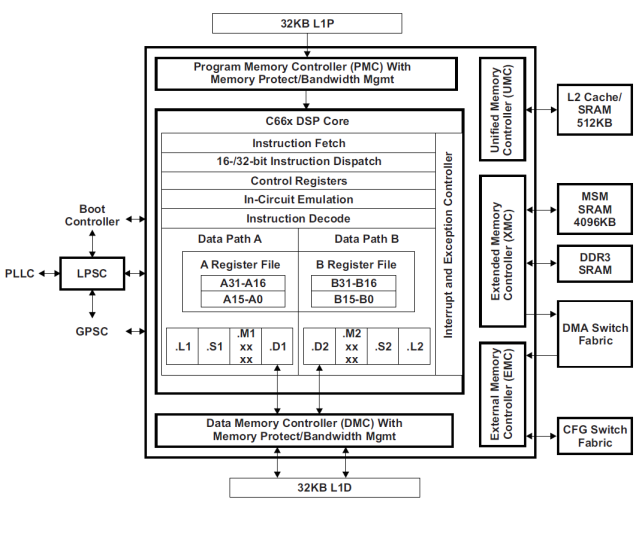

Процессоры TMS320C66x содержат двойной набор вычислительных блоков — один на стороне A (Путь данных A); другой находится на стороне B (путь данных B).

Набор вычислительных блоков классический и включает в себя умножитель .

М, АЛУ .

L, сдвигатель .

S и генератор адреса данных .

D. В современных ЦСП функции каждого из этих блоков существенно расширены и могут частично перекрываться; однако для упрощения понимания удобно пользоваться классической терминологией.

Все блоки работают параллельно, извлекая операнды из регистров файла регистров (A/B Register File) и возвращая результат соответствующей операции в один из регистров.

Данные перед поступлением в регистровый файл для обработки сохраняются во внутренней или внешней памяти данных (L1D, L2 Cache/SRAM, MSM SRAM, DDR3 SRAM).

Результаты обработки и массивы промежуточных данных также записываются в память.

Подсистема памяти процессора TMS320C66x будет рассмотрена отдельно в соответствующем разделе.

Данные обрабатываются в соответствии с программой, загруженной в процессор.

Во время работы программа находится в программной памяти (L1P, L2 Cache/SRAM, MSM SRAM, DDR3 SRAM).

Программная машина отвечает за чтение программы из памяти (Instruction Fetch), ее декодирование (Decode) и распределение по соответствующим исполнительным элементам (Dispatch).

Рисунок 2 — Архитектура ядра процессора C66x

Дополнительные аппаратные модули в составе ядра процессора представляют собой набор регистров управления (Control Registers), логику внутрисхемной эмуляции (In-Circuit Emulation), контроллер прерываний и исключений (Interrupt and Exception Controller), диспетчер памяти, включающий в себя модуль защиты памяти (контроллер памяти программ/данных) и ряд других компонентов.

Далее рассмотрим подробнее вычислительные блоки и регистры рабочего ядра.

В данном случае мы остановимся лишь на отличиях ядра C66x от ядер предыдущих моделей процессоров.

В процессорах C66x используется принцип упакованных инструкций — наиболее часто используемые инструкции имеют длину 16 бит, а базовая длина командного слова — 32 бита.

Это экономит память программы.

Программная машина процессора способна одновременно извлекать, декодировать и выдавать из памяти до 15 команд. Регистровые файлы сторон A и B содержат по 32 32-битных регистра.

Обеспечивает возможность работы с 8-, 16-, 32-, 64- и 128-битными данными (для формата с фиксированной запятой), а также с 40-битными данными.

В этом случае регистры группируются в пары или четверки.

Шины обмена между регистровым файлом и вычислительными блоками расширены до 64 бит. В блоки .

L и .

S можно одновременно подать два 64-битных операнда и получить 64-битный результат. В умножитель подаются два 128-битных операнда, сформированных как два 64-битных входных слова.

Результат 128-битный.

По каналам пересечения сторон A и B можно передавать только 64-битные слова.

Возможность загрузки операндов из памяти в регистры не изменилась — четыре 32-битных слова за такт. Возможности записи в память были расширены до четырех 32-битных слов за такт по сравнению с процессорами TMS320C67x. Команды всегда выбираются из памяти по 8 слов каждая, образуя пакет выборки.

Однако реально такой пакет может содержать до 14 инструкций благодаря наличию 16-битных инструкций, упакованных в одно слово.

Если пакет содержит только обычные 32-битные инструкции, то каждый 0-й бит инструкции указывает, выполняется ли эта инструкция параллельно со следующей или следующая инструкция выполняется на один такт позже.

То есть наличие бита параллельности позволяет указать, какие инструкции выполняются параллельно.

В результате формируются пакеты исполнения, которые могут содержать от 1 до 8 и 32-битных команд. Если пакет выборки включает в себя упакованные инструкции, то такой пакет сопровождается заголовком, занимающим 2 старших слова.

Заголовок указывает, что содержится в пакете, какие из команд 16-битные и какие из команд выполняются параллельно.

Адресация осуществляется аналогично предыдущим моделям процессоров.

Однако интересно отметить, что циклическая адресация позволяет перебирать невыровненные адреса.

Работа конвейера при обработке команд в целом не отличается от общего подхода к организации выполнения программы для платформы C6000. Конвейер включает в себя 4 этапа выборки команд, 2 этапа декодирования и от 1 до 10 этапов выполнения инструкций.

Разные команды выполняются за разное количество циклов.

Команды, выполняемые за один этап выполнения, называются однотактными.

Однотактные инструкции включают большинство операций с фиксированной точкой.

Инструкции с плавающей запятой, даже базовые операции умножения и сложения, представляют собой 4-тактные инструкции.

Команды доступа к памяти, команды перехода и многие другие не являются однотактными.

Различия во времени выполнения разных инструкций вызывают разные ограничения на совместное использование инструкций и ресурсов процессора.

Все это делает процесс программирования процессора, особенно на низком уровне, достаточно сложной задачей.

Однако эта концепция, как уже говорилось, лежит в основе всей платформы C6000. Обработка прерываний организована аналогично другим моделям процессоров C6000. Типы прерываний: перезапуск, немаскируемое прерывание, маскируемое прерывание и исключение.

Специальный регистр определяет адрес таблицы векторов прерываний.

Таблица содержит набор кодов для каждого прерывания.

Если обработка прерываний проста, весь соответствующий код можно записать непосредственно в саму таблицу.

Если код не подходит, необходимо организовать переход к процедуре обработки прерываний.

Обычно реакция на прерывание отключает другие маскируемые прерывания.

Однако обработку вложенных прерываний можно организовать искусственно с помощью специальных фрагментов кода, описанных в документации.

Все статьи серии:

- Обзор архитектуры процессора

- Операционные ядра: вычислительные ресурсы ЦП

-

Все О Sony Vaio Vpc-F Серии 13Wfx/B

19 Oct, 24 -

Голосовое Меню Своими Руками

19 Oct, 24 -

Против Учителей, Которые Читают С Бумаги

19 Oct, 24 -

Видеоуроки По Python От Академии Хана

19 Oct, 24 -

Поздравляем Дорогих Дам

19 Oct, 24 -

Легальность Музыкальных Сервисов

19 Oct, 24