Логисторная логика — это набор концепций, применение которых позволяет ускорить вычисления, снизить затраты вычислительной энергии и увеличить плотность транзисторов на кристалле без существенного изменения техпроцесса.

Он находится в стадии разработки, и приведенная ниже статья является лишь основным результатом.

Мы надеемся, что она вызовет интерес в научных кругах и среди энтузиастов и развитие продолжится.

Логисторная логика предполагает:

- Параллельное – последовательное, а не последовательное, как в КМОП, выполнение операций на уровне логических элементов (альтернатива КМОП).

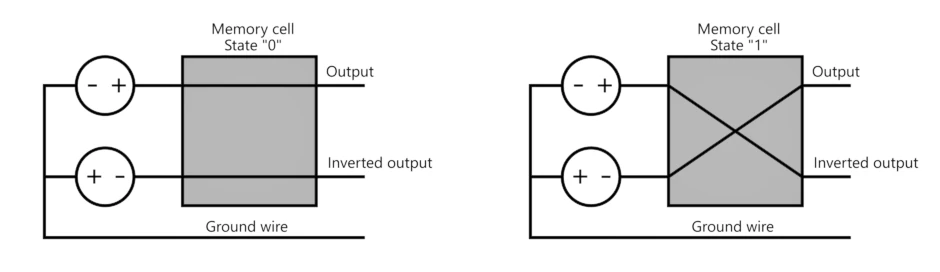

- Нестандартный метод кодирования 0 и 1

- Использование логисторов (типа транзисторов)

- Использование биполярной силы

- Использование «сеточного массива» макетов ворот (вертикальных и горизонтальных при виде сверху)

Время выполнения этих операций определяется суммой времен выполнения каждой из последовательно включенных транзисторных КМОП-сборок.

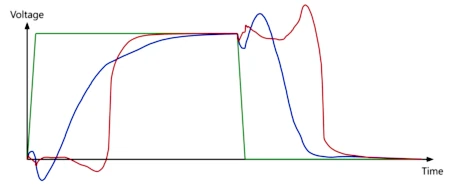

Для демонстрации задержек, возникающих при последовательном соединении КМОП-сборок, представим моделирование, выполненное в LTSpice на основе реальных spice-моделей 10-нм FinFET:

На графике ниже показаны исходный сигнал (зеленый) и задержки, возникающие после двух (синий) и после четырех инверторов (красный).

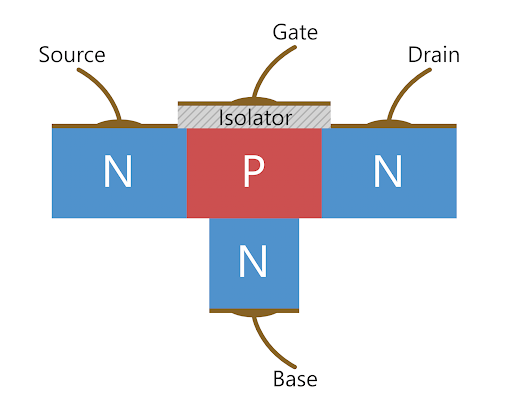

Предлагается новый тип транзистора – лог:

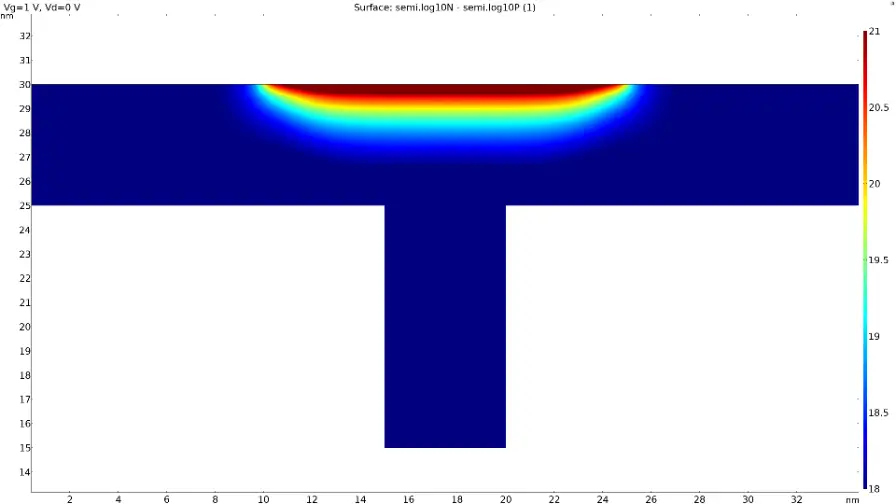

В логисте выходной сигнал (между Source и Drain) «изолирован» от управляющего сигнала — между Gate и Base; соответственно логисты тоже можно использовать вместо оптопар Логистическое моделирование было выполнено в полупроводнике Comsol, которое показало появление канала между истоком и стоком, когда положительное напряжение прикладывается к затвору, а отрицательное - к базе.

Ниже показан канал при отсутствии и наличии напряжения между источником и стоком:

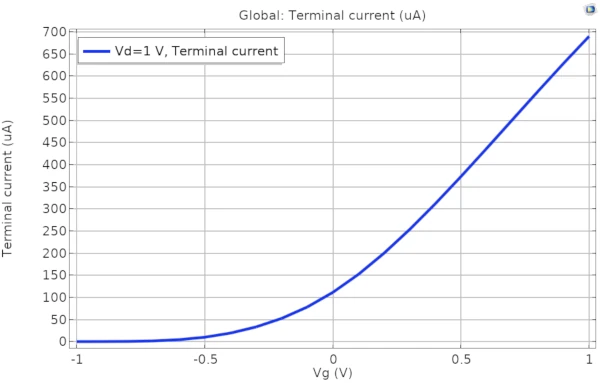

Расчетная Вольт-Амперная характеристика логиста:

Благодаря биполярному питанию, о котором будет сказано ниже, нет необходимости обеспечивать полную «запирание» логиста при коротком замыкании Gate и Base, что дает возможность выбрать профиль допинга, при котором логист « «лучше» заблокирован и позволяет пропускать в три раза более высокие токи, чем NMOS, при прочих равных условиях.

Входные значения в АЛУ, построенном на основе логической логики, должны иметь следующий способ кодирования 0 и 1:

Где выходное значение — это напряжение между выходами и землей.

Как видите, каждый бит передается по двум проводам.

Единичные логические операции в логистической логике в основном описываются следующим образом:

Где «результат» — это наличие (1) или отсутствие (0) пути.

В логической логике логические схемы отличаются от КМОП, ТТЛ и других технологий.

Если нет ограничения на степень параллелизма (в «полной» логистической логике), схемы строятся таким образом, что при выполнении операции не происходят операции «to Gate».

Другими словами, АЛУ запрещено отправлять сигнал от стока к затвору.

В результате операции выполняются параллельно, а не последовательно, как в CMOS.

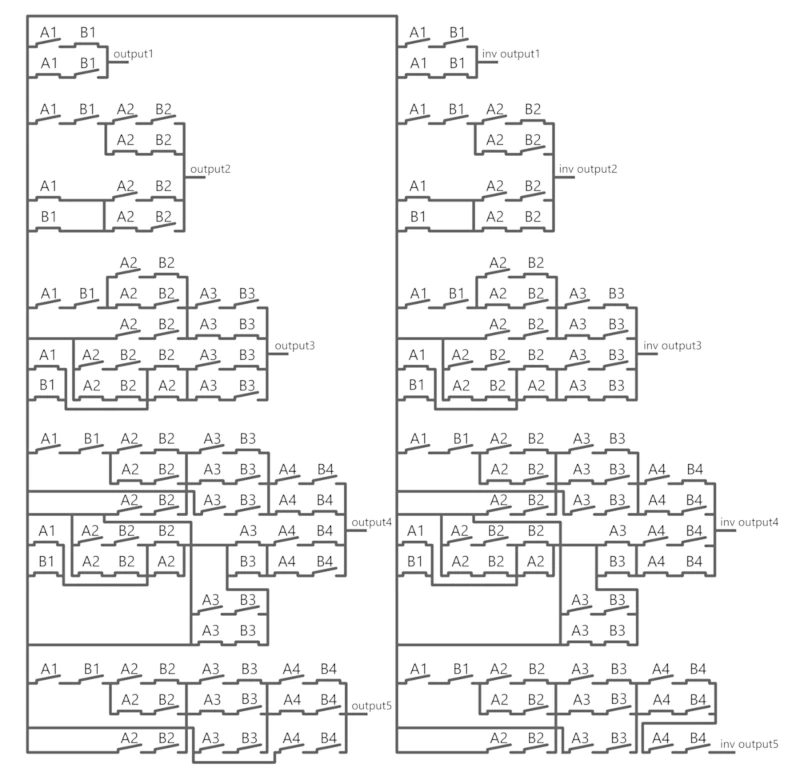

Пример построения «полной» логистической схемы сумматора двух 4-битных чисел А1, А2, А3, А4; B1, B2, B3, B4 – биты первого и второго числа; выходы - результат Инвертированные входы представлены как проводящие переключатели, неинвертированные входы представлены как непроводящие переключатели.

В логистической логике формат вывода не регламентирован и может не совпадать с форматом ввода, поэтому правая часть (дополнительная) является необязательной и дается для понимания способа построения дополнительных цепей.

В полной логической логике каждый выход должен иметь независимую логическую схему.

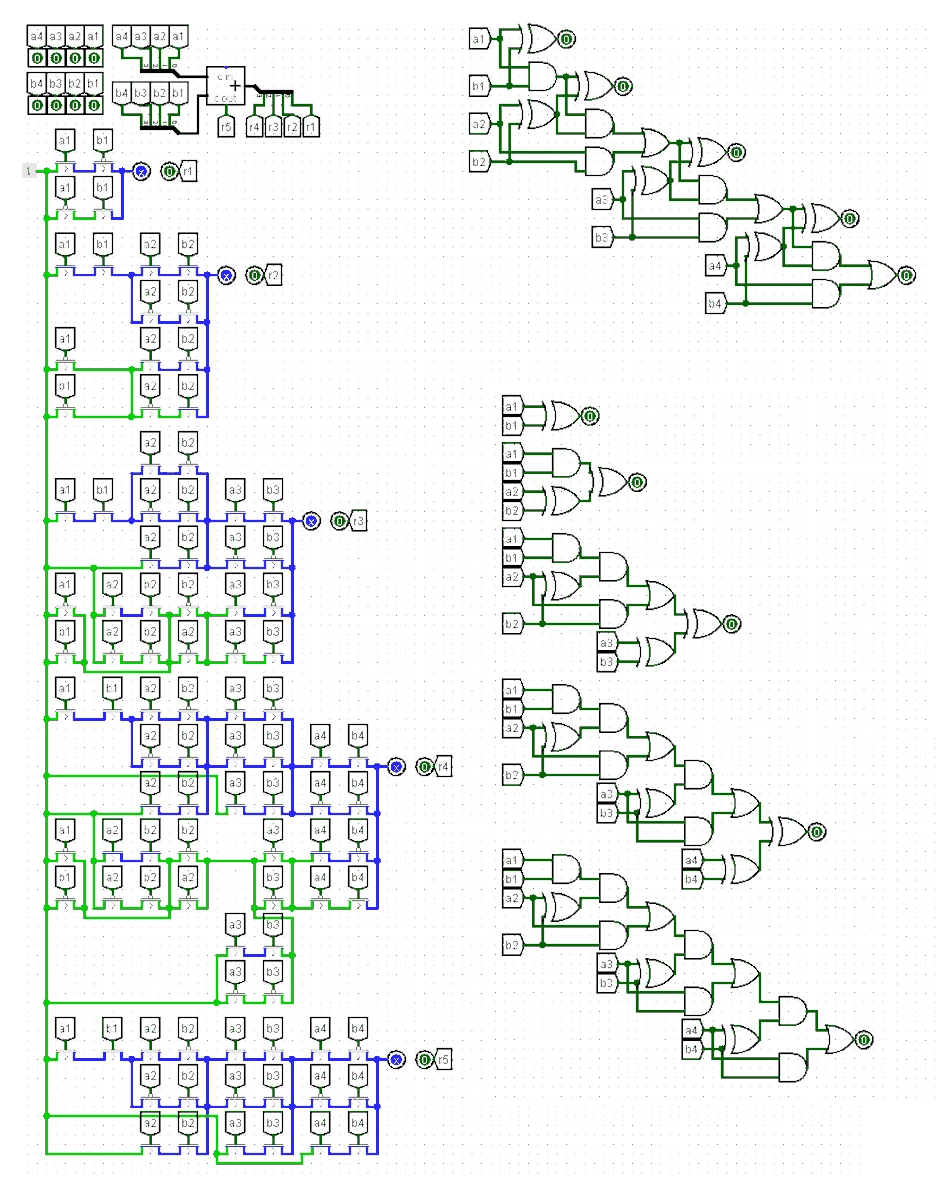

Ниже представлена симуляция Logisim без дополнительной части.

вверху справа — стандартная схема сумматора; Внизу справа — схема, необходимая для построения полных логистических цепей.

Ниже приведена симуляция логистического сумматора двух 3-битных чисел в фальстаде:

Для подтверждения работоспособности логической части логистической логики была спроектирована плата в EasyEDA и изготовлена на JLCPcb:

Поскольку логистов не существует, были использованы оптопары.

Плата работает и выдает ожидаемые значения, что неопровержимо доказывает правильность логической части логистической логики.

Для достижения высокой плотности логов рекомендуется объединить Базу всех логов и разместить Базу на обратной стороне Подложки.

Ворота рекомендуется располагать горизонтально и вертикально.

Исток и Сток соседних Логисторов должны быть объединены, чтобы 4 Гейта были подключены к одному Истоку/Стоку.

Стоит обратить особое внимание на то, что в статье описана логистическая логика без ограничения степени параллелизма (полного), где степень параллелизма — это примерное количество Гейтов, которые можно запитать от одного Драйна.

Для повышения производительности обязательно использовать ограничение степени параллелизма.

Это устраняет необходимость использования независимой схемы для каждого выходного бита.

Использование каскадирования перед логистической логикой для увеличения токов и насыщения большого количества вентилей является очевидным, но худшим решением.

По техническим причинам команда не может продолжить работу над проектом и описать оптимальное решение по реализации ограничения на степень параллелизма, а также не имеет ресурсов для реализации чипа на основе логистической логики, поэтому материал передается на дальнейшее рассмотрение.

разработки для научного сообщества и энтузиастов Разработано ЛНМО; Авторы: Артём Родичкин, Анна Евсеева, Полина Маслова, Семен Архипов, Инна Миронова, Михаил Чечулин Теги: #Популярная наука #Процессоры #Будущее уже здесь #Высокая производительность #процессор #физика #логика #технический процесс #cmos

-

Принципы Мониторинга Бизнес-Приложений

19 Oct, 24 -

Грейс «Бабушка Кобола» Хоппер

19 Oct, 24 -

Ground Zero Свяжет Ваш Адрес И Ядерный Взрыв

19 Oct, 24 -

Youtube Присваивает Пользовательский Контент

19 Oct, 24