Господа! Недавно Imagination Technologies (компания, разработавшая графический процессор PowerVR внутри Apple iPhone) и Xilinx (компания № 1 в области FPGA) начали постепенно пропагандировать несколько иконоборческую инициативу по бесплатному распространению среди университетов исходного кода современных промышленных Ядро процессора MIPS microAptiv UP. который используется, например, в микроконтроллере Microchip PIC32MZ. Студенты смогут изменять команды этого процессора, добавлять к нему свои периферийные устройства и реализовывать полученную конструкцию на ПЛИС.

Вот ссылка на сообщение о семинаре 13-14 мая под Лос-Анджелесом, на котором Imagination и Xilinx покажут представителям научных кругов новый продукт под названием MIPSfpga — imgtec.com/mipsfpga По сути, MIPSfpga — это бесплатная лицензия на базовую конфигурацию экономичного процессорного ядра MIPS microAptiv UP, которая предоставляется в исходном коде на языке описания аппаратного обеспечения Verilog. Это то же самое ядро, которое продается коммерческим заказчикам за сотни тысяч долларов.

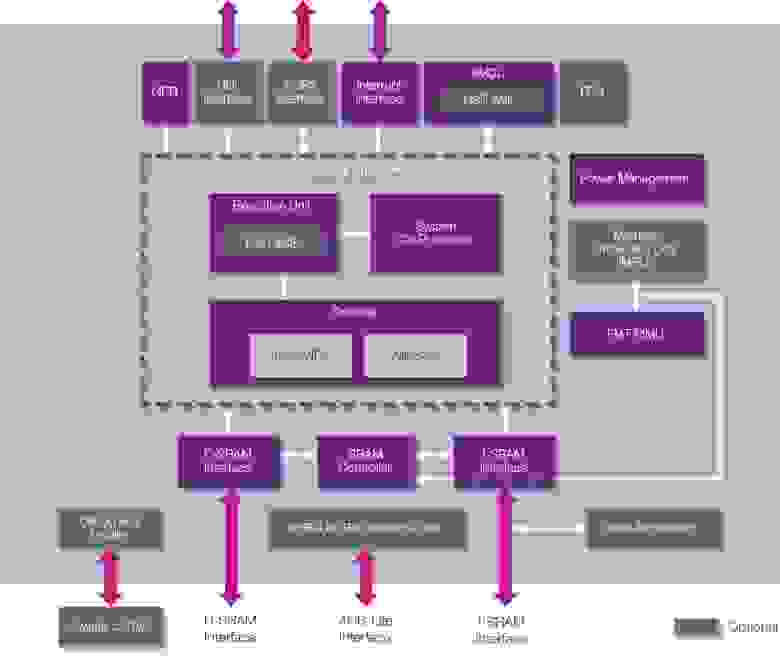

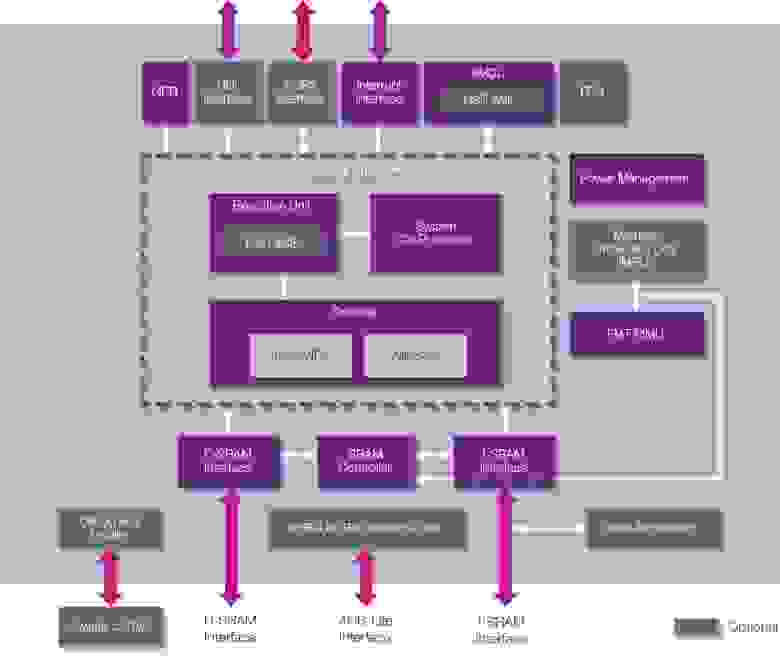

MIPS microAptiv UP представляет собой простую конструкцию с пятиэтапным последовательным конвейером (как в учебниках по компьютерной архитектуре), но имеет кэши и TLB MMU. TLB MMU даже позволяет использовать на нем Linux.

Описание ядра: www.imgtec.com/mips/aptiv/microaptiv.asp

Наиболее широко известным примером ядра MIPS microAptiv UP является 32-битный микроконтроллер Microchip PIC32MZ, производство которого началось в прошлом году.

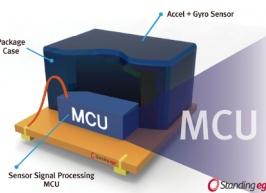

И из самых свежих примеров использования: 10 апреля этого года Electronic Engineering Times опубликовала статью о южнокорейском стартапе Standing Egg, который лицензировал ядро MIPS M5100 (фактически MIPS microAptiv без кешей и MMU, но с добавленным расширением).

для виртуализации) для создания платформы для МЭМС-сенсоров с приложениями для Интернета вещей: www.eetimes.com/document.aspЭdoc_id=1326327

Разработчики микросхем MIPS microAptiv UP используют методологию электронного проектирования, которая стала стандартной в течение последних 20 лет и называется уровнем передачи регистров (RTL).

По этой методике проект пишется на языке Verilog, после чего специальная программа (логический синтез) превращает проект в граф проводов и логических элементов, другая программа (статический временной анализ) сообщает проектировщику, укладывается ли он в скорость бюджет, а третья программа (размещение и маршрутизация) прокладывает этот проект по всей площади чипа.

Когда проект проходит все этапы: кодирование Verilog, отладка, проверка, синтез, статический временной анализ, планировка помещений, размещение и маршрутизация, извлечение паразитов и т. д. — получается файл под названием GDSII, который отправляется на фабрику.

где микросхемы производятся.

Самые известные заводы этого типа принадлежат Тайваньской компании по производству полупроводников или TSMC. При этом ничто не мешает производить микросхемы с ядром MIPS microAptiv UP на российских заводах «Микрон» и «Ангстрем».

Альтернативой производству чипа на заводе является реализация проекта на программируемой пользователем вентильной матрице (FPGA), которую новый продукт MIPSfpga использует в образовательных целях.

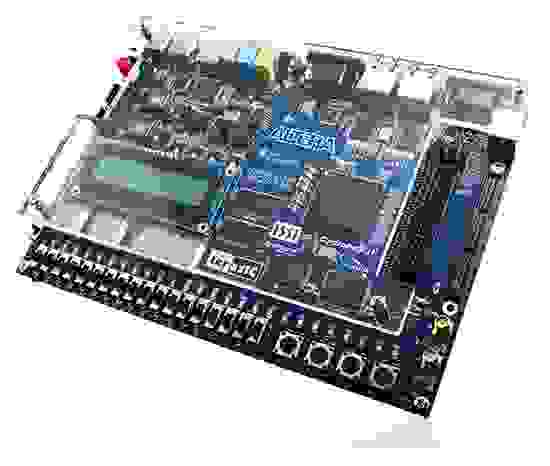

Хотя пакет MIPSfpga предназначен для синтеза для FPGA (например, MIPSfpga имеет реализацию памяти внутри кэшей с использованием макросов для Xilinx Artix-7 и Altera Cyclone IV), по сути это те же источники, которые используются для синтеза в ASIC. Другими словами, студенты и аспиранты могут поэкспериментировать с ядром на недорогих FPGA-платах, придумать какое-нибудь интересное решение (скажем, многоядерную SoC из маленьких некогерентных ядер или комбинацию ядра MIPS microAptiv UP со специализированным студенческим ядром).

DSP процессор), не вкладывая деньги инвесторов, а затем, когда идея будет доказана, найти инвесторов, приобрести коммерческую лицензию и сделать на заводе чип — ASIC. Обратите внимание, что в случае с MIPSfpga мы говорим не об ограниченном образовательном подмножестве MIPS (таких подмножеств из других источников достаточно много) и не о открытом ядре типа OpenRISC или Leon4, а о коммерчески успешном современное промышленное ядро, на которое лицензировали несколько десятков компаний.

У конкурирующей компании ARM также есть программное ядро для образовательных экспериментов над FPGA, но их ядро не находится в открытом исходном коде (т. е.

студенты не могут подключать провода к внутренним регистрам и модифицировать verilog), тогда как у ARM ядра ARM Cortex M0 есть конкурирующее продукт. иметь кэши, интерфейс для отладчика или TLB MMU. MIPSfpga имеет все это.

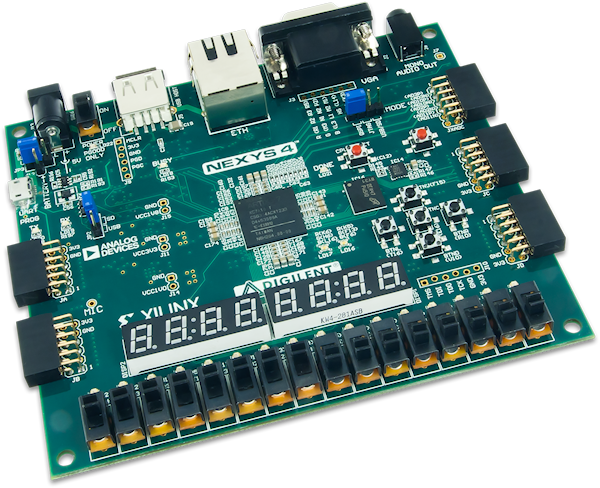

Дополнительные детали: MIPSfpga в настоящее время работает на двух платах Digilent Nexys-4 с Xilinx Artix-7 и Altera DE2-115 с Cyclone IV E. Первая имеет академическую цену 180 долларов США / коммерческую 320 долларов США, вторую — академическую цену 300 долларов США / коммерческую 600 долларов США.

Перенести его на другие платы (при условии, что он подходит) довольно легко — нужно заменить некоторые макросы на память и подключить топ-модуль к конкретной внешней обертке verilog. В частности, можно попробовать портировать его на дешевую плату Digilent Basys-3 с Xilinx Artix-7 (80 долларов академическая / 150 долларов коммерческую), а также на платы, разработанные или произведенные в России.

Codescape MIPS SDK предлагается в виде набора инструментов, который содержит отладчик и набор инструментов GCC. Связь между отладчиком и платой Nexys-4 осуществляется с помощью EJTAG, зонда BusBlaster и OpenOCD. Altera DE2 115 использует интерфейс отладки, расположенный непосредственно на плате, т.е.

BusBlaster не требуется.

Также включен загрузочный код на ассемблере, который инициализирует кеши, MMU и т. д. Какое это имеет отношение к вам: 1. Успешно завершен первый этап тестирования MIPSfpga в трех университетах США и Великобритании.

Теперь продукт пройдет бета-тестирование в других университетах США, Европы и Азии.

Если вы работаете в университете и он обладает достаточным опытом работы с Verilog или VHDL для работы с пакетом, то вы можете принять участие в качестве раннего пользователя и получить преимущество перед другими университетами при его использовании.

2. 13-14 мая в Лос-Анджелесе пройдет семинар, организованный компаниями Imagination Technologies и Xilinx, на котором профессора из колледжа Харви Мадда и инженеры-прикладники из Imagination будут обучать профессоров различных университетов использованию MIPSfpga. Если вы или любой профессор университета, которого вы знаете, хотели бы принять в нем участие и можете приехать в Лос-Анджелес в это время, свяжитесь с менеджером образовательной программы Робертом Оуэном (его контактная информация находится по адресу: imgtec.com/mipsfpga ), или у меня ([email protected]).

3. Ко времени семинара в Лос-Анджелесе MIPSfpga будет официально анонсирована, а после завершения (1) станет общедоступной.

Поэтому, если вы не сможете принять участие в качестве раннего пользователя, вы, тем не менее, сможете начать работу с продуктом летом.

Возможность использования ядер промышленных процессоров на Verilog в образовательных целях и без покупки коммерческой лицензии позволит большому количеству молодых разработчиков в академических кругах начать прототипировать инновационные решения в области систем на кристалле и расширений микроархитектуры, имея прямой путь к коммерциализация – создание собственных чипов для Интернета вещей и других приложений.

Юрий Панчул Старший инженер-проектировщик аппаратного обеспечения, процессоры MIPS Imagination Technologies Участвовать в опросе могут только зарегистрированные пользователи.

Войти , Пожалуйста.

Какими из упомянутых технологий вы владеете или планируете освоить? 71,32% Основы цифровой схемотехники 92 37,98% Язык описания аппаратного обеспечения Verilog, подмножество для уровня передачи регистров (RTL) 49 25,58% Язык описания аппаратного обеспечения VHDL, подмножество для уровня передачи регистров (RTL) 33 19,38% Язык описания аппаратного обеспечения Verilog, подмножество для верификация 25 15,5 % Язык описания аппаратуры VHDL, подмножество для проверки 20 12,4 % SystemVerilog 16 68,22 % Архитектура процессора – набор команд, ассемблер 88 34,88 % Микроархитектура процессоров – организация конвейеров, вычислительных блоков 45 13,95 % Разработка систем на кристалле, уровень верификации протоколов и систем 18 14,73% Разработка систем на кристалле, физический уровень 19 3,1% Другое (расскажите в комментариях) Проголосовали 4 129 пользователей.

85 пользователей воздержались.

Теги: #Процессоры #verilog #vhdl #vhdl #vhdl #vhdl #системы на кристалле #FPGA #ASIC #Системный анализ и проектирование

-

Безопасность Точки Доступа Wi-Fi

19 Oct, 24 -

Локальный Прокси-Сервер Для Siri

19 Oct, 24 -

5,8 Миллиона Iops: Почему Так Много?

19 Oct, 24 -

Надстройка Для Expression Blend 2.5

19 Oct, 24