Еще в 2011 году Xilinx представила свои первые чипы SoC (System On Chip) — Zynq-7000. Zynq SoC сочетает в себе программируемую логику, процессорный модуль и некоторые периферийные устройства.

Статья не является наиболее полным описанием SoC Zynq, а лишь отражает некоторые характеристики, с которыми пришлось столкнуться при разработке устройств на базе SoC Zynq.

Содержание

1 Общая информация 2 порта 2,1 млн МО 2.2 ЭМИО 2.3 Г.П.

2,4 л.

с.

2.5 АКП 3 Периферия 3.1 Контроллер статической памяти 3.2 Флэш-контроллер Quad-SPI 3.3 Контроллер SD/SDIO 3.4 Ввод-вывод общего назначения (GPIO) 3.5 USB-хост, устройство и контроллер OTG 3,6-гигабитный Ethernet-контроллер 3.7 SPI-контроллер 3.8 CAN-контроллер 3.9 UART-контроллер 3.10 Контроллер I2C 3.11 Интерфейс XADC 4 Процессорный модуль 5 Программируемая логика 6 Производительность 6.1 Теоретический 6.2 Практичность 6.2.1 Обработка сетевых пакетов 6.2.2 Производительность порта HP 7 Передача данных между процессорным модулем и программируемой логикой 8 Загрузка SoC 9 проблем 10 Создание файла конфигурации 11 Заключение 12 использованных источников

1 Общая информация

Блок-схема Zynq. Каждый Zynq состоит из одного или двух ядер ARM Cortex-A9 (ARM v7), каждое ядро имеет собственный кеш L1, а кеш L2 является общим.

Поддерживаемая оперативная память имеет стандарты DDR3, DDR3L, DDR2, LPDDR-2. Максимальный объем оперативной памяти — 1 ГБ (2 чипа по 4 Гбит каждый).

Максимальная тактовая частота оперативной памяти составляет 525 МГц.

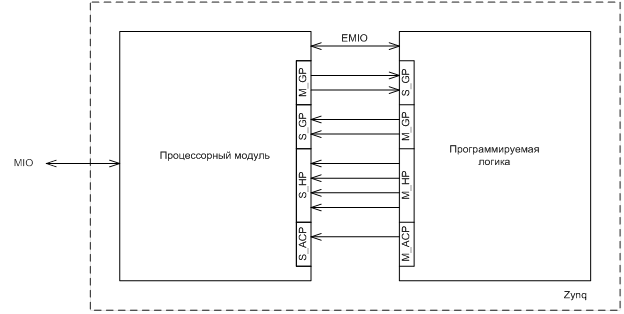

Операционные системы: Standalone (голое железо) и Petalinux. Процессорный модуль общается с внешним миром и программируемой логикой с помощью портов, сгруппированных в группы:

- MIO (мультиплексный ввод-вывод);

- EMIO (расширенный мультиплексированный ввод-вывод);

- GP (порты общего назначения);

- HP (высокопроизводительные порты);

- ACP (порт когерентности ускорителя).

Схема интерфейса Zynq. Буквы S и M на порту обозначают ведомое и ведущее устройства соответственно.

Поскольку и процессорный модуль, и программируемая логика реализованы в одном корпусе Zynq, существуют выводы, относящиеся к процессорному модулю, и выводы, относящиеся к программируемой логике.

2 порта

2,1 млн МО

Порты MIO подключены к контактам процессора.С помощью MIO можно подключить следующие периферийные устройства процессорного модуля:

- USB-контроллер – 2 шт;

- Контроллер Gigabit Ethernet – 2 шт.;

- Контроллер SD/SDIO – 2 шт.;

- UART – 2 шт;

- CAN – 2 шт;

- I2C – 2 шт;

- СПИ – 2 шт;

- ГПИО.

Все контакты можно использовать как контакты общего назначения.

- QSPI-контроллер;

- ОНФИ-контроллер;

- Контроллер SRAM/NOR.

Поэтому включить все сразу не получится.

Для решения этой проблемы существует группа портов EMIO.

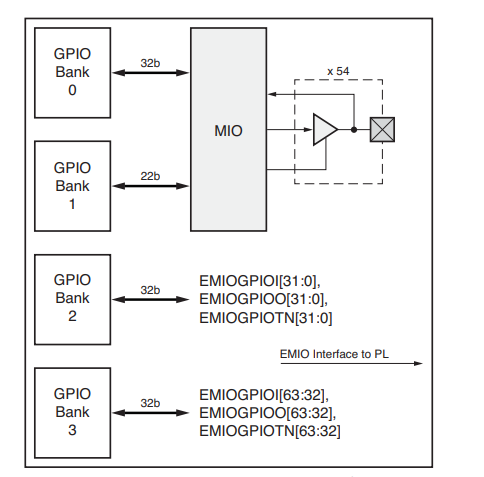

2.2 ЭМИО

EMIO – это переадресация периферийного устройства от процессорного модуля к программируемой логике и подключение периферийного устройства к выходам программируемой логики.Однако не все периферийные устройства можно перенести через EMIO, некоторые не передаются вообще (USB), некоторые с изменением функционала (Ethernet через EMIO имеет интерфейс GMII для подключения внешнего чипа физического уровня).

Между процессорным модулем и программируемой логикой через порт EMIO можно подключить 192 сигнала (64 входа и 128 выходов).

2.3 Г.

П.

Порты GP используют протокол Axi4. Протокол предполагает работу с данными шириной до 32 бит. За одну транзакцию передаются/принимаются данные не более 8*32 бит (размер boost-транзакции — 8).

Обычно используется для управления блоками программируемой логики или низкоскоростной связи.

Имеется 2 главных порта и 2 ведомых порта.

2,4 л.

с.

Порты HP используют протокол AXI4. Протокол предполагает работу с данными шириной 32 или 64 бита.

Протокол поддерживает повышающие транзакции.

За одну транзакцию передается/принимается произвольный объем данных.

Его используют, как правило, для организации высокоскоростного обмена данными между процессорным модулем и программируемой логикой.

Имеется 4 подчиненных порта.

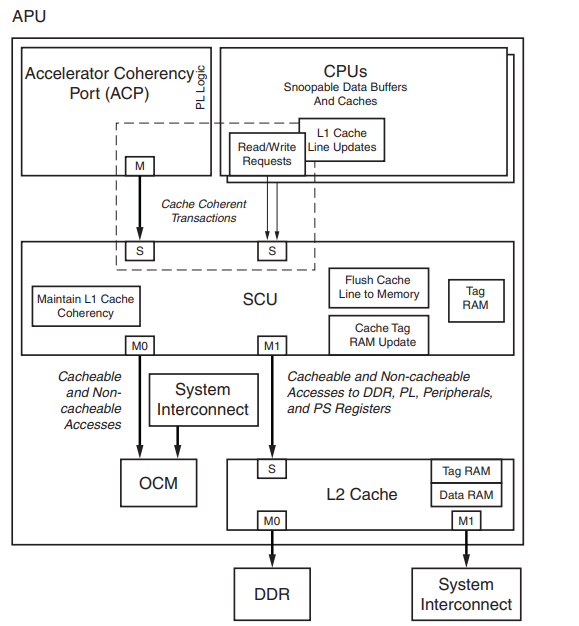

2.5 АКП

Порт ACP использует протокол AXI4. Протокол предполагает работу с 64-битными данными.Протокол поддерживает повышающие транзакции.

За одну транзакцию передается/принимается произвольный объем данных.

Он используется, как правило, для организации высокоскоростного обмена данными между процессорным модулем и программируемой логикой, причем данные дополнительно помещаются в кэш L2. Имеется один подчиненный порт.

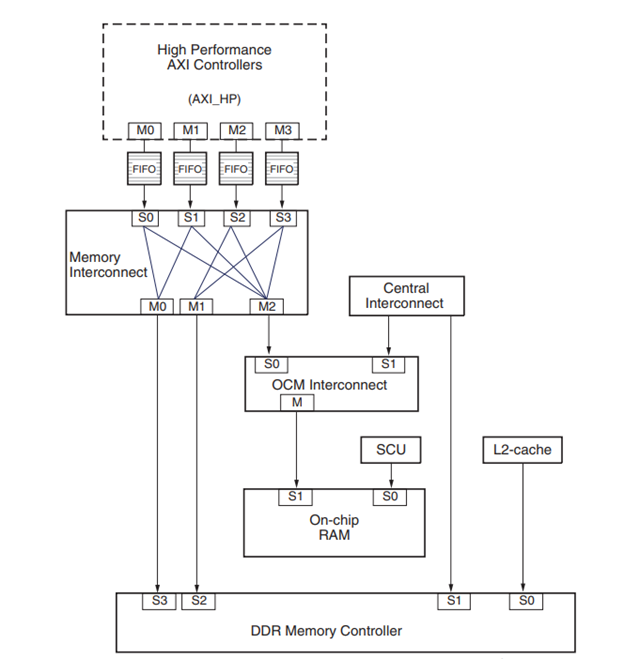

Путь данных с использованием порта ACP

3 Периферия

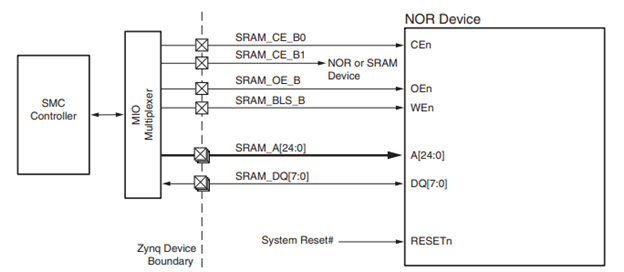

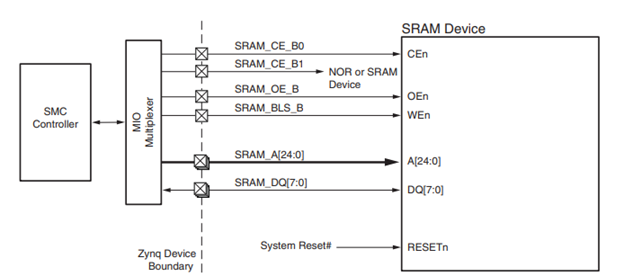

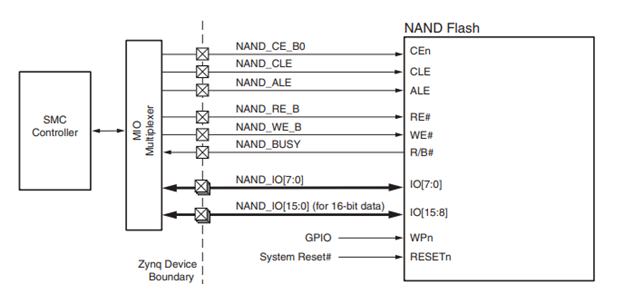

3.1 Контроллер статической памяти

SMC используется как контроллер памяти NAND или как контроллер параллельной памяти.Поддерживает следующие типы памяти:

- NAND-вспышка;

- НИ вспышка;

- асинхронная SRAM.

- Поддержка спецификации ONFI 1.0;

- поддержка микросхем памяти емкостью до 1 ГБ;

- 1 бит ECC, считываемый аппаратно (используется, если микросхема флэш-памяти не поддерживает ECC).

- 8 или 16 линий обмена данными и одна линия выбора чипа (Chip Select);

- асинхронный режим работы.

- 8 линий данных;

- 2 линии выбора чипа (Chip Select);

- 25 адресных строк;

- Асинхронный режим работы.

Подключение чипа NOR Flash с параллельным интерфейсом

Подключение микросхемы SRAM с параллельным интерфейсом

Подключение чипа NAND Flash

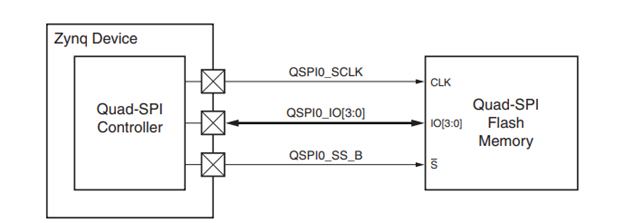

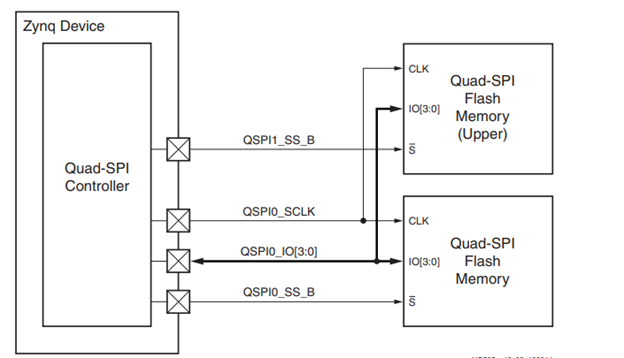

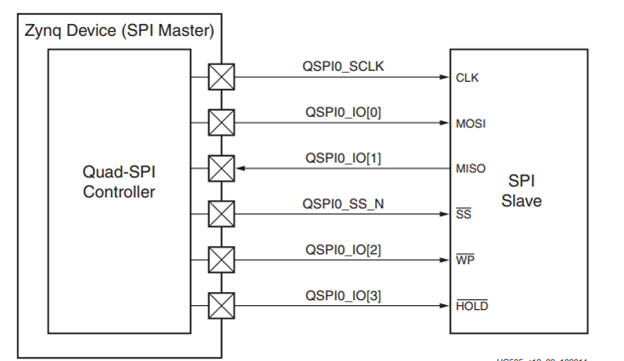

3.2 Флэш-контроллер Quad-SPI

Реализует SPI-контроллер для подключения внешних микросхем памяти по технологии NOR. Основные показатели:- Поддержка флэш-памяти от Micron и Spansion;

- регулируемая ширина шины (1x, 2x, 4x, 8x);

- тактовая частота до 100 МГц

- один сигнал выбора чипа (Chip Select/Slave Select), 4 двунаправленные линии данных;

- два сигнала выбора чипа (Chip Select/Slave Select), 8 двунаправленных линий передачи данных (параллельное соединение);

- два сигнала выбора чипа (Chip Select/Slave Select), двунаправленные 4 линии для данных (общее переключение);

- один сигнал выбора чипа (Chip Select/Slave Select), одна линия для передачи, одна линия для приема.

Один чип, 4 двунаправленные линии передачи данных

Два чипа, 8 двунаправленных линий передачи данных

Два чипа, 4 двунаправленные линии

Один чип, каждая линия однонаправленная

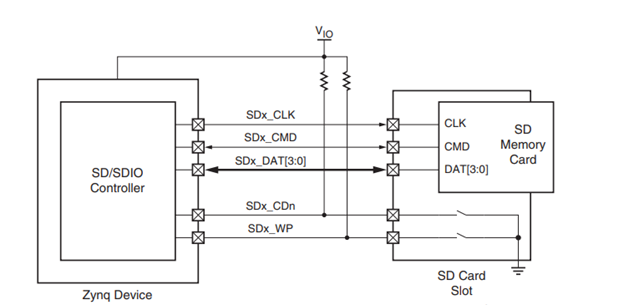

3.3 Контроллер SD/SDIO

Заявлена поддержка устройств eMMC, но без гарантии, что все будет работать корректно (ожидается, что SoC Zynq-7000 будет работать с устройствами eMMC, поскольку протокол такой же, как у SD, но это не подвергалось тщательной проверке).Основные показатели:

- Поддержка спецификации SD Host Controller 2.0;

- поддержка карт SDHS и SDHC;

- Поддержка стандарта MMC3.31;

- Режим только хоста;

- максимальная тактовая частота 50 МГц;

- Режим SPI не поддерживается.

Подключение SD-карты

3.4 Ввод-вывод общего назначения (GPIO)

Каждый из портов может использоваться в следующем режиме:- вход;

- Выход;

- выход с третьим состоянием;

- вход, изменение данных которого генерирует прерывание.

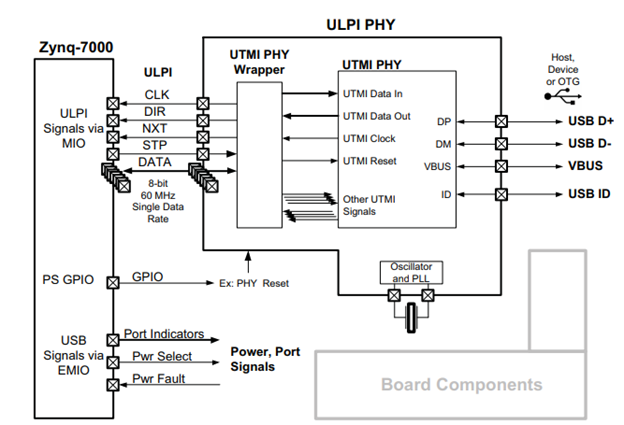

3.5 USB-хост, устройство и контроллер OTG

Требуется внешний чип физического уровня с интерфейсом ULPI. Основные показатели:- поддержка интерфейса 2.0;

- до 12 конечных точек/конечных точек (одна контрольная и 11 пользовательских);

- ОТГ 1.3;

- все типы транзакций (Управление, Массовые, Прерывания, Изохронные);

- Поддерживаются режимы OTG, USB-хост, USB-устройство.

Подключение USB-контроллера

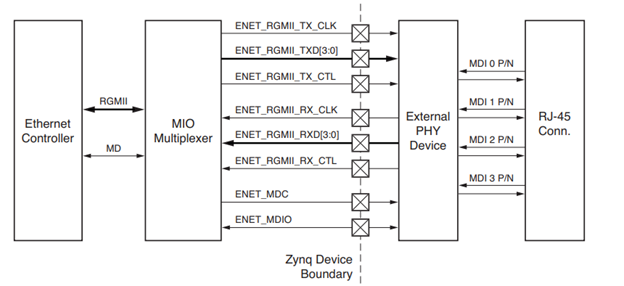

3,6-гигабитный Ethernet-контроллер

Требуется внешний чип физического уровня с интерфейсом RGMII. Основные показатели:- поддержка скоростей 10/100/1000 Мбит/с;

- поддержка полнодуплексного и полудуплексного режимов;

- расчет контрольной суммы для IP, TCP, UDP в версиях протокола IPv4 и IPv6;

- Jumbo Frames не поддерживаются;

- Гигабитный полудуплекс не поддерживается;

- поддержка VLAN;

- Поддержка Wake-on-LAN.

Подключение сетевого контроллера.

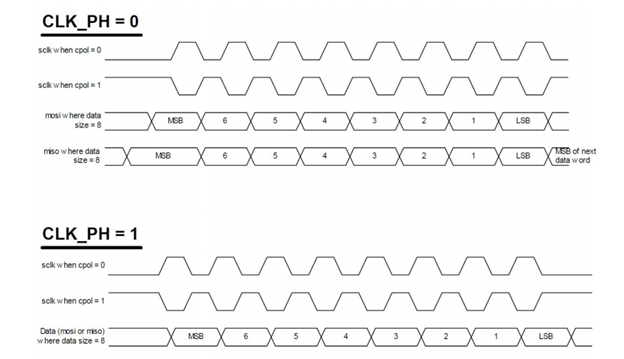

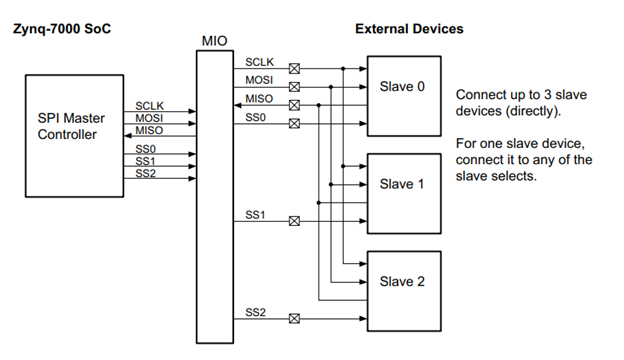

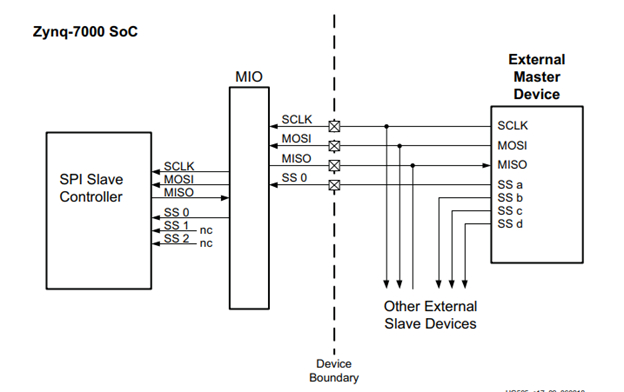

3.7 SPI-контроллер

Основные показатели:- работа в режиме Master,Slave,Multi-Master;

- поддержка работы с тремя устройствами в режиме Master, по 3 линиям SS (Slave Select);

- Поддерживает одновременную передачу и прием;

- тактовый сигнал до 50 МГц при использовании MIO, до 25 МГц при использовании EMIO;

- настраиваемые режимы фазы и полярности тактового сигнала (CPHA, CPOL).

Фазы и полярность часов

Подключение SPI-контроллера в режиме Master

Подключение SPI-контроллера в ведомом режиме

3.8 CAN-контроллер

Основные показатели:- поддержка стандартов CAN 2.0A и CAN 2.0B;

- поддержка кадров с длиной идентификатора 11 и 29 бит;

- скорость до 1 Мбит/с.

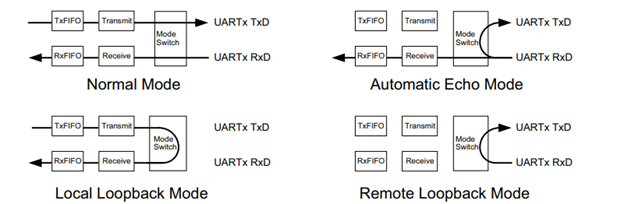

3.9 UART-контроллер

Основные показатели:- регулируемая скорость передачи;

- регулируемое количество бит данных – 6, 7, 8;

- регулируемое количество стоп-битов – 1, 1,5, 2;

- паритетный контроль;

- передача данных в режимах «Обычный», «Автоматическое эхо», «Локальный шлейф», «Удаленный шлейф».

Режимы работы UART-контроллера

3.10 Контроллер I2C

Основные показатели:- скорость обмена до 400 Кбит/с;

- Поддержка версии 2 спецификации;

- работать в режиме Master и Slave.

3.11 Интерфейс XADC

Аналоговый модуль смешанных сигналов Xilinx. Аналого-цифровой преобразователь.

В его состав входят 2 двенадцатиразрядных АЦП с частотой дискретизации 1 MSPS, аналоговый мультиплексор (до 17 внешних аналоговых каналов), а также встроенные датчики температуры и напряжения микросхемы Zynq. Аналоговые входы поддерживают полосу пропускания сигнала до 500 кГц при частоте дискретизации 1 MSPS.

4 Процессорный модуль

Каждый Zynq, как уже говорилось выше, содержит одно или два процессорных ядра.Максимальная тактовая частота ядер зависит от класса скорости чипа (Speed Grade) [1].

Возможны 5 классов скорости: -1, -1L, -2, -2L, -3. Классы с индексом L характеризуются пониженным напряжением питания.

Количество ядер и зависимость максимальной частоты от класса быстродействия микросхемы

| Чип | Количество ядер | Максимальная тактовая частота, МГц | ||

|---|---|---|---|---|

| -1 | -2 | -3 | ||

| Z-7007S | 1 | 667 | 766 | - |

| Z-7012S | 1 | 667 | 766 | - |

| Z-7014SS | 1 | 667 | 766 | - |

| Z-7010 | 2 | 667 | 766 | 866 |

| Z-7015 | 2 | 667 | 766 | 866 |

| Z-7020 | 2 | 667 | 766 | 866 |

| Z-7030 | 2 | 667 | 800 | 1000 |

| Z-7035 | 2 | 667 | 800 | 1000 |

| Z-7045 | 2 | 667 | 800 | 1000 |

| Z-7100 | 2 | 667 | 800 | - |

5 Программируемая логика

Программируемая логика, используемая в Zynq, основана на двух семействах FPGA: Artix-7 и Kintex-7. Артикс позиционируется как менее производительный и с меньшим расходом.Соответственно, Кинтекс более производительный и с более высоким расходом.

На практике они различаются количеством доступных ресурсов и типом высокоскоростных трансиверов (GTP со скоростью до 6,25 Гбит/с в Artix и GTX со скоростью до 12,5 Гбит/с в Kintex) [2].

Программируемые логические характеристики

| Чип | Семья | Логические ячейки | ЛУТ | Триггеры | БРЭМ | ЦСП | ГТП/ГТХ |

|---|---|---|---|---|---|---|---|

| Z-7007S | Артикс | 23 тыс.

|

14400 | 28800 | 50 | 66 | - |

| Z-7012S | Артикс | 55 тыс.

|

34400 | 68800 | 72 | 120 | 4 |

| Z-7014S | Артикс | 65 тыс.

|

40600 | 81200 | 107 | 170 | - |

| Z-7010 | Артикс | 28К | 17600 | 35200 | 60 | 80 | - |

| Z-7015 | Артикс | 74К | 46200 | 92400 | 95 | 160 | 4 |

| Z-7020 | Артикс | 85 тыс.

|

53200 | 106400 | 140 | 220 | - |

| Z-7030 | Кинтекс | 125 тыс.

|

78600 | 157200 | 265 | 400 | 4 |

| Z-7035 | Кинтекс | 275 тыс.

|

171900 | 343800 | 500 | 900 | 16 |

| Z-7045 | Кинтекс | 350 тыс.

|

218600 | 437200 | 545 | 900 | 16 |

| Z-7100 | Кинтекс | 444К | 277400 | 554800 | 755 | 2020 | 16 |

BRAM (Block RAM) – используется для хранения данных.

Размер одной BRAM = 36Кбит. Примечание.

Количество доступных GTP/GTX также зависит от используемого корпуса.

В таблице указано максимальное значение.

6 Производительность

6.1 Теоретический

В таблице ниже приведены теоретические значения пропускной способности между процессорным модулем и программируемой логикой, а также пропускная способность памяти.Следует понимать, что производительность получается умножением тактового сигнала на ширину интерфейса и не отражает реальную картину передачи данных.

Теоретическая пропускная способность между процессорным модулем и программируемой логикой

| Интерфейс | Г.

П.

|

Г.

П.

|

HP | АШП | ГДР | ОКМ |

|---|---|---|---|---|---|---|

| Тип | PS Раб | ПС Мастер | PS Раб | PS Раб | Внешняя память | Внутренняя память |

| Ширина шины, бит | 32 | 32 | 64 | 64 | 32 | 64 |

| Тактовый сигнал, МГц | 150 | 150 | 150 | 150 | 1066 | 222 |

| Чтение, МБ/с | 600 | 600 | 1200 | 1200 | 4264 | 1779 |

| Запись, МБ/с | 600 | 600 | 1200 | 1200 | 4264 | 1779 |

| Чтение + запись, МБ/с | 1200 | 1200 | 2400 | 2400 | 4264 | 3557 |

| Количество интерфейсов | 2 | 2 | 4 | 1 | 1 | 1 |

| Суммарная пропускная способность, МБ/с | 2400 | 2400 | 9600 | 2400 | 4264 | 3557 |

| прямой доступ к памяти | ДМАК | Ethernet-контроллер | USB-контроллер | SD-контроллер |

|---|---|---|---|---|

| Тип | АРМ ПЛ310 | ПС Мастер | ПС Мастер | ПС Мастер |

| Ширина шины, бит | 64 | 4 | 8 | 4 |

| Тактовый сигнал, МГц | 222 | 250 | 60 | 50 |

| Чтение, МБ/с | 1776 | 125 | 60 | 25 |

| Запись, МБ/с | 1776 | 125 | 60 | 25 |

| Чтение + запись, МБ/с | 3552 | 250 | 60 | 25 |

| Количество интерфейсов | 1 | 2 | 2 | 2 |

| Суммарная пропускная способность, МБ/с | 3552 | 500 | 120 | 50 |

| Межсоединение | Часовой домен | Ширина, бит | Тактовый сигнал, МГц | Чтение, МБ/с | Запись, МБ/с | Чтение + запись, МБ/с |

|---|---|---|---|---|---|---|

| Центральный межконнект | ЦП_2x | 64 | 222 | 1776 | 1776 | 3552 |

| Мастера | ЦП_1x | 32 | 111 | 444 | 444 | 888 |

| Рабы | ЦП_1x | 32 | 111 | 444 | 444 | 888 |

| Мастер-интерконнект | ЦП_2x | 32 | 222 | 888 | 888 | 1776 |

| Подчиненное соединение | ЦП_2x | 32 | 222 | 888 | 888 | 1776 |

| Соединение памяти | DDR_2x | 64 | 355 | 2840 | 2840 | 5680 |

Пропускная способность чтения DDR ограничена 2840 МБ/с из-за использования Memory Interconnect[3].

6.2 Практичность

Производительность на практике, конечно, оказывается ниже теоретической.

При разработке устройств на базе Zynq нас интересовала производительность обработки сетевых пакетов и производительность портов HP.

6.2.1 Обработка сетевых пакетов

Производительность обработки сетевых пакетов| Схема подключения | Протокол | МТУ | ТХ, Мбит/с | Загрузка процессора, % | Приём, Мбит/с | Загрузка процессора, % |

|---|---|---|---|---|---|---|

| ПЛ Ethernet | TCP | 1500 | 824 | 70.7 | 651 | 89.5 |

| TCP | 8192 | 988 | 45.8 | 818 | 55.3 | |

| UDP | 1500 | 583 | 54.4 | 565 | 66.2 | |

| UDP | 8192 | 737 | 33.6 | 876 | 85.8 | |

| PS ЭМИО | TCP | 1500 | 801 | - | 756 | - |

| ПС МИО | TCP | 1500 | 678 | - | 691 | - |

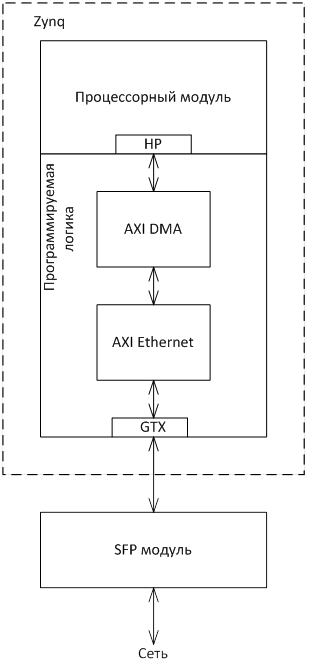

Подключение показано на схеме ниже.

Расчеты контрольной суммы для протоколов IP, TCP, UDP выполняются ядром Axi Ethernet. Процессор используется для генерации и обработки сетевых пакетов.

В тесте использовалась операционная система Petalinux с версией ядра 4.19. Измерение проводилось на плате ZC706, на которой был установлен чип Z-7045 с классом скорости -2. Согласно таблице выше, процессорный модуль содержит 2 ядра и работает на тактовой частоте до 800 МГц [4].

ПЛ Ethernet-соединение

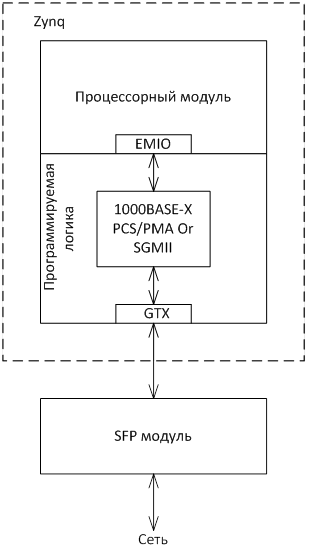

При использовании схемы подключения PS EMIO используется Ethernet-контроллер, реализованный в процессорном модуле.

Подключение показано на схеме ниже.

Вычисление контрольных сумм протоколов IP, TCP, UDP осуществляется ядром процессорного модуля.

Программируемая логика используется для преобразования интерфейсов для подключения внешнего чипа физического уровня.

В тесте использовалась операционная система Petalinux с версией ядра 4.6. Измерение проводилось на плате ZC706, на которой был установлен чип Z-7045 с классом скорости -2. Согласно таблице выше, процессорный модуль содержит 2 ядра и работает на тактовой частоте до 800 МГц [5].

PS ЭМИО подключение

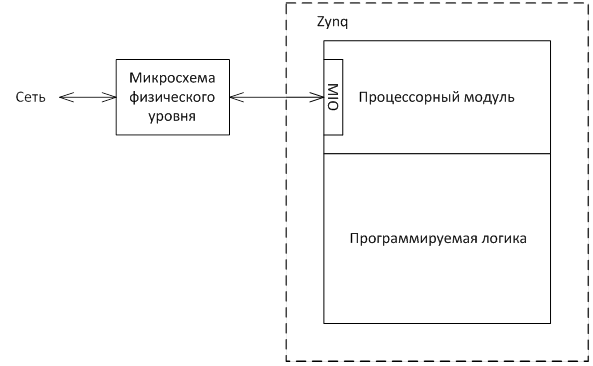

При использовании схемы подключения PS MIO используется Ethernet-контроллер, реализованный в процессорном модуле.

Подключение показано на схеме ниже.

Вычисление контрольных сумм протоколов IP, TCP, UDP осуществляется ядром процессорного модуля.

Вычисление контрольных сумм протоколов IP, TCP, UDP осуществляется ядром процессорного модуля.

В тесте использовалась операционная система Petalinux с ядром версии 4.0. Измерение проводилось на плате Zybo, на которой был установлен чип Z-7010 с классом скорости -1. Согласно таблице выше, процессорный модуль содержит 2 ядра и работает на тактовой частоте до 667 МГц.

Подключение PS МИО Производительность сетевого контроллера в режиме Rx+Tx

| Схема подключения | Протокол | МТУ | ТХ, Мбит/с | Приём, Мбит/с |

|---|---|---|---|---|

| PS ЭМИО | TCP | 1500 | 470 | 218 |

Итого: если вам нужно обрабатывать сетевые пакеты на скорости 1 Гбит/с, то Zynq для этой задачи не подходит.

6.2.2 Производительность порта HP

Теоретическая пропускная способность порта HP составляет 9,6 Гбит/с.Для тестирования пропускной способности мы использовали плату Mini-ITX, на которой был установлен чип Z-7100 с классом скорости -2. Согласно таблице выше, процессорный модуль содержит 2 ядра и работает на тактовой частоте до 800 МГц.

Операционная система Petalinux с версией ядра Теги: #Программирование микроконтроллеров #Процессоры #производительность #FPGA #обзор #тест скорости #zynq-7000 #создание прошивки #Zynq PS #Zynq PL

-

Оскп - Мой Опыт

19 Oct, 24 -

Как Пройти Кибертесты На Checkpoint

19 Oct, 24 -

Харадий

19 Oct, 24 -

Взлом Библиотеки От Гэотар-Медиа

19 Oct, 24