Находится на борту космического корабля «Аполлон».

управляющий компьютер (Apollo Guidance Computer, AGC) помог кораблю добраться до Луны и приземлиться на ее поверхность.

Программное обеспечение AGC было физически встроено в постоянную память на неоднократно сшитый ядра [основная веревочная память].

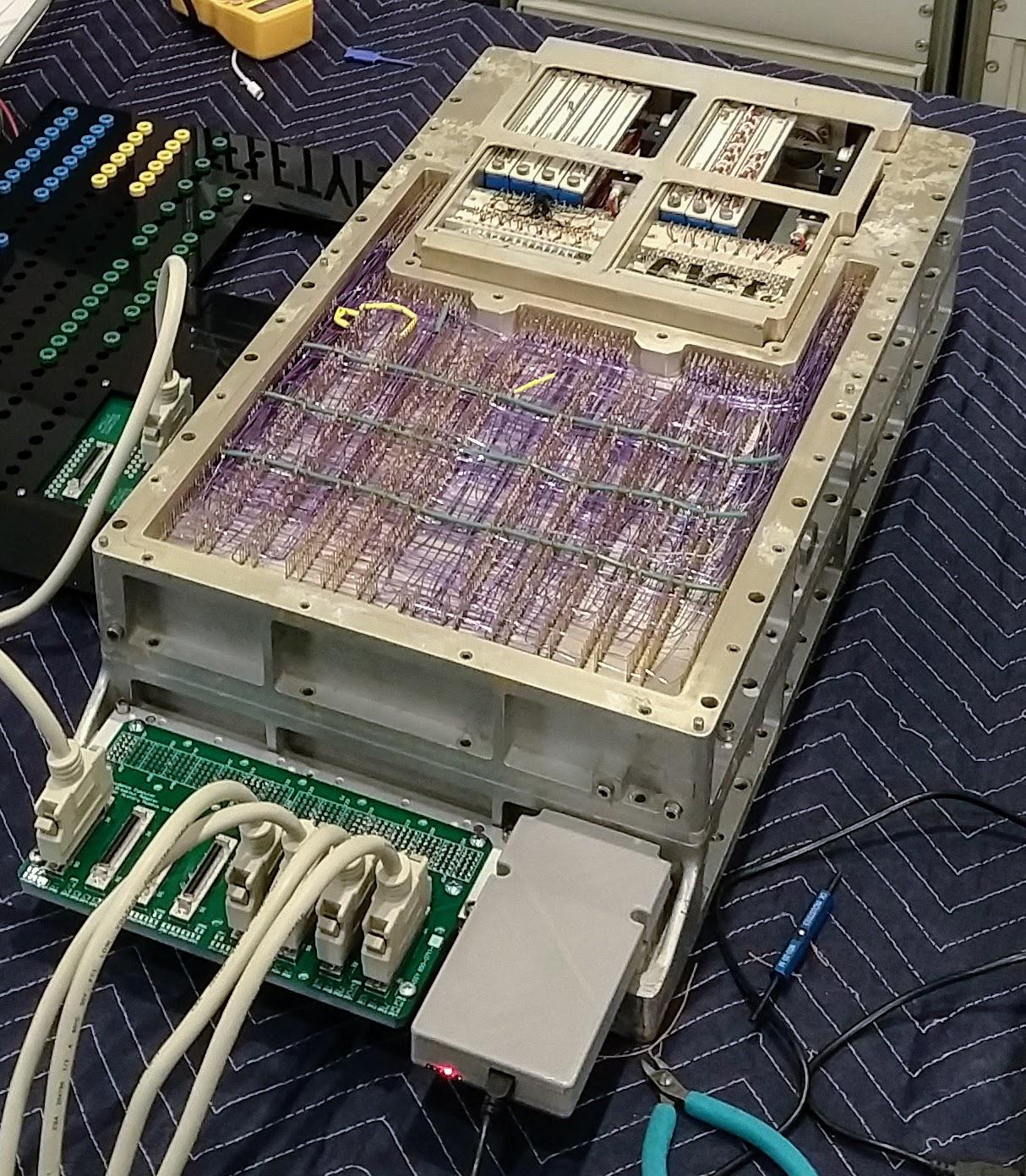

Кен Ширрифф и его единомышленники восстанавливают АРУ (на фото ниже), которому не хватает памяти на ядрах, вместо которого установлены коробки-симуляторы такой памяти.

Эти коробки использовались при разработке программ и наземных испытаниях, чтобы инженерам не приходилось постоянно прошивать память.

У симулятора отсутствует документация, поэтому я [автор записи в блоге / прим.

перев.

] провели его инженерный анализ, собрали интерфейс и с помощью симулятора запустили программы на нашем АРУ.

Однако в процессе мы столкнулись с некоторыми трудностями.

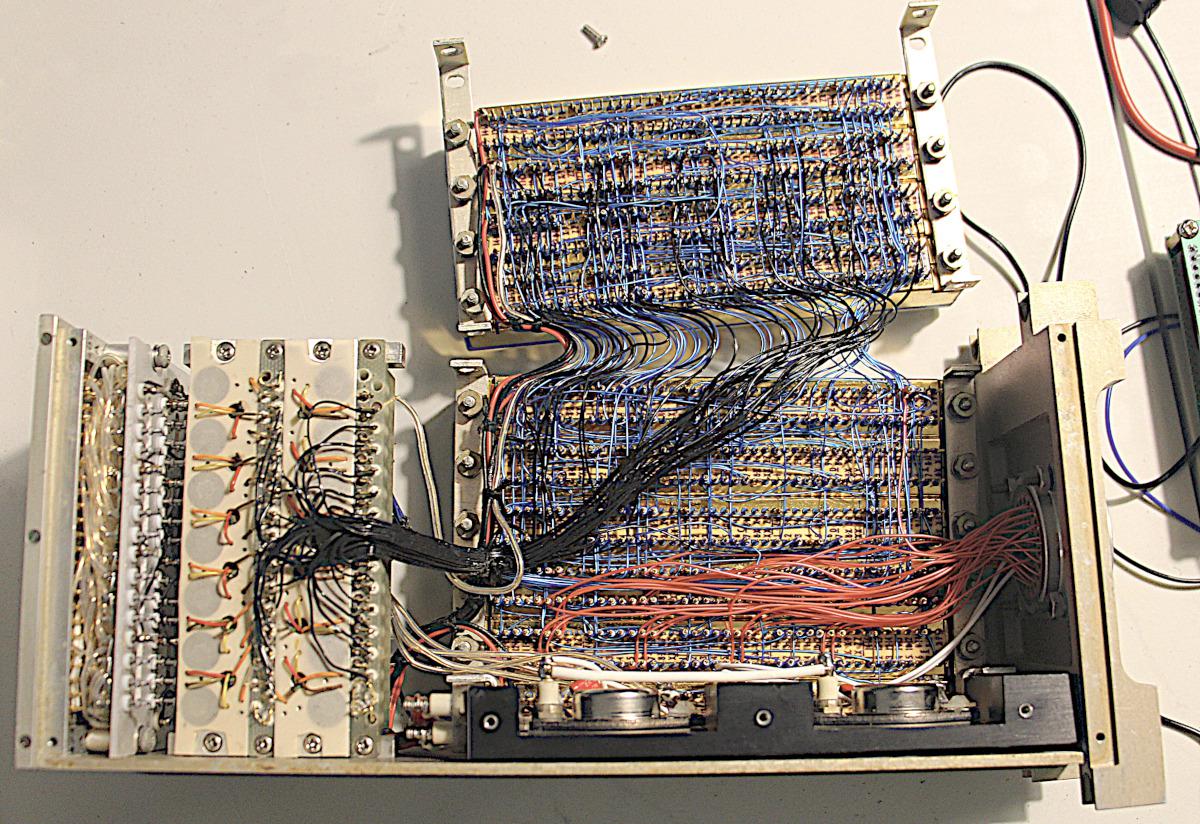

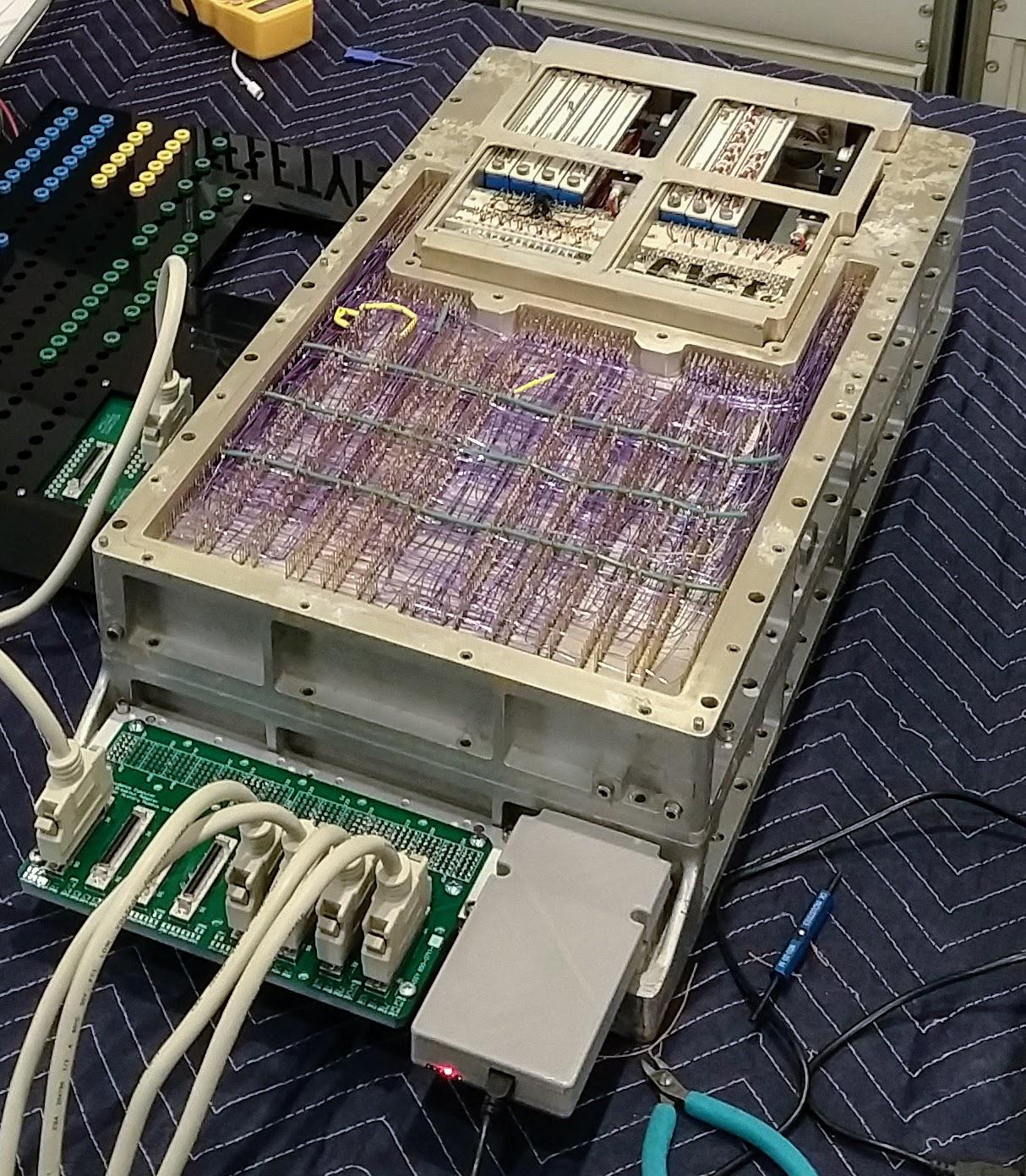

Компьютер AGC со снятой крышкой.

Вы можете увидеть материнскую плату с кучей проводов.

В складских помещениях видны ящики с симуляторами.

Платы интерфейса на переднем плане современные.

Память на нескольких сшитых ядрах

АРУ содержал шесть модулей памяти на многократно прошитых ядрах, каждый из которых хранил всего 6 килослов информации (около 12 КБ).Модули памяти немного напоминали картриджи ПЗУ для видеоигр и хранили программное обеспечение в постоянной, но стираемой форме.

Программы записывались путем вплетения проводов в магнитные сердечники.

Провод, проходящий через сердечник, представлял бит 1, а провод, идущий в обход, представлял бит 0. Проплетая 192 провода через сердечник или вокруг него, можно было хранить 192 бита, что давало гораздо более высокую плотность, чем перезаписываемая память на магнитных сердечниках, которая хранила один бит на ядро.

Память на нескольких сшитых ядрах (Блок I) с АРУ

Производство такой памяти было кропотливым процессом, занимавшим 8 недель и стоившим 15 000 долларов за модуль.

Опытные женщины продевали провода вручную, прошивая жилы одну за другой полой иглой, через которую продевалась проволока (на фото ниже).

Им помогала автоматическая система, которая считывала программу с перфоленты и помещала отверстие над основным массивом.

Ткач продевал иглу в отверстие, протягивая проволоку там, где это было необходимо.

После этого память монтировалась на модуль вместе с сотнями резисторов и диодов и заливалась эпоксидной смолой для надежности в полете.

Женщина прошивает постоянную память, добавляя в нее программу

Симулятор памяти на нескольких прошитых ядрах

Процесс перепрошивки памяти требовал серьезных затрат времени и средств, поэтому при тестировании и разработке требовалась альтернатива.Вместо проводных ядер НАСА использовало симуляторы ядра, которые позволяли AGC загружать данные из внешней системы.

Наш АРУ использовался для наземных испытаний, поэтому у него были не прошитые сердечники, а имитатор сердечника.

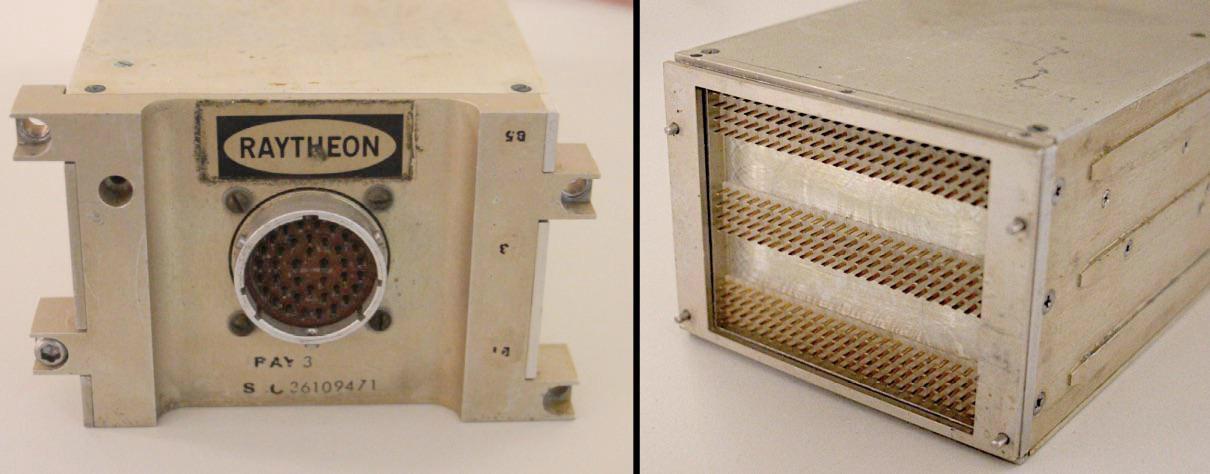

Он состоит из двух коробок, соединенных разъемами для прошитых ядер, причем каждая коробочка занимает три слота памяти.

Их можно увидеть на левой стороне AGC на фотографии ниже.

Они имеют круглые разъемы в стиле милитари для подключения к внешнему компьютеру.

Ящики-симуляторы установлены с левой стороны АРУ вместо реальных модулей памяти.

И хотя у нас есть подробная документация по АРУ, документации по симулятору мне не удалось найти.

Пришлось применить инженерный анализ, проследить все схемы и понять, что делают коробки.

Внешнее изучение их мало что дает. На одной стороне каждой коробки имеется разъем MIL-Spec для подключения к внешней системе.

С другой стороны есть три группы по 96 контактов, подключающихся к АРУ.

Каждая группа контактов занимает место одного модуля памяти на ядрах.

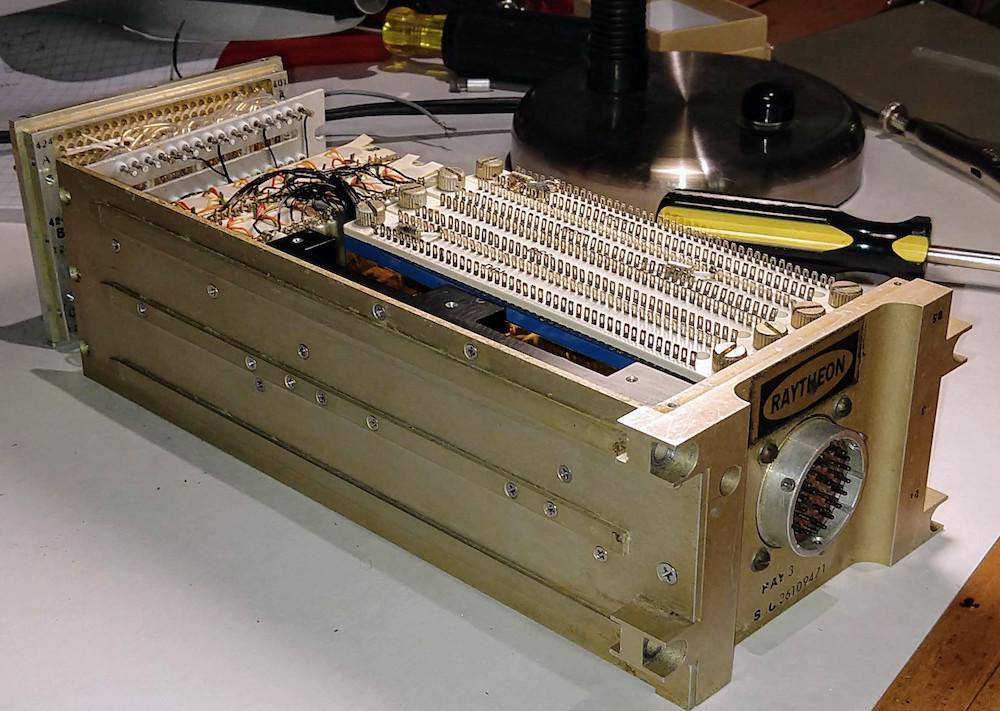

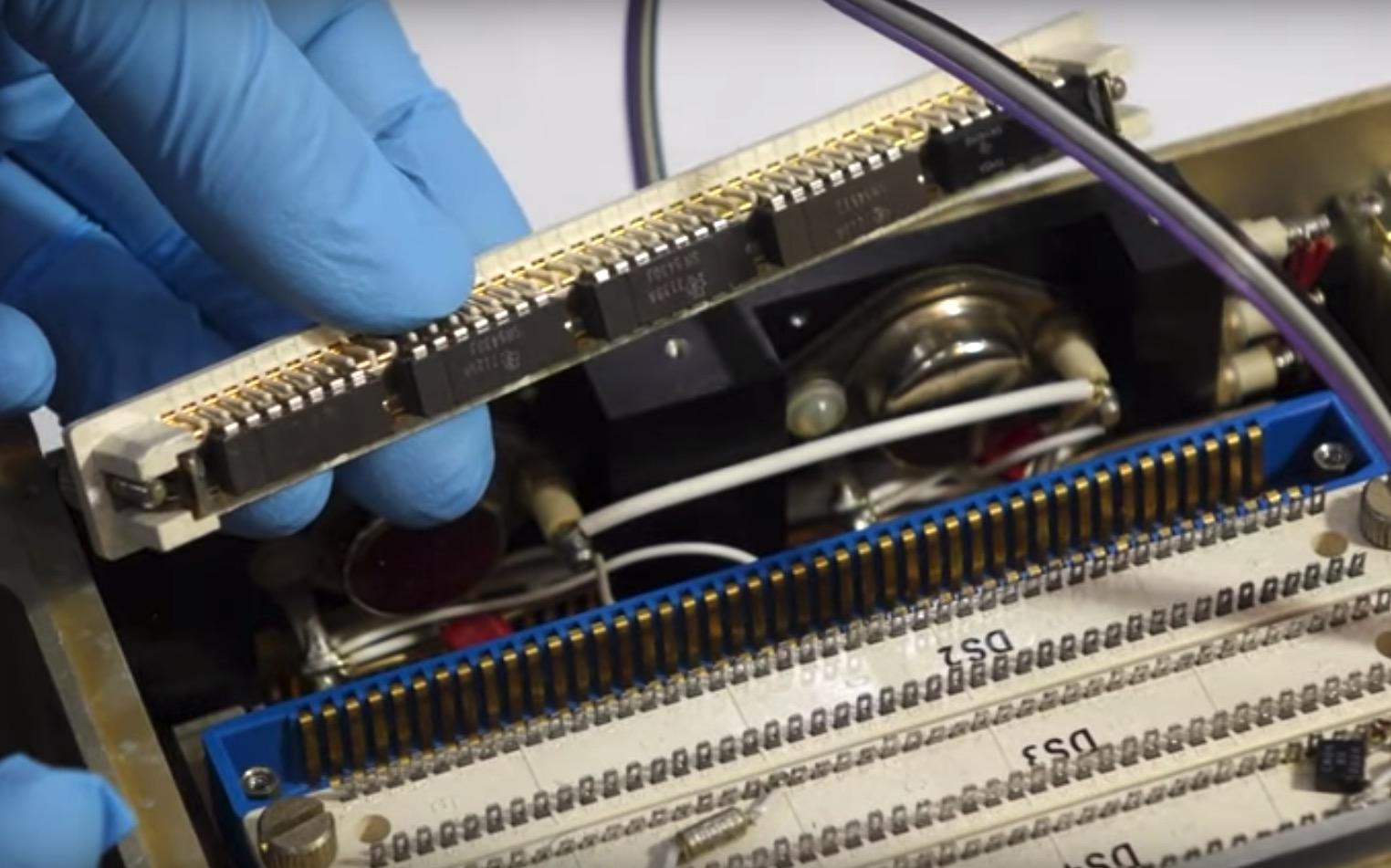

Вскрытие коробок выявило нестандартную технологию сборки.

Частично в схемах использован метод, конструктивно аналогичный кордвуд – компоненты крепились вертикально с помощью отверстий в металлическом блоке.

С обеих сторон колодки к проводам были припаяны контакты.

В остальных схемах в коробках использовались стандартные интегральные схемы (TTL 7400).

Но в отличие от современных печатных плат, чипы монтировались внутри пластиковых модулей, называемых «щупами» [ Dipstik, английский — щуп ] и были смотаны вместе проводами.

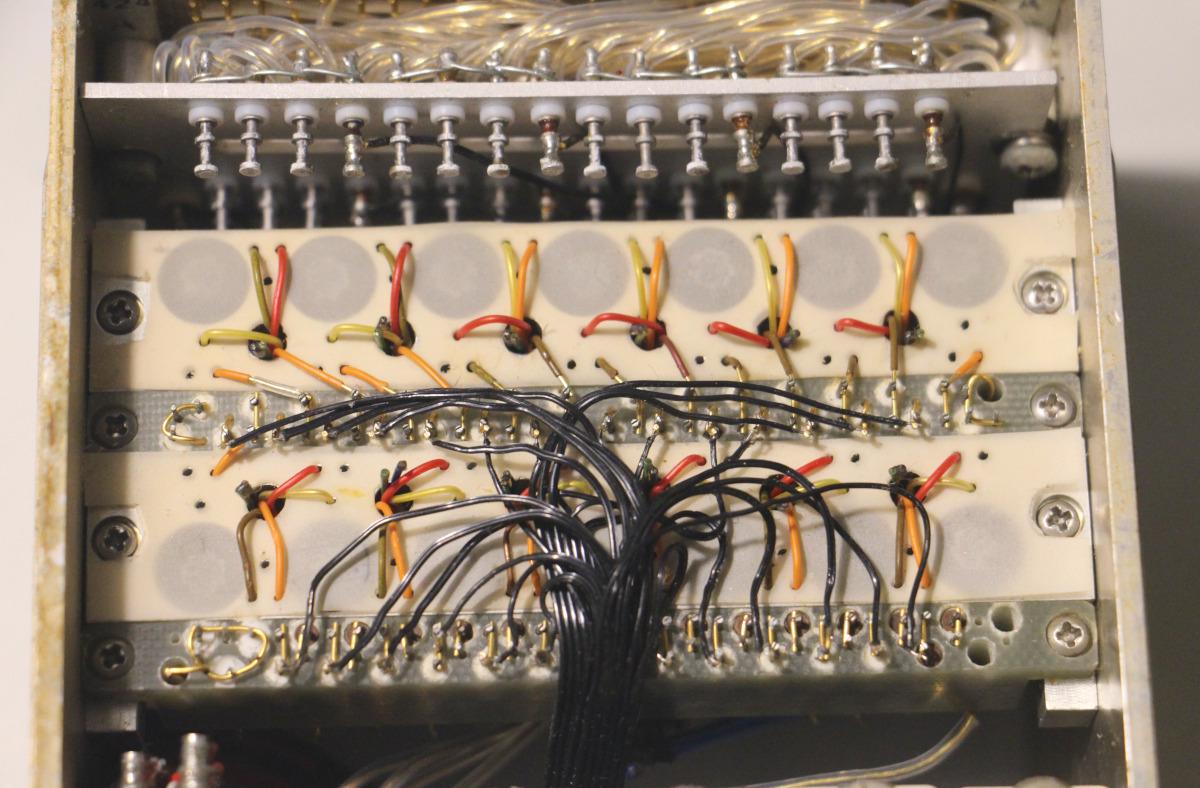

Планировка Кордвуд

Компоновка кордвуда активно использовалась в АРУ для создания аналоговых схем, а также она присутствует в имитаторах памяти (см.фото ниже).

Белые кружки в центре — это концы резисторов и диодов, установленных в модуле вертикально, с припаянными с обеих сторон контактами.

Компоненты плотно упакованы, как бревна, поэтому такую компоновку называют дровяной.

Импульсные трансформаторы расположены под большими серыми кружками.

Подобные есть и на другой стороне модуля, у них из отверстий выходят оранжевые, желтые, красные и коричневые провода.

Черные провода соединяют схему кордвуда с цифровой логикой.

Вверху фотографии вы можете видеть колышки, на которых крепятся диоды и резисторы, а также подключение к выводам, которые подключаются к АРУ.

Основная цель схемы из кордвуда — обеспечить электрическую изоляцию между схемой АРУ и блоками имитатора памяти.

В современных схемах эту функцию выполняют оптоизоляторы, но в симуляторах вместо них используются небольшие импульсные трансформаторы.

Поскольку каждый блок получает сигналы, предназначенные для трех разных модулей памяти, многие диоды объединяют три сигнала в один.

Резисторы контролируют ток, проходящий через импульсные трансформаторы.

Было сложно понять структуру аналоговых цепей кордвуда.

Во-первых, компоненты не видны, поскольку они интегрированы в модуль.

Мне пришлось использовать мультиметр, чтобы выяснить, где они находятся.

Во-вторых, поскольку в макете из кордвуда штифты торчат с обеих сторон, я потратил много времени, переворачивая коробку, чтобы найти нужные мне штифты.

Наконец, я не смог найти удобный способ нарисовать схему компоновки кордвуда, которая не создавала бы лабиринта линий.

Цифровая логика и дипстик

Dipstik — это сменный модуль, представленный в 1968 году для облегчения прототипирования интегральных схем.Он заменил печатные платы на систему упаковки, которая давала вдвое большую плотность.

Идея заключалась в пластиковой колодке разъемов с подключенными внизу контактами для подключения схемы.хм, система дипстиков для установки микросхем.

я думаю @kenshirriff видел это раньше.

думаю, это был модуль разработки для компьютера наведения Аполлона.

pic.x.com/ewYyXY1voz — Время трубки (@TubeTimeUS) 19 марта 2019 г.

Интегральные схемы монтировались на держателе, вставленном в колодку разъемов.

Сверху на держателе имелись выступы под пайку для установки дополнительных компонентов, например, развязывающих конденсаторов.

На фото ниже показаны модули щупов со снятым одним держателем.

У каждого держателя было по 5 микросхем.

Выводы микросхемы были размещены между выводами держателя и выводами блока разъемов.

Эта идея казалась хорошей, но в итоге оказалась ненадежной.

Deepstick оказался провальным проектом.

На фото ниже показаны контакты, соединенные путем намотки проводов снизу щупов.

Мне было чрезвычайно трудно за ними следить; невозможно было проследить за каждым проводом в море одинаковых синих проводов.

Пришлось все проверять мультиметром.

Тогда я смог нарисовать принципиальную схему и подумать, что она делает. Всего в симуляторе было использовано около 50 ИС.

Судя по маркировке компонентов, коробки симулятора были собраны в 1971 году.

Хотя с момента создания АРУ прошло всего несколько лет, технологии в симуляторах уже кажутся более совершенными, что иллюстрирует быстрый прогресс ИС от середины -1960-е – начало 1970-х годов.

АРУ был собран с использованием простых интегральных схем, каждая из которых содержала два вентиля ИЛИ-НЕ и включала примитивную резисторно-транзисторную логику (RTL).

Коробки симулятора содержат более сложные микросхемы серии 7400, содержащие более десяти элементов транзисторно-транзисторной логики (ТТЛ).

В отличие от устаревших плоских микросхем в AGC, в блоках симулятора используются микросхемы в корпусе DIP (двухрядный корпус), и такие корпуса используются до сих пор.

Результаты инженерного анализа

Обрисовав все контуры, я понял, как работает тренажер, и нарисовал.схема .

По сути, один ящик расшифровывает адрес, с которого осуществляется доступ, а второй отправляет необходимые данные в АРУ (буду называть их «ящиком адреса» и «ящиком данных»).

Адресный ящик принимает сигналы и преобразует их в двоичную форму.

Задача непростая, так как сигналы поступают в виде мощных импульсов тока и напряжения 14 В, которые предназначены для переключения ядер.

Также эти импульсы разделены во времени, так как одни переключают ядро в одну сторону, а другие обратно.

Наконец, посылаемые ядрам импульсы содержат не только адрес, но и сигнал о выборе одного из 6 модулей и о выборе одного из 12 потоков в модуле.

В адресном блоке используются импульсные преобразователи, преобразующие импульсы 14 В в сигналы TTL. Там есть куча логики И-ИЛИ для преобразования сигналов в двоичные адреса (что нетривиально, поскольку каждый модуль содержит 6 килослов, это не степень двойки, поэтому требуется много манипуляций с битами).

Триггер блокирует адрес, когда он доступен.

Наконец, схема RC-мультивибратор управляет синхронизацией, определяя на основе различных сигналов, готов ли адрес и когда отправлять результат в АРУ.

Окно данных проще.

Он получает 16 бит данных от внешней системы и отправляет сигналы на усилители АРУ, имитируя милливольтовые сигналы от ядра.

Эти сигналы генерируются импульсными преобразователями.

Адресный ящик и ящик данных обмениваются данными через провода объединительной платы AGC. Коробки обмениваются данными с внешней системой с помощью дифференциальных сигналов для устранения помех от длинных кабелей.

В коробках находятся стабилизаторы LM109 на 5 В, питающие ТТЛ.

Один блок получает нерегулируемый постоянный ток через внешний разъем и отправляет нерегулируемый постоянный ток в другой через объединительную плату АРУ (что для меня немного странно).

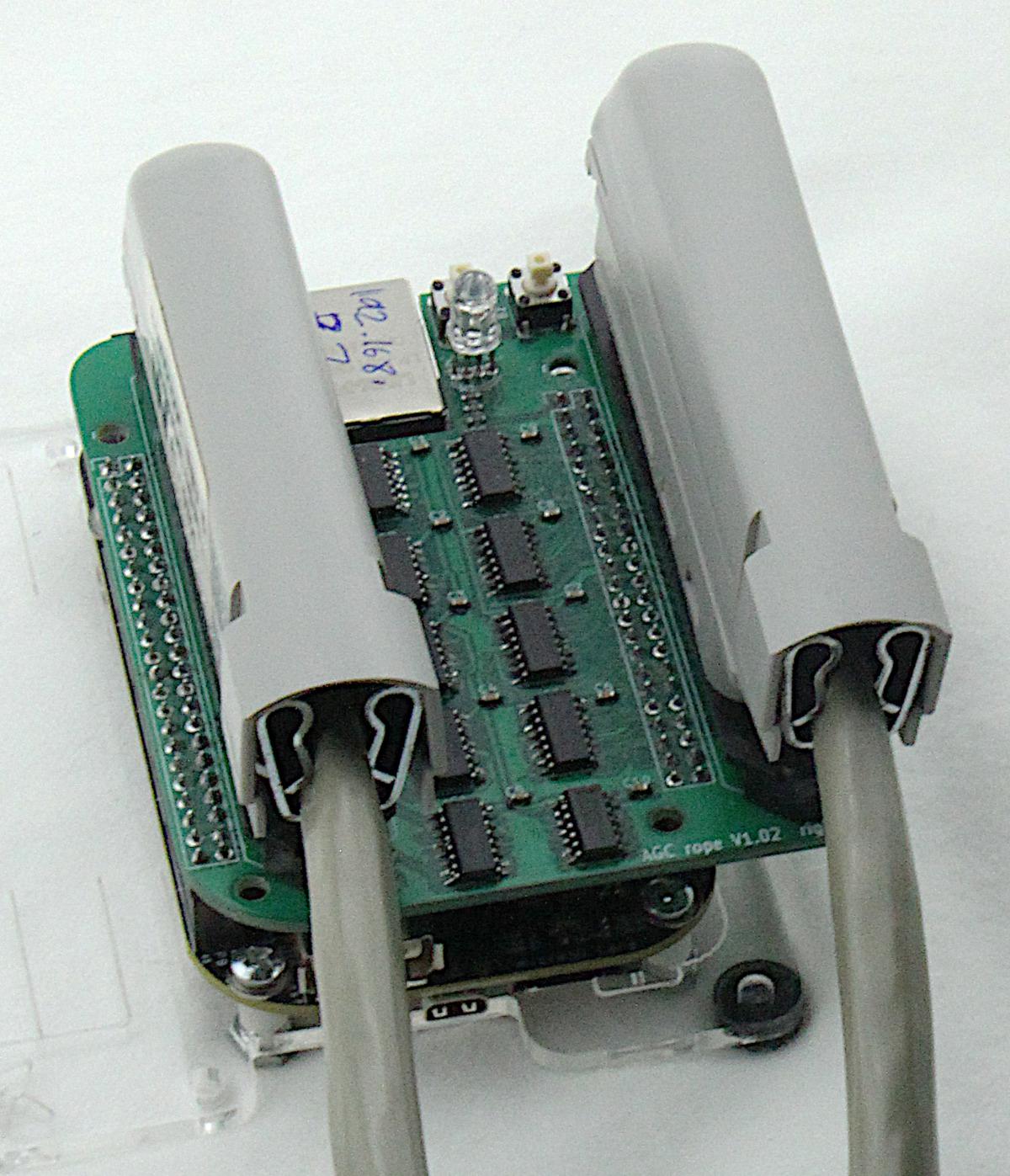

BeagleBone как интерфейс

Поняв работу симулятора, следующим шагом было создание интерфейса, способного выводить данные из программы в симулятор.я использовал БигльКость , крошечный одноплатный компьютер на базе Linux. Преимущество BeagleBone в том, что он имеет быстрые микроконтроллеры, способные в реальном времени реагировать на запросы памяти от АРУ.

Интерфейс представляет собой плату, подключенную к BeagleBone. Каждый из двух кабелей идет в отдельный блок симулятора.

Я разработал интерфейсную плату для подключения к BeagleBone. Все очень просто: дифференциальные линейные приемники.

AM26C32 , преобразование дифференциальных сигналов симулятора в логические сигналы 3,3 В для BeagleBone и драйверы дифференциальных линий.

AM26C31 для отправки сигналов на симулятор.

Я спроектировал плату в KiCad и заказал изготовление у PCBWay , спонсор восстановления AGC. Я написал программу, работающую на микроконтроллере BeagleBone PRU. По сути, это конечный автомат, который ожидает адреса от блока симулятора, ожидает сигнала синхронизации, считывает слово из оперативной памяти BeagleBone и отправляет это слово в симулятор.

Я выложил программу на Гитхаб .

Проблемы с симулятором

Имитаторы памяти на нескольких ядрах не были собраны по стандартам бортовой управляющей машины «Аполлон», и в результате мне пришлось потратить много времени на их отладку.Многие соединения были разорваны и их пришлось паять заново (не знаю, сломались ли они от времени, или когда я разобрался со схемой работы).

Мы также обнаружили короткое замыкание в одном щупе и неисправную микросхему.

Больше всего проблем было со щупами, так как многие контакты чередовались между щупами и ИС.

Проблема заключалась в том, что контакты микросхемы оказались зажаты между контактами держателя щупа и колодкой, в которую они были вставлены.

Пластиковые щупы выгибаются наружу, из-за чего контакты периодически выходят из строя.

Изогнув ножки микросхемы в форме буквы S, Марк смог обеспечить их контакт с обеих сторон, по крайней мере, на некоторое время.

Но через несколько часов мягкие ножки ИМС прогнулись, контакты снова стали плохо работать, поэтому долгосрочного решения этой проблемы у нас не было.

Самой интересной проблемой была гонка двух сигналов от AGC, действие которых должно было быть прекращено одновременно.

Они питали оба конца катушки импульсного преобразователя, который не должен был выдавать сигнал.

Однако один сигнал отставал от другого, что приводило к появлению ложного импульса.

К сожалению, цифровая логика в блоке симулятора была асинхронной, этот импульс блокировал неправильный бит адреса в триггерах, что приводило к доступу к неправильной ячейке памяти.

В результате мы отследили эту проблему и установили дополнительные конденсаторы фильтрации импульсов.

К сожалению, мы использовали слишком большие конденсаторы и в других случаях сигнал слишком сильно задерживался, что приводило к другим ошибкам.

Затем мы установили конденсаторы меньшего размера и, наконец, смогли успешно запускать программы на АРУ, используя старинные симуляторы основной памяти.

Заключение

Бортовой управляющий компьютер «Аполлона» использует многоядерную память.Поскольку постоянно перепроектировать такую память в ходе разработки было непрактично, вместо нее использовались симуляторы.

Я перепроектировал симулятор и создал интерфейс для его запуска с помощью BeagleBone. Мы успешно запускали программы на AGC через этот интерфейс.

Однако симулятор памяти оказался проблематичным и ненадежным.

@CuriousMarc снял видео с подробным описанием нашей работы с симулятором памяти: Теги: #Космонавтика #История ИТ #Накопители #Apollo #Apollo #Beaglebone #память на ядрах

-

Ice Bucket Challenge От Хабрахабра

19 Oct, 24 -

Как Раскрутить Новичка, Ничего Не Сломав

19 Oct, 24 -

В Розыске! Старые Хиты Эрика Липперта

19 Oct, 24 -

Пропеллеры… Рекорд!!!

19 Oct, 24