Приоритеты современной военной авиации ориентированы на качественную ситуационную осведомленность, поэтому современный истребитель представляет собой летающий рой высокотехнологичных датчиков.

Сбор информации от этих датчиков, ее обработка и представление пользователю осуществляется бортовой микропроцессорной системой (МПС).

Вчера для его реализации были использованы гибриды HPEC (включая CPU, GPU и FPGA).

Сегодня для ее реализации используются однокристальные системы SoC, которые помимо сборки всех компонентов на одном чипсете еще и организуют внутрикристальную сеть (NoC) как альтернативу традиционной магистральной сети передачи данных.

Завтра, когда системы SoC станут еще более зрелыми, ожидается приход полиморфной наноэлектроники, которая обеспечит значительный рост производительности и снизит скорость устаревания.

Введение

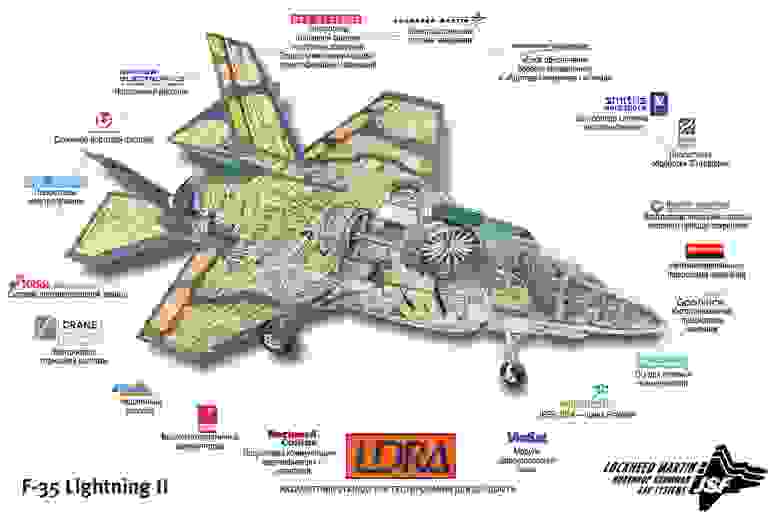

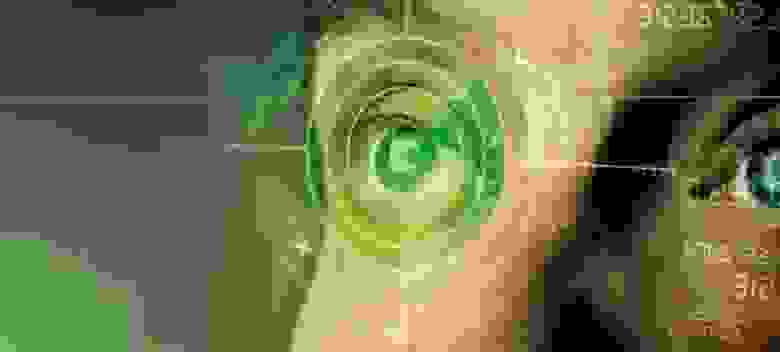

Если в эпоху истребителей 4-го поколения показателями боевого превосходства были высокая скорость и экономное энергопотребление, то в эпоху истребителей 5-го поколения боевое превосходство измеряется прежде всего качеством ситуационной осведомленности.[6] Таким образом, современный истребитель представляет собой летающий рой всевозможных высокотехнологичных датчиков, обеспечивающих в общей сложности «360-градусную осведомленность об обстановке».

[5] Сбор информации с этих датчиков, ее обработка и представление в понятном для пилота виде требует огромных вычислительных мощностей.

Все эти расчеты необходимо производить на борту, поскольку суммарная интенсивность входного потока данных от всего роя датчиков (видеокамер, радаров, ультрафиолетовых и инфракрасных датчиков, лидара, гидролокатора и т.д.) превышает пропускную способность внешних высокоскоростной каналы связи не менее 1000 раз.

[2] Бортовая обработка сигналов привлекательна еще и тем, что предоставляет пилоту актуальную информацию в режиме реального времени.

Под «понятностью изложения» подразумевается, что вся информация — какой бы разнородной она ни была — должна быть синтезирована в единую «театральную картину боевых действий», [9] интерпретация которой не должна превращаться в загадочную аналитическую задачу ( как это было на старых моделях истребителей, где пилоту приходилось одновременно следить за десятками дисплеев).

Высокопроизводительная интегрированная система

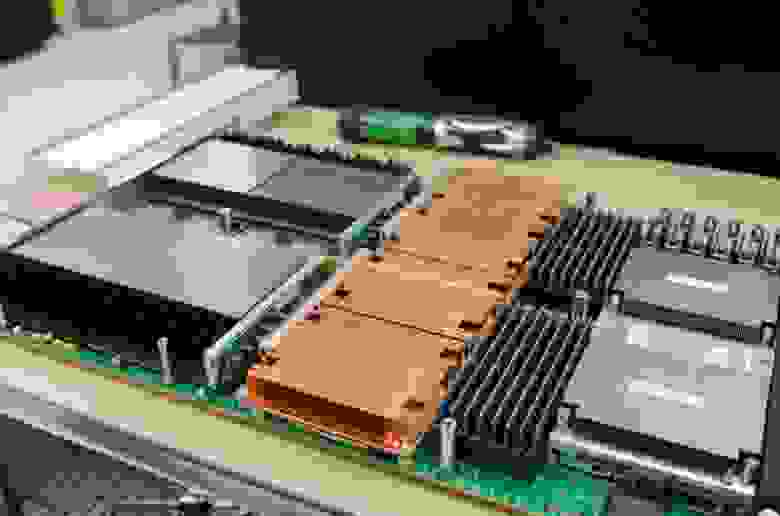

Ответственность за эту театральную постановку, или, более формально, ответственность за решение этой сложной и трудной задачи, лежит на бортовой МПС, которая, помимо высоких характеристик, должна обеспечивать еще и достаточно низкий уровень SWaP (габаритов, массы и мощности).потребления), что само по себе является «вечнозеленой проблемой»» [8] Сегодня популярным (но не самым продвинутым) решением в этом плане является использование трех многопрофильных процессоров, размещенных в одном корпусе: CPU, GPU и FPGA. Устоявшееся название такого гибрида — HPEC (High Performance Integrated System) [2].

Залогом его успешной реализации является продуманная архитектура MPS, которая берет лучшие характеристики от каждого процессора и обходит их слабые стороны.

При этом целью архитектуры HPEC является достижение эффекта синергии — когда производительность конечной гибридной системы существенно превышает суммарную производительность ее составных частей.

Гибридная архитектура объединяет в одном корпусе несколько процессоров разных типов.

Идея состоит в том, что если вы воспользуетесь сильными сторонами каждого отдельного компонента, вы сможете создать передовую систему HPEC, сочетающую в себе потрясающую производительность, а их детище — детский SWaP. [10] Рассмотрим подробнее каждый из трех компонентов архитектуры HPEC.

Пример гибрида HPEC Врезка: Живой пример гибрида HPEC В качестве живой иллюстрации гибрида HPEC можно привести портативную камеру AdLink NEON-1040 x86 (4 Мп, 60 кадров в секунду), рассчитанную на суровые условия эксплуатации.

Он оснащен FPGA и графическим процессором, обеспечивающими передовые технологии обработки изображений, а также четырехъядерным процессором (Intel Atom, 1,9 ГГц), благодаря которому алгоритмы обработки могут быть реализованы в виде x86-совместимых программ.

Кроме того, камера имеет на борту 32 ГБ дискового пространства, где можно хранить видео, программы и архивные данные.

[13]

Камера AdLink Преимущество FPGA в том, что алгоритмы реализуются аппаратно, а такая реализация, как известно, всегда быстрее.

Кроме того, работая на относительно низких тактовых частотах порядка сотен МГц, FPGA могут выполнять десятки тысяч вычислений за такт и потреблять гораздо меньше энергии, чем графические процессоры.

Также сложно конкурировать с FPGA по времени отклика (сотни наносекунд — против десятков микросекунд, которые может обеспечить GPU).

Также стоит отметить, что современные ПЛИС имеют возможность динамической переконфигурации: их можно перепрограммировать на лету (без перезагрузки и остановки) для адаптации алгоритмов к изменяющимся условиям эксплуатации.

Поэтому FPGA (например, Xilinx) хороша для первичной обработки данных, поступающих с датчиков.

Он фильтрует необработанную информацию, поступающую от датчиков, и передает более сжатый полезный поток.

FPGA здесь незаменима, поскольку однородный поток данных, обработку которого к тому же легко распараллелить, — это именно та задача, где FPGA является лидером жанра.

Боковая панель: Проектирование DSP на FPGA Традиционно FPGA программируются на языке низкого уровня VHDL. Однако Xilinx удалось интегрировать процесс разработки с такой мощной инструментальной средой, как MathWorks Simulink. Одной из приятных особенностей Simulink является его интеграция с MatLab, который, в свою очередь, является самым популярным инструментом моделирования алгоритмов для военной и коммерческой обработки сигналов; Что касается проектирования компонентов DSP, MatLab вообще является стандартом де-факто.

Такая интеграция позволяет разработчику использовать программные коды и утилиты, разработанные в MatLab. Что, в свою очередь, облегчает и ускоряет цикл проектирования.

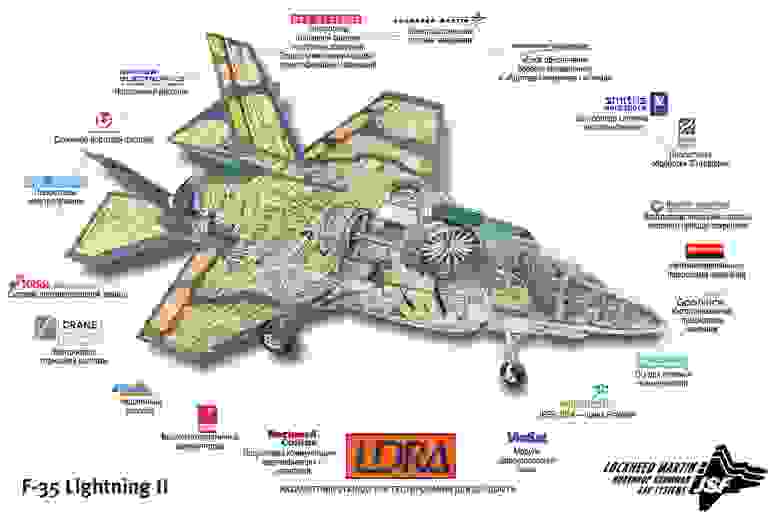

Тем более, что основная часть тестирования итоговой системы перенесена в среду MatLab, где это делать гораздо удобнее, чем при работе с традиционными инструментами FPGA. [1] ПЛИС В настоящее время они являются ядром наиболее ответственных подсистем бортовой МПС военной авиации: бортовой управляющей вычислительной машины, системы навигации, дисплеев в кабинах, систем торможения, регуляторов температуры и давления в кабине, приборов освещения, двигателя самолета.

блоки управления.

[14] FPGA также являются основой сетевых коммуникаций авионики, электрооптических систем наведения и других типов вычислительно-интенсивных вычислений для «интегрированных модулей авионики» (IMA) на борту объединенного ударного истребителя (JSF), такого как F-35. .

[5] графический процессор (например, Nvidia Tesla) — хорош для параллельной обработки алгоритмов с интенсивной математикой и плавающей запятой.

Он делает это лучше, чем FPGA и CPU. Массивная параллельная конструкция графического процессора, состоящего из нескольких сотен ядер, позволяет ему обрабатывать параллельные алгоритмы намного быстрее, чем центральный процессор.

FPGA, конечно, также хороша для параллельной обработки, но не для операций с плавающей запятой.

Сама FPGA их делать не может, тогда как современный GPU обеспечивает триллион операций с плавающей запятой в секунду — что, например, очень полезно для таких задач, как сшивка нескольких гигапиксельных видеопотоков.

Многоядерный процессор (например, Intel Core i7) – хорош для когнитивной обработки.

Итак, взяв лучшие характеристики всех процессоров и обойдя их слабые стороны, можно добиться необычайной вычислительной мощности.

Кроме того, в HPEC можно включить другие выделенные процессоры для достижения еще большей производительности.

Например, для решения задач бортовой навигационной системы может быть использован ППУ (Physics Processing Unit) – аппаратный ускоритель физических расчетов, оптимизированный для работы с динамикой твердых, жидких и мягких тел, для обнаружения столкновений.

, для анализа методом конечных элементов, для анализа неисправностей объектов и т. д. [11] Другими примерами специализированных процессоров являются аппаратный ускоритель обработки радиолокационных сигналов [1] и аппаратный ускоритель графового анализа, [12] которые будут незаменимы при обработке « большие данные".

В обозримом будущем за счет удешевления аппаратных средств и упрощения процесса их разработки ожидается появление самых разнообразных аппаратных ускорителей, которые пополнят «периодическую систему вычислений первичных элементов» [10].

] благодаря чему алхимический процесс инженерного проектирования станет еще более эффективным.

Боковая панель: HPEC на одном чипсете Разработчики высокопроизводительных военных компонентов (HPEC) часто используют дуэт топового процессора Intel и ПЛИС Altera. Отвечая на потребности разработчиков, Intel Сегодня интегрирует модули FPGA от Altera (которая недавно стала частью Intel) в свои топовые процессоры.

Завтра Intel планирует предоставить разработчикам возможность настраивать процессоры с использованием собственных компонентов ASIC, для чего она сотрудничает с корпорацией eASIC. [4] Интерес к компонентам ASIC обусловлен тем, что какими бы быстрыми и энергоэффективными ни были компоненты FPGA, поставщики ASIC обещают удвоение производительности при 80-процентном снижении энергопотребления.

[3]

Сжатие MPS на один чипсет

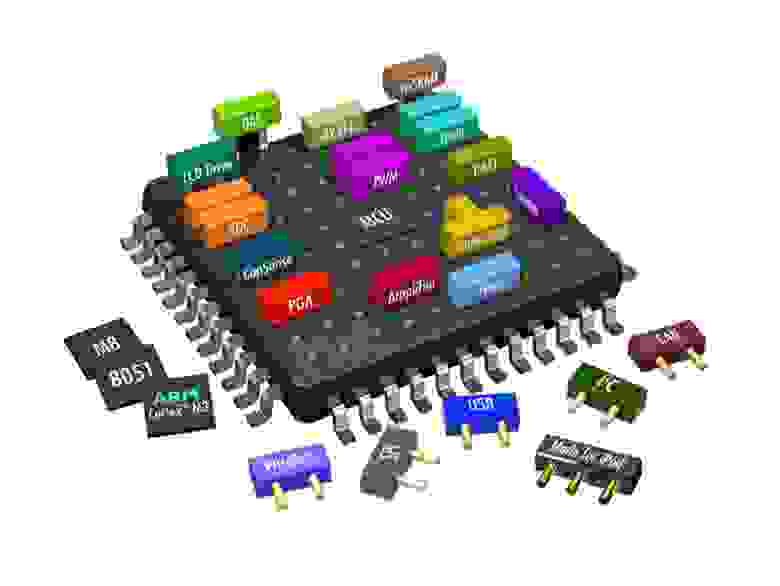

Итак, мы рассмотрели архитектуру HPEC, которая способна обеспечить высокую производительность при достаточно низком уровне SWaP. Однако в этом отношении существует более продвинутое решение: концепция SoC, суть которой заключается в разместить всю микропроцессорную систему на одном чипсете .SoC сочетает в себе программируемость процессора с возможностью настройки оборудования FPGA, обеспечивая непревзойденный уровень производительности, гибкости и масштабируемости системы.

Значительный сдвиг в этом отношении в сторону программной составляющей позволяет создавать многофункциональные системы со всевозрастающими возможностями и все уменьшающимися размерами и стоимостью.

Использование перепрограммируемых компонентов также позволяет осуществлять более дешевые и быстрые обновления устаревших систем — без необходимости обновлять аппаратное обеспечение при каждом постепенном улучшении их архитектуры, что особенно актуально для военной промышленности.

Типичная система SoC включает в себя:

- микроконтроллер, многоядерный процессор или ядро DSP;

- блоки памяти, на выбор: ПЗУ, ОЗУ, EEPROM и флэш-память;

- таймеры, включая генераторы и системы фазовой автоподстройки частоты;

- периферийные устройства, в том числе счетчики-таймеры, таймеры реального времени, генераторы включения и сброса;

- внешние интерфейсы, в том числе общепринятые: USB, FireWire, Ethernet, USART и SPI;

- аналоговые интерфейсы, включая блоки ЦАП и АЦП;

- регуляторы напряжения и схемы управления питанием;

- шины данных, по которым все вышеперечисленные блоки обмениваются информацией;

- Контроллеры DMA, расположенные между внешними интерфейсами и памятью, позволяют обмениваться данными в обход ядра процессора, тем самым увеличивая пропускную способность SoC.

Эта концепция предлагает отказаться от традиционных шин данных и заменить их внутрикристальной сетью .

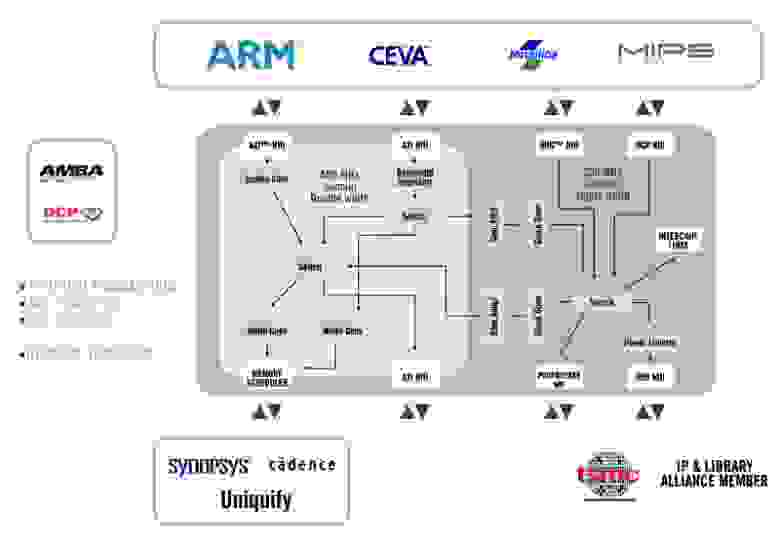

Например, Arteris Inc использует концепцию NoC для управления внутрикристальным трафиком и обменом управляющими сигналами, что приводит к значительному увеличению пропускной способности.

[7]

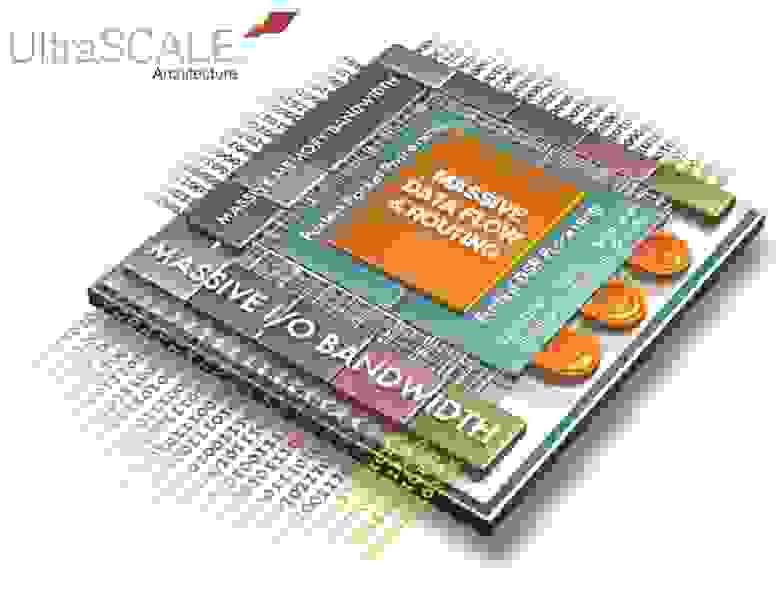

Системная архитектура SoC от Arteris Inc. Боковая панель: живой пример системы SoC. Одним из живых примеров системы SoC является Zynq Ultrascale+ MPSoC от Xilinx. Это настоящая SoC, разработанная по принципу «все включено».

На борту имеются: 1) программируемая логика, 2) 64-битная четырехъядерная процессорная система ARM A53, 3) память, 4) функции безопасности, 5) четыре гигабитных приемника.

И все это на одном чипсете! Архитектура SoC обещает конечному пользователю множество преимуществ: гораздо более высокую производительность, более быструю разработку и время вывода на рынок, а также возможность использовать многолетний опыт разработки программных алгоритмических решений при проектировании аппаратных компонентов.

[7]

Xilinx Zynq Ultrascale+ MPSoC

Заключение

Подводя итог обзора высокопроизводительных систем в целом и SoC в частности – как наиболее популярного их представителя сегодня – можно сказать, что эволюция малого форм-фактора встраиваемых вычислительных систем произошла столь быстро, и ее влияние на архитектуру Возможности системы настолько обширны, что инженерам-конструкторам могут потребоваться годы, чтобы интегрировать эту передовую однокристальную концепцию в свои решения.Кроме того, поскольку усилия по разработке SoC в основном направлены на то, чтобы как можно медленнее устаревать оборудование, они имеют тенденцию становиться более перепрограммируемыми.

Поэтому есть основания предполагать, что наноэлектроника завтрашнего дня будет иметь возможность полной пользовательской настройки, в результате чего граница между аппаратным и программным обеспечением будет полностью стерта.

[7] По сути, такое событие ознаменует начало новой эры – полиморфной наноэлектроники, которая будет сочетать в себе такие противоречивые характеристики, как гибкость программного уровня и высокую производительность аппаратного ускорения.

Это позволит разработчикам взять от существующих программных и аппаратных архитектур только лучшие характеристики и не только игнорировать их слабые стороны (как это делается при проектировании архитектуры HPEC), но и в принципе не включать их в окончательный проект устройства.

При этом вероятность достижения синергетического эффекта (о котором говорилось при обсуждении архитектуры HPEC) существенно возрастает. Что, несомненно, сыграет ключевую роль в повышении качества ситуационной осведомленности, которая, как было сказано в начале статьи, является сегодня залогом борьбы с превосходством.

Не только в воздушном пространстве, но и на всем остальном «театре боевых действий».

Библиография

- Дэвид Лис.

Быстрое прототипирование обработки радиолокационных сигналов // Передовые технологии: Датчики.7(2), 2012. С.

76-79.

- Кортни ?.

Ховард.

HPEC обеспечивает обработку данных на борту для постоянного наблюдения // Военная и аэрокосмическая электроника: Высокопроизводительные встроенные вычисления.27(7), 2016. С.

16–21.

- Путь миграции ASIC на основе ячеек .

- Джон Келлер.

Intel увеличит предложение интегрированных микропроцессоров и FPGA с приобретением Altera . - Кортни ?.

Ховард.

Обработка видео и изображений на переднем крае // Военная и аэрокосмическая электроника: Прогрессивная авионика.22(8), 2011.

- Стефани Энн Фрайоли.

Разведывательное обеспечение F-35A Lightning II // Air & Space Power Journal. 30(2), 2016. С.106-109.

- Дж.

Р.

Уилсон.

Сжатие плат в системы на кристалле // Военная и аэрокосмическая электроника: Руководство покупателя.27(3), 2016. С.

19–25.

- Кортни Ховард. Данные, востребованные: ответ на вызов связи // Военная и аэрокосмическая электроника: Носимая электроника.

27(9), 2016.

- Прелипчан Г.

, Боскояну М.

, Моисеску Ф.

Новые идеи поддержки искусственного интеллекта в военных приложениях, в журнале «Последние достижения в области искусственного интеллекта, инженерии знаний и баз данных», AIKED’10, 2010. 10. Джон Келлер.

Гибридные процессорные архитектуры отвечают требованиям SWaP // Военная и аэрокосмическая электроника: модернизация авионики.26(2), 2015. С.

18–24.

- ASUS PhysX P1 (на базе PPU Ageia PhysX) .

- Объявление широкого агентства: Иерархическая идентификация, проверка эксплойтов (HIVE) Microsystems Technology Office DARPA-BAA-16-52, 10 августа 2016 г.

- Прочная интеллектуальная камера для промышленных условий, представленная ADLINK // Военная и аэрокосмическая электроника: высокопроизводительные встроенные вычисления.

27(7), 2016. с.

27.

- Кортни Ховард. Авионика: на шаг впереди // Военная и аэрокосмическая электроника: Инновации в авионике.

24(6), 2013. С.

10–17.

Эта статья была первоначально опубликована в «Компоненты и технологии» .

Теги: #Высокая производительность #Большие данные #Визуализация данных #soc #GPGPU #FPGA #noc #mps #swap #F-35 #HPEC

-

Как Написать (Игрушку) Jvm

19 Oct, 24 -

Венчурный Сервис Знакомств

19 Oct, 24 -

Новая Страница Профиля В Живом Журнале.

19 Oct, 24 -

Киберпанк Комната/Квартира

19 Oct, 24 -

Iphone Nano Выйдет Весной?

19 Oct, 24 -

Создание Модуля Для Drupal 7. Часть 2

19 Oct, 24