В данной статье рассмотрены основные вопросы, касающиеся принципа работы различных типов АЦП.

При этом некоторые важные теоретические выкладки, касающиеся математического описания аналого-цифрового преобразования, остались за рамками статьи, но приводятся ссылки, где заинтересованный читатель сможет найти более глубокое рассмотрение теоретических аспектов преобразования.

работа АЦП.

Таким образом, статья больше посвящена пониманию общих принципов работы АЦП, чем теоретическому анализу их работы.

" Введение

В качестве отправной точки давайте определим аналого-цифровое преобразование.

Аналого-цифровое преобразование — это процесс преобразования входной физической величины в ее числовое представление.

Аналого-цифровой преобразователь — это устройство, выполняющее такое преобразование.

Формально входной величиной АЦП может быть любая физическая величина - напряжение, ток, сопротивление, емкость, частота следования импульсов, угол поворота вала и т.п.

Однако для определенности в дальнейшем под АЦП будем понимать исключительно напряжение-то -преобразователи кодов.

Понятие аналого-цифрового преобразования тесно связано с понятием измерения.

Под измерением мы понимаем процесс сравнения измеренной величины с каким-либо эталоном; при аналого-цифровом преобразовании входное значение сравнивается с некоторым эталонным значением (обычно эталонным напряжением).

Таким образом, аналого-цифровое преобразование можно рассматривать как измерение величины входного сигнала, и к нему применимы все понятия метрологии, такие как погрешности измерения.

Основные характеристики АЦП АЦП имеет множество характеристик, основными из которых являются частота преобразования и разрядность.

Частота преобразования обычно выражается в выборках в секунду (SPS), а разрядность — в битах.

Современные АЦП могут иметь разрядность до 24 бит и скорость преобразования до единиц GSPS (конечно, не одновременно).

Чем выше скорость и разрядность, тем сложнее получить требуемые характеристики, тем дороже и сложнее преобразователь.

Скорость преобразования и разрядность определенным образом связаны друг с другом, и мы можем увеличить эффективную разрядность преобразования, пожертвовав скоростью.

Типы АЦП Существует множество типов АЦП, но для целей данной статьи мы ограничимся рассмотрением только следующих типов:

- АЦП параллельного преобразования (прямое преобразование, флэш-АЦП)

- АЦП последовательного приближения (АЦП последовательного приближения)

- дельта-сигма АЦП (зарядно-сбалансированный АЦП)

Однако перечисленные выше архитектуры АЦП являются наиболее представительными в силу того, что каждая архитектура занимает определенную нишу в общем скоростно-разрядном диапазоне.

АЦП прямого (параллельного) преобразования имеют наибольшее быстродействие и наименьшую разрядность.

Например, АЦП параллельного преобразования TLC5540 от Texas Instruments имеет скорость 40 MSPS при всего 8 битах.

АЦП этого типа могут иметь скорость преобразования до 1 GSPS. Здесь можно отметить, что конвейерные АЦП имеют еще большее быстродействие, но они представляют собой комбинацию нескольких АЦП с меньшим быстродействием и их рассмотрение выходит за рамки данной статьи.

Среднюю нишу в ряду «скорость-скорость» занимают АЦП последовательного приближения.

Типичные значения — 12–18 бит с частотой преобразования 100KSPS-1MSPS. Наивысшая точность достигается сигма-дельта АЦП с разрядностью до 24 бит включительно и быстродействием от единиц СПС до единиц КСПС.

Другой тип АЦП, нашедший применение в недавнем прошлом, — это интегрирующий АЦП.

Интегрирующие АЦП в настоящее время почти полностью заменены АЦП других типов, но их можно встретить в старых измерительных приборах.

АЦП прямого преобразования АЦП прямого преобразования получили широкое распространение в 1960-х и 1970-х годах, а в 1980-х годах начали производиться в виде интегральных схем.

Они часто используются в составе «конвейерных» АЦП (в данной статье не рассматриваются) и имеют разрядность 6-8 бит при скорости до 1 GSPS. Архитектура АЦП прямого преобразования представлена на рис.

1.

Рис.

1. Структурная схема АЦП прямого преобразования.

Принцип работы АЦП предельно прост: входной сигнал подается одновременно на все «положительные» входы компараторов, а на «отрицательные» подается ряд напряжений, полученных из опорного напряжения путем деления их на резисторы.

Р.

Для схемы рис.

1 этот ряд будет таким: (1/16, 3/16, 5/16, 7/16, 9/16, 11/16, 13/16) Uref, где Uref – опорное напряжение АЦП.

Пусть на вход АЦП подается напряжение, равное 1/2 Uref. Тогда сработают первые 4 компаратора (если считать снизу), и на их выходах появятся логические.

Приоритетный кодер формирует двоичный код из «столбца» единиц, который фиксируется в выходном регистре.

Теперь становятся понятны преимущества и недостатки такого преобразователя.

Все компараторы работают параллельно, время задержки схемы равно времени задержки в одном компараторе плюс время задержки в кодере.

Компаратор и энкодер можно сделать очень быстрыми, в результате вся схема имеет очень высокую производительность.

Но для получения N бит нужны 2^N компараторов (и сложность кодера тоже растет как 2^N).

Схема на рис.

1. содержит 8 компараторов и имеет 3 бита, для получения 8 бит нужно 256 компараторов, для 10 бит - 1024 компаратора, для 24-битного АЦП их потребуется более 16 миллионов.

Однако таких высот технология еще не достигла.

АЦП последовательного приближения АЦП последовательного приближения реализует алгоритм «взвешивания», восходящий к Фибоначчи.

В своей книге «Liber Abaci» (1202) Фибоначчи рассмотрел «проблему выбора наилучшей системы гирь», то есть нахождения такого ряда гирь, который потребовал бы минимального числа взвешиваний на рычажных весах для нахождения веса объект. Решением этой проблемы является «бинарный» набор весов.

Подробнее о задаче Фибоначчи можно прочитать, например, здесь: http://www.goldenmuseum.com/2015AMT_rus.html .

Аналого-цифровой преобразователь регистра последовательного приближения (SAR) измеряет величину входного сигнала путем выполнения серии последовательных «взвешиваний», то есть сравнения значения входного напряжения с рядом значений, формируемых следующим образом: 1. на первом этапе на выходе встроенного цифро-аналогового преобразователя устанавливается значение, равное 1/2Uref (здесь и далее будем считать, что сигнал находится в интервале (0 – Uref).

2. если сигнал больше этой величины, то он сравнивается с напряжением, лежащим в середине оставшегося интервала, т.е.

в данном случае 3/4Uref. Если сигнал меньше установленного уровня, то следующее сравнение будет производиться с менее чем половиной оставшегося интервала (т.е.

с уровнем 1/4Uref).

3. Шаг 2 повторяется N раз.

Таким образом, N сравнений («взвешиваний») дают N бит результата.

Рис.

2. Структурная схема АЦП последовательного приближения.

Таким образом, АЦП последовательного приближения состоит из следующих узлов: 1. Компаратор.

Он сравнивает входное значение и текущее значение «взвешивающего» напряжения (на рис.

2 обозначено треугольником).

2. Цифро-аналоговый преобразователь (ЦАП).

Он формирует «вес» напряжения на основе цифрового кода, полученного на входе.

3. Регистр последовательного приближения (SAR).

Он реализует алгоритм последовательного приближения, генерирующий текущее значение кода, подаваемого на вход ЦАП.

В его честь названа вся архитектура АЦП.

4. Схема Sample/Hold (Выборка/Хранение, S/H).

Для работы этого АЦП принципиально важно, чтобы входное напряжение оставалось постоянным на протяжении всего цикла преобразования.

Однако «реальные» сигналы имеют тенденцию меняться со временем.

Схема выборки и хранения «запоминает» текущее значение аналогового сигнала и сохраняет его неизменным на протяжении всего рабочего цикла устройства.

Преимуществом устройства является сравнительно высокая скорость преобразования: время преобразования N-разрядного АЦП составляет N тактов.

Точность преобразования ограничена точностью внутреннего ЦАП и может составлять 16-18 бит (сейчас начали появляться 24-битные АЦП SAR, например, AD7766 и AD7767).

Дельта-сигма АЦП Наконец, наиболее интересным типом АЦП является сигма-дельта АЦП, который в литературе иногда называют АЦП с зарядовой балансировкой.

Структурная схема сигма-дельта АЦП представлена на рис.

3.

Рис.

3. Структурная схема сигма-дельта АЦП.

Принцип работы этого АЦП несколько сложнее, чем у других типов АЦП.

Суть его в том, что входное напряжение сравнивается со значением напряжения, накопленным интегратором.

На вход интегратора в зависимости от результата сравнения подаются импульсы положительной или отрицательной полярности.

Таким образом, данный АЦП представляет собой простую следящую систему: напряжение на выходе интегратора «отслеживает» входное напряжение (рис.

4).

Результатом работы этой схемы является поток нулей и единиц на выходе компаратора, который затем пропускается через цифровой фильтр нижних частот, в результате чего получается N-битный результат. ФНЧ на рис.

3. Совмещен с «дециматором» — устройством, снижающим частоту показаний за счет их «прореживания».

Рис.

4. Сигма-дельта АЦП как система слежения.

Для строгости изложения необходимо сказать, что на рис.

3 представлена структурная схема сигма-дельта АЦП первого порядка.

Сигма-дельта АЦП второго порядка имеет два интегратора и две петли обратной связи, но здесь не будет обсуждаться.

Интересующиеся этой темой могут обратиться к [3].

На рис.

5 показаны сигналы АЦП при нулевом входном уровне (вверху) и на уровне Vref/2 (внизу).

Рис.

5. Сигналы в АЦП при разных уровнях входного сигнала.

Более наглядно работу сигма-дельта АЦП демонстрирует небольшая программа, расположенная здесь: http://designtools.analog.com/dt/sdtutorial/sdtutorial.html. Теперь, не углубляясь в сложный математический анализ, попробуем понять, почему сигма-дельта АЦП имеют очень низкий уровень шума.

Рассмотрим структурную схему сигма-дельта модулятора, представленную на рис.

3, и представим ее в таком виде (рис.

6):

Рис.

6. Структурная схема сигма-дельта модулятора.

Здесь компаратор представлен как сумматор, который складывает непрерывный полезный сигнал и шум квантования.

Пусть интегратор имеет передаточную функцию 1/s. Тогда, представляя полезный сигнал как X(s), выходной сигнал сигма-дельта модулятора как Y(s), а шум квантования как E(s), мы получаем передаточную функцию АЦП: Y(s) = X(s)/(s+1) + E(s)s/(s+1) То есть, по сути, сигма-дельта модулятор представляет собой фильтр нижних частот (1/(s+1)) для полезного сигнала и фильтр верхних частот (s/(s+1)) для шума, причем оба фильтры, имеющие одинаковую частоту среза.

Шумы, сосредоточенные в высокочастотной области спектра, легко удаляются цифровым фильтром нижних частот, расположенным после модулятора.

Рис.

7. Явление «перемещения» шума в высокочастотную часть спектра.

Однако следует понимать, что это крайне упрощенное объяснение явления формирования шума в сигма-дельта АЦП.

Итак, главным преимуществом сигма-дельта АЦП является его высокая точность за счет чрезвычайно низкого уровня собственных шумов.

Однако для достижения высокой точности необходимо, чтобы частота среза цифрового фильтра была как можно ниже, во много раз меньше рабочей частоты сигма-дельта модулятора.

Поэтому сигма-дельта АЦП имеют низкую скорость преобразования.

Их можно использовать в аудиотехнике, но основное их применение — в промышленной автоматике для преобразования сигналов датчиков, в измерительных приборах и в других приложениях, где требуется высокая точность.

но высокая скорость не требуется.

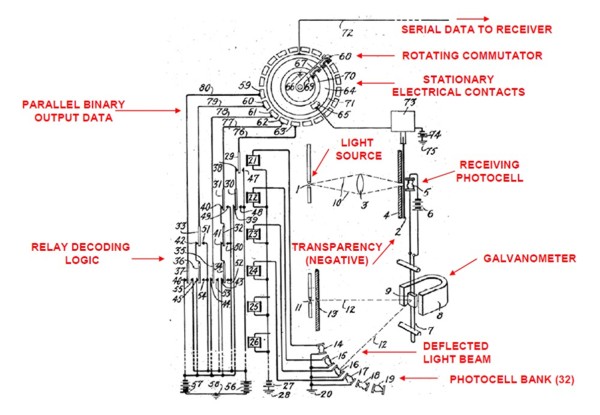

Немного истории Самым старым упоминанием АЦП в истории, вероятно, является патент Пола М.

Рейни «Факсимильная телеграфная система», патент США № 1608527, поданный 20 июля 1921 года и выданный 30 ноября 1926 года.

Устройство, изображенное в патенте, на самом деле представляет собой 5-ти АЦП прямого преобразования бит.

Рис.

8. Первый патент на АЦП.

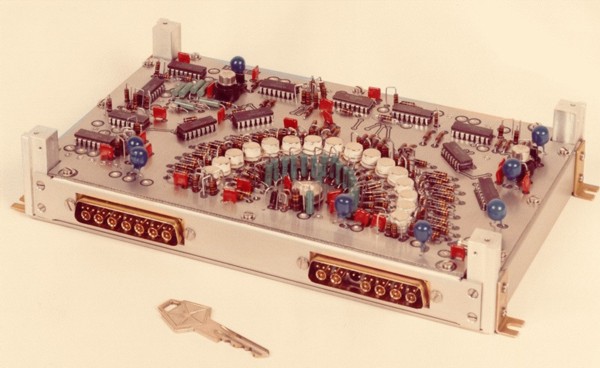

Рис.

9. АЦП прямого преобразования (1975 г.

) Представленное на рисунке устройство представляет собой АЦП прямого преобразования MOD-4100 производства компании Computer Labs, 1975 года выпуска, собранный с использованием дискретных компараторов.

Компараторов 16 (они расположены полукругом, чтобы уравнять задержку распространения сигнала на каждый компаратор), поэтому АЦП имеет разрядность всего 4 бита.

Скорость преобразования 100 MSPS, потребляемая мощность 14 Вт. На следующем рисунке показана расширенная версия АЦП прямого преобразования.

Рис.

10. АЦП прямого преобразования (1970 г.

).

VHS-630 1970 года, произведенный Computer Labs, содержал 64 компаратора, был 6-битным, 30 MSPS и потреблял 100 Вт (версия VHS-675 1975 года имела 75 MSPS и потребляла 130 Вт).

Литература В.

Кестер.

Архитектура АЦП I: Flash Converter. Аналоговые устройства, Учебное пособие по MT-020. www.analog.com/static/imported-files/tutorials/MT-020.pdf В.

Кестер.

Архитектура АЦП II: успешное приближение АЦП.

Analog Devices, Учебное пособие по MT-021. www.analog.com/static/imported-files/tutorials/MT-021.pdf В.

Кестер.

Архитектура АЦП III: основы сигма-дельта АЦП.

Analog Devices, Учебное пособие по MT-022. www.analog.com/static/imported-files/tutorials/MT-022.pdf В.

Кестер.

Архитектура АЦП IV: передовые концепции и приложения сигма-дельта АЦП.

Аналоговые устройства, Учебное пособие по MT-023. www.analog.com/static/imported-files/tutorials/MT-023.pdf Теги: #Электроника для начинающих #электроника #АЦП #начинающим

-

Отключение Сети Yota В Санкт-Петербурге

19 Oct, 24 -

Тайкаст #1

19 Oct, 24 -

Asp.net: Регистрация Javascript На Странице

19 Oct, 24